核心结论先行:

-

"代码顺序"

"执行顺序"

"观察顺序"。

-

x86 的强一致性( TSO )是"溺爱", ARM 的弱一致性(Relaxed)才是"现实"。

-

Go Runtime 源码 明确指出:Writer 没乱序,不代表其他线程观察到的也没乱序。这是 Data Race 的根源。

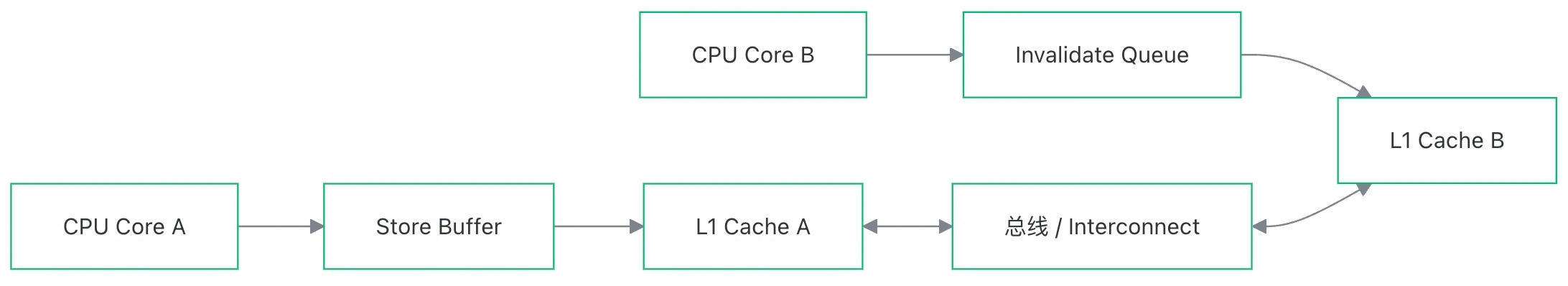

很多开发者认为并发问题的根源是 L1/L2 缓存不一致。

错! 根据 MESI 协议,Cache 之间是强一致的。真正的"罪魁祸首"是 CPU 为了掩盖 Cache 延迟而引入的两个 缓冲区:

-

Store Buffer(写缓冲):

-

Writer 侧的欺骗 :Writer 执行

x=1,为了不等待,直接扔进 Store Buffer 就继续跑下一行。 -

后果 :Writer 自己能看到

x=1,但其他核(Reader)根本不知道x变了。

-

-

Invalidate Queue(失效队列):

-

Reader 侧的敷衍 :Writer 发来消息说"

x变了,作废你的缓存!",Reader 为了忙流水线,把消息扔进队列暂时不处理,继续读旧的x。 -

后果:Reader 读到了旧数据,即使 Writer 已经发出了通知。

-

案例实证 1:单侧加锁的"薛定谔"变量

此案例展示了 单侧加锁(Writer 加锁,Reader 裸奔) 为何无法保证一致性。

Go

package main

import (

"fmt"

"runtime"

"sync"

"sync/atomic"

"testing"

"time"

)

var (

x int

y int

mu sync.Mutex

)

func TestAsymmetricLockConsistency(t *testing.T) {

runtime.GOMAXPROCS(runtime.NumCPU())

fmt.Println("🕵️♀️ 寻找单侧加锁下的乱序 (Observer Consistency Test)")

fmt.Println("目标:Reader 不加锁,能否看到 Lock 内部的 Y 先于 Lock 之前的 X 更新?")

fmt.Println("Writer: X=1 -> Lock -> Y=1 -> Unlock")

fmt.Println("Reader: if Y==1 && X==0 => 乱序!")

var detected int64 = 0

var ops int64 = 0

// 运行 5 秒

done := make(chan bool)

go func() {

time.Sleep(5 * time.Second)

close(done)

}()

var wg sync.WaitGroup

// Reader 协程

for i := 0; i < 4; i++ { // 多个 Reader 增加观测概率

wg.Add(1)

go func() {

defer wg.Done()

for {

select {

case <-done:

return

default:

// 关键点:Reader 不加锁

r1 := y // 先读 Y

r2 := x // 后读 X (内存序上,如果我们看到 Y=1,理论上 X 应该早就是 1 了)

// 插入屏障防止编译器把 r2 读操作优化到 r1 之前

// 在 Go 中很难显式控制,但我们可以通过依赖关系或 atomic Load 来尝试

// 这里我们用最原始的读,看看硬件行为

if r1 == 1 && r2 == 0 {

atomic.AddInt64(&detected, 1)

// fmt.Println("💥 抓到了!Y=1 但 X=0")

}

}

}

}()

}

// Writer 协程

wg.Add(1)

go func() {

defer wg.Done()

for {

select {

case <-done:

return

default:

atomic.AddInt64(&ops, 1)

// 重置

x = 0

y = 0

// 必须确保 Reader 此时读到的是 0, 0 吗?

// 其实很难同步,我们主要靠大量的随机碰撞。

// 这里的重置本身也存在竞态,但我们只关心 0 -> 1 的过程。

// 稍微停顿确保 Reader 有机会读到 0

for i := 0; i < 100; i++ {

runtime.Gosched()

}

// --- 核心动作 ---

x = 1 // Store X

mu.Lock() // Barrier?

y = 1 // Store Y

mu.Unlock() // Release Barrier

// ----------------

}

}

}()

wg.Wait()

fmt.Printf("测试结束。总操作数: %d, 捕捉到乱序次数: %d\n", ops, detected)

if detected > 0 {

fmt.Println("结论:单侧加锁无法保证顺序一致性!Reader 确实看到了乱序。")

} else {

fmt.Println("结论:未捕捉到。可能是 x86 TSO 太强,或者 Lock 的实现使用了全屏障 (MFENCE)。")

}

}为什么会乱序?(x86 vs Mac M系列)

|-------------------------|----------|-----------------------------------------------------------------------------------------------|

| 平台 | 现象 | 原因分析 |

| x86 (Intel) | 通常没事 | 硬件强行保证 Load-Load 有序 。即使 Reader 没加锁,CPU 也会乖乖先读 y 再读 x。如果 y 是新值,x 必然也是新值。 |

| Mac ( ARM ) | 必挂 | 硬件允许 Load-Load 乱序 。Reader 的 CPU 发现 x 地址就在手边,y 还在远端,于是先读了 x (0) ,再读的 y (1)。逻辑崩溃。 |

本质:双向奔赴协议

mu.Unlock() 只是把信(数据)寄出去了。

如果 Reader 不加锁(mu.Lock()),就相当于他不肯去信箱取信 ,甚至倒着读信。单侧加锁无法约束 Reader 的硬件行为。

案例实证 2:Map 的 Copy-On-Write 乱序

此案例展示了 指针 赋值与对象初始化 的重排风险。

Go

// 全局变量

var globalConf map[int]int

var updateLocker = sync.Mutex{}

func TestMapCowPanic(t *testing.T) {

// 开启最大核心数

runtime.GOMAXPROCS(runtime.NumCPU())

fmt.Println("🌪️ 极限测试:尝试复现 Map 初始化过程中的指令重排导致的 Panic")

fmt.Println("原理:如果指针赋值被重排到了 map 赋值中间,就会发生并发读写")

var wg sync.WaitGroup

// 运行时间控制

done := make(chan bool)

go func() {

time.Sleep(60 * time.Second)

close(done)

}()

// Reader 协程群:疯狂读取

// 如果发生了重排,Reader 拿到 map 时,Writer 可能还在往里面写东西

for i := 0; i < 20; i++ {

wg.Add(1)

go func() {

defer wg.Done()

for {

select {

case <-done:

return

default:

m := globalConf

if m != nil {

// 尝试读取,如果 Writer 还在写,这里就是并发读写 -> Panic

// 读多个 key 增加碰撞概率

_ = m[0]

_ = m[100]

_ = m[1000]

_ = m[5000]

}

}

}

}()

}

// Writer 协程:不断创建大 Map

wg.Add(1)

go func() {

defer wg.Done()

for {

select {

case <-done:

return

default:

// 创建一个新 Map

newMap := make(map[int]int)

// 写入大量数据

// 期望:CPU 可能会把下面的 `globalConf = newMap` 重排到这个循环中间

// 虽然 Go 编译器通常不会这么做,但这是唯一的复现机会

for k := 0; k < 10000; k++ {

newMap[k] = k

}

// 发布指针

globalConf = newMap

// 稍微让出一点时间给 Reader 消化

// runtime.Gosched()

}

}

}()

wg.Wait()

fmt.Println("✅ 测试结束。如果没 Panic,说明 Go 的运行时/编译器屏障很强。")

}在 Go 内存模型允许的情况下,或者在弱一致性硬件(ARM)上,Reader 可能会观察到这样的顺序:

-

看到动作 B 完成 :Reader 读到了

globalConf已经指向了newMap的地址(非 nil)。 -

看到动作 A 未完成 :Reader 去访问

newMap内部的数据结构(bucket, hmap),却发现内存里是一堆零值或垃圾数据。 -

结果:并发读写 Panic,或者访问了损坏的内存结构。

为什么? 因为 newMap 的初始化写操作还在 Writer 的 Store Buffer 里排队,而 globalConf 的指针赋值操作可能因为刚好在 Cache Line 里而被优先处理(或者被 Reader 优先观测到)。

源码铁证:Go Runtime 的"免责声明"

Go Runtime 源码注释明确区分了 "执行顺序" 和 "观察顺序"。

引用自 Go 源码 runtime/internal/atomic/types.go (及相关架构实现):

- LoadAcquire (对应 Reader)

Go

// LoadAcquire is a partially unsynchronized version of Load...

// Other threads may observe operations that precede this operation to

// occur after it...

// 译:其他线程可能会看到"本该在 Load 之前发生的操作"被拖到了"Load 之后"才发生。

// 但它保证:本线程 Load 之后的操作,绝对不会跑到 Load 之前去。(单向屏障)- StoreRelease (对应 Writer)

Go

// StoreRelease is a partially unsynchronized version of Store...

// Other threads may observe operations that occur after this operation to

// precede it...

// 译:其他线程可能会看到"本该在 Store 之后发生的操作"跑到了"Store 之前"。

// 但它保证:本线程 Store 之前的所有操作,绝对不会跑到 Store 之后去。(确保 Store 之前的数据都刷出去了)Other threads may observe...

这句话极其关键:

"Writer 没重排,但别人能看到像重排一样。"

-

Writer 说 :"我发誓,我是先写了

Key,再把Map指针给你的!"(程序顺序 Program Order) -

Reader 说 :"由于 总线延迟 、 Store Buffer 、以及你自己发信的顺序(Store-Store 乱序),我确实是先收到了 指针 ,后收到了 Key。"(观察顺序 Observation Order)

Go Runtime 的注释就是在告诉你:除非你用正确的 同步原语 (Lock/Atomic),否则不要假设别人的眼睛(观察顺序)和你的一样。

总结与最佳实践

-

忘掉 x86 :不要在 x86 机器上测试并发正确性,那是在温室里测试抗风能力。去 ARM (Mac M系列) 上测!

-

可见性

实时性:可见性是指"最终能看到"且"顺序正确"。硬件层面的延迟是微秒级的,但对 CPU 来说就是万年。

-

原子操作的三层语义:

-

Relaxed (Go

atomic.Load/Store): 只保证那一个变量读写是原子的,不保证前后指令顺序。(极度危险,仅用于计数器) -

Acquire/Release (Go Mutex, Channel): 保证半个世界的顺序。

-

Sequential Consistency (C++

memory_order_seq_cst) : 保证全宇宙的绝对顺序(Go 的atomic在某些实现上接近这个,但不要依赖)。

-

-

最终建议:

-

有 Data Race 就是 Bug,无论它在 x86 上跑得多么欢。

-

单侧加锁 = 没加锁(对于可见性而言)。

-

初始化后发布 :如果是类似 Map 的例子,请使用

atomic.Value或者sync.Once,它们内部包含了正确的屏障指令。

-

附录:CPU与可见性

x86 vs M系列:x86 像一个"保姆",硬件帮你处理了大部分顺序问题(除了 Store-Load),所以 Store Buffer 经常导致可见性问题。Mac M 系列(ARM)像一个"赛车手",为了快,它允许读写随意乱序,除非你明确下指令(屏障)让它慢下来。

M系列更弱?:一致性模型更弱,但这对性能是好事(CPU 束缚更少)。对程序员来说,意味着并发代码必须写得更严谨(必须正确使用 Lock/Atomic/Volatile)。

可见性本质 :不是缓存导致的,而是为了掩盖缓存延迟引入的 Store Buffer (导致写了别人看不见)和 Invalidate Queue(导致别人通知了你却装作没看见)造成的。

核心差异:TSO vs Relaxed

x86:强一致性 (TSO - Total Store Order)

x86 架构(Intel/AMD)采用的是 TSO 模型。它非常"溺爱"程序员,硬件层面做了很多排序保证:

-

写写有序:Store A 后 Store B,所有核心看到的顺序一定先 A 后 B。

-

读读有序:Load A 后 Load B,顺序不会乱。

-

读写有序:Load A 后 Store B,顺序不会乱。

-

唯一允许乱序 :Store-Load。即前面的写操作还没刷入主存,后面的读操作就已经从缓存/内存读了(因为有 Store Buffer 存在)。

这意味着: 在 x86 上写并发代码,很多时候即使你忘记加内存屏障(Memory Barrier),代码也能跑对,因为硬件帮你保证了大部分顺序。

Mac M 系列 (ARM):弱一致性 (Relaxed/Weak Memory Model)

Mac 的 M 系列芯片基于 ARM 架构,采用 弱内存模型。它追求极致的能效和性能,因此硬件"很懒":

-

几乎所有顺序都可能被打乱。

-

Store A 后 Store B,另一个线程可能先看到 B,再看到 A。

-

Load 和 Store 之间也可以随意乱序。

这意味着: 在 M 系列芯片上,必须显式地使用内存屏障(Memory Barrier)指令(如 DMB 指令)来告诉 CPU:"这里不能乱序"。如果代码里不仅没有锁,也没用 volatile 或原子变量(Atomic),在 x86 上侥幸能跑通的代码,在 M1/M2/M3 上极大概率会崩溃或死锁。

线程屏障 (Barrier/Fence) 的差别

由于内存模型的不同,两者在屏障指令的开销和需求上完全不同:

|-------------------|------------------------------------|-------------------------------------------|

| 特性 | x86 (Intel/AMD) | Mac M 系列 (ARM) |

| 写-写重排 | 不允许 (硬件保证有序) | 允许 (需要写屏障 StoreStore Fence) |

| 读-读重排 | 不允许 (硬件保证有序) | 允许 (需要读屏障 LoadLoad Fence) |

| 屏障指令 | MFENCE (全屏障), SFENCE, LFENCE | DMB (Data Memory Barrier), DSB, ISB |

| Java volatile | 写操作编译为 Lock 前缀指令 (类似全屏障) | 写操作编译为 dmb ish (全屏障) |

| 开销 | 屏障指令较重,但平时不需要太多屏障 | 屏障指令相对轻量,但需要更频繁地使用 |

为什么说 M 系列"更弱"?

这里的"弱"是指约束弱(Weakly Ordered)。CPU 可以在执行指令时更自由地重新排列读写顺序,从而利用流水线榨干性能。但这把复杂性甩给了软件(编译器和开发者)。

CPU 可见性的本质:不仅是缓存,更是缓冲区

很多人认为可见性问题(一个线程写,另一个线程看不见)是因为 L1/L2 缓存(Cache) 造成的。

这是一个常见的误区。

根据 MESI 缓存一致性协议 ,L1/L2 缓存之间其实是强一致的。如果 Core A 改了 Cache Line,Core B 对应的 Cache Line 会立刻失效(Invalidate)。缓存本身是有一致性保证的。

真正的"罪魁祸首"是:Store Buffer 和 Invalidate Queue。

本质图解:

-

Store Buffer (写缓冲):

-

CPU 觉得写内存(甚至写 L1 Cache)太慢了。

-

当你执行

x = 1时,Core A 不会等数据真的写入 Cache,而是直接扔进 Store Buffer,然后继续执行下一条指令。 -

后果 :Core A 自己能看到

x=1(Store Forwarding),但 Core B 此时完全看不到!对于 Core B,x还是 0。这就是不可见。

-

-

Invalidate Queue (失效队列):

-

当 Core A 真的要把

x=1写回 Cache 时,它通过 MESI 协议发消息给 Core B:"把你的 x 缓存作废(Invalidate)"。 -

Core B 收到消息,觉得处理这个"作废"动作太慢,于是把消息扔进 Invalidate Queue,回了个"收到",然后继续干活。

-

后果 :Core B 以为自己处理了,其实它的 Cache 里

x还是旧值。等它真的处理队列时,才发现x变了。

-

屏障做了什么?

当你加了内存屏障(比如 Java 的 volatile 写,或 C++ 的 atomic):

-

写屏障 (Store Fence) :强制 CPU 把 Store Buffer 里的所有数据立刻刷入 Cache(并触发 MESI 协议),直到刷完才能执行后面的指令。

-

读屏障 (Load Fence):强制 CPU 处理完 Invalidate Queue 里的所有失效消息,确保自己 Cache 里的数据是最新的,才能读取数据。