目录

[1. CAN 总线传输协议概述](#1. CAN 总线传输协议概述)

[1.1 系统组成与节点类型](#1.1 系统组成与节点类型)

[1.2 物理层架构](#1.2 物理层架构)

[2. 数据传输方式与帧格式](#2. 数据传输方式与帧格式)

[2.1 编码与逻辑位](#2.1 编码与逻辑位)

[2.2 帧格式 (Standard Frame)](#2.2 帧格式 (Standard Frame))

[3. CAN 总线关键特性](#3. CAN 总线关键特性)

[4.1FPGA实现CAN协议+收发器芯片 (TPT1051)完成电平转换](#4.1FPGA实现CAN协议+收发器芯片 (TPT1051)完成电平转换)

[4.2 FPGA+控制器完成协议+收发器完成电平转换](#4.2 FPGA+控制器完成协议+收发器完成电平转换)

[5. 参考资料](#5. 参考资料)

前言

在掌握了 1553B、RS422、LVDS、SpaceWire基础上,本文对CAN (Controller Area Network) 总线进行解析。我们将深入探讨其独特的非破坏性仲裁机制、物理特性以及在 FPGA 设计中常用的协议实现方案。

1. CAN 总线传输协议概述

CAN 总线 全称为"控制器局域网络",由德国 Bosch 公司于 20 世纪 80 年代开发。虽然起步于汽车工业,但因其极高的鲁棒性、实时性 和低成本,它已成为卫星载荷管理、分布式传感器网络及微小卫星(CubeSat)的标准通信协议。

1.1 系统组成与节点类型

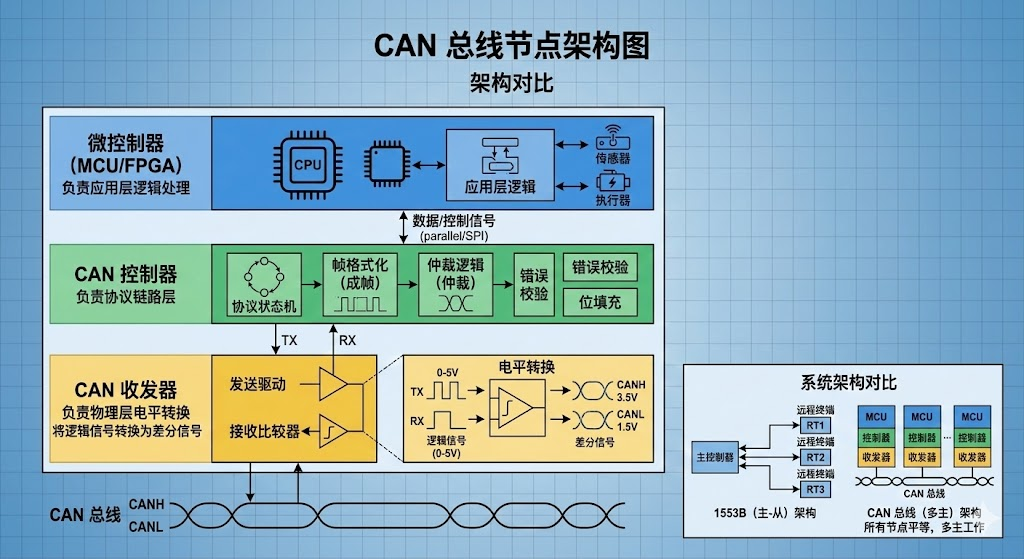

不同于 1553B 的"主-从"严密等级制,CAN 总线采用多主(Multi-Master)架构。系统中的节点在法律地位上是平等的,每个节点主要由三部分组成:

-

微控制器 (MCU/FPGA):负责应用层逻辑处理。

-

CAN 控制器:负责协议链路层(如成帧、仲裁、错误校验、位填充),该控制器可以用专门控制器芯片,也可以自己在FPGA写CAN协议实现。

-

CAN 收发器:负责物理层电平转换(将逻辑信号转换为差分信号)。

该组成示意图如下:

图 1-1 CAN总线节点架构

图 1-1 CAN总线节点架构

1.2 物理层架构

CAN 采用直线拓扑结构,利用屏蔽双绞线传输信号。

-

差分信号:包含 CAN_H 和 CAN_L 两根线。接收端通过两线间的电压差来识别逻辑状态。

-

终端匹配 :总线的最远两端必须各连接一个

的终端电阻,用于消除高频信号反射,确保波形完整。

-

线网逻辑 :遵循"显性电平(Dominant)覆盖隐性电平(Recessive)"的原则。在逻辑上,显性对应"0",隐性对应"1"。只要有一个节点发"0",全总线即为"0"。

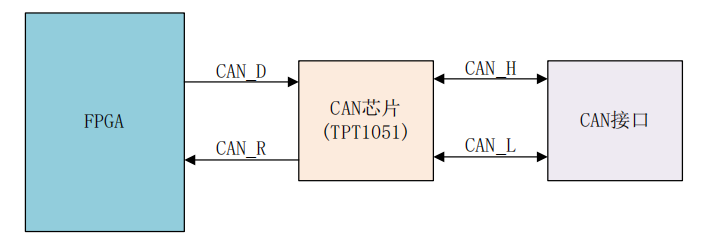

在FPGA中的连接方式如图1-2所示。

图 1-2 FPGA实现CAN协议+收发器芯片 (TPT1051)完成电平转换方案连接示意图

图 1-2 FPGA实现CAN协议+收发器芯片 (TPT1051)完成电平转换方案连接示意图

2. 数据传输方式与帧格式

2.1 编码与逻辑位

CAN 总线采用 NRZ(Non-Return to Zero)编码。

-

位填充机制 (Bit Stuffing):为了防止长串相同电平导致时钟不同步,当协议检测到连续 5 个相同位时,会自动插入一个相反的位。接收端会自动剔除该位。

-

线与仲裁:这是 CAN 的核心灵魂。当多个节点同时发送数据时,它们会一边发一边听。如果自己发的是"1"(隐性)却听到总线是"0"(显性),说明有更高优先级的节点在说话,此时该节点自动退出竞争。

2.2 帧格式 (Standard Frame)

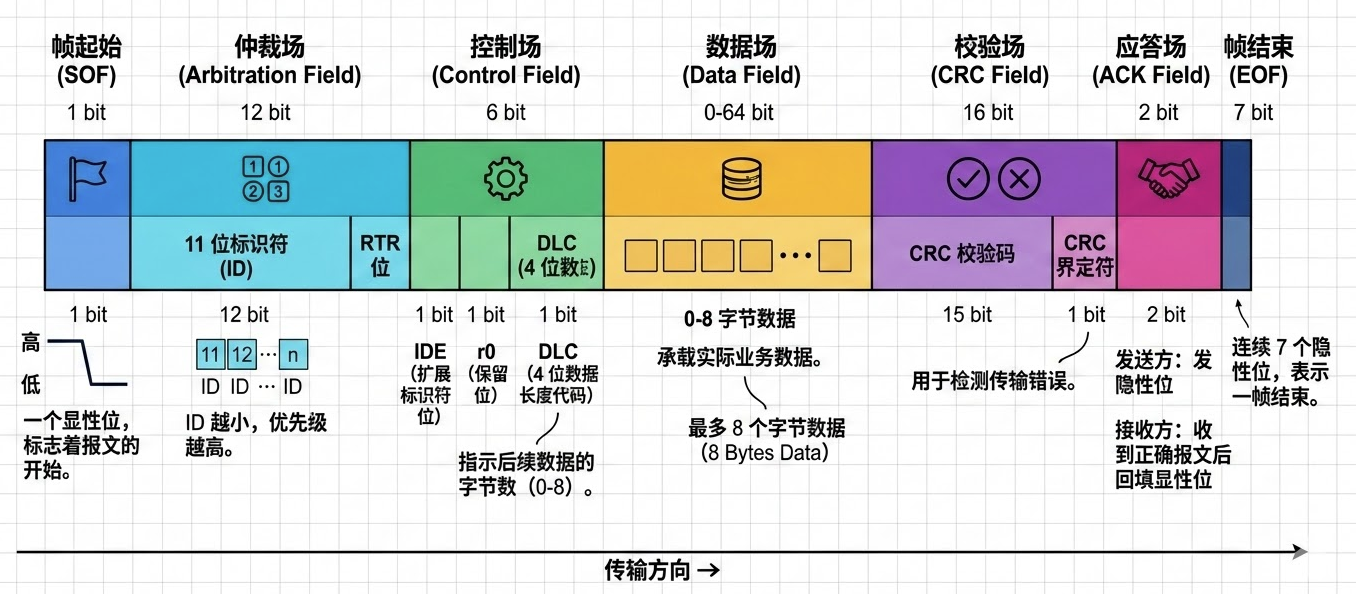

标准的 CAN 2.0A 帧如图2-1所示。

图2-1 CAN 2.0 标准数据帧结构

图2-1 CAN 2.0 标准数据帧结构

其固定由以下几部分组成:

-

帧起始 (SOF, 1 bit):一个显性位,标志着报文的开始。

-

仲裁场 (Arbitration Field, 12 bit) :包含 11 位标识符 (ID) 和 RTR 位(远程发送请求位)。ID 越小,优先级越高。

-

控制场 (Control Field, 6 bit) :包含 IDE(扩展标识符位)、r0(保留位)和 DLC(4 位数据长度代码),指示后续数据的字节数。

-

数据场 (Data Field, 0-64 bit):承载实际业务数据,最多 8 个字节。

-

校验场 (CRC Field, 16 bit):包含 15 位校验码和 1 位界定符,用于检测传输错误。

-

应答场 (ACK Field, 2 bit):发送方发隐性位,接收方收到正确报文后回填显性位。

-

帧结束 (EOF, 7 bit):连续 7 个隐性位,表示一帧结束。

3. CAN 总线关键特性

-

非破坏性逐位仲裁:这是 CAN 最显著的特点。即使发生冲突,高优先级报文也能毫发无损地继续传输,不会像以太网那样因冲突而导致带宽归零。

-

强大的错误处理机制 :CAN 具备五种错误检测方式(位、格式、CRC、应答、填充)。如果一个节点频繁出错,它会从"主动错误状态"降级为"被动错误状态",严重时甚至会自我锁定(Bus Off),确保不影响整条总线的安全。

-

配置灵活:节点加入或退出总线不需要修改软件设置,具有极佳的即插即用特性,适合分布式传感器部署。

4.FPGA实现CAN方案

4.1FPGA实现CAN协议+收发器芯片 (TPT1051)完成电平转换

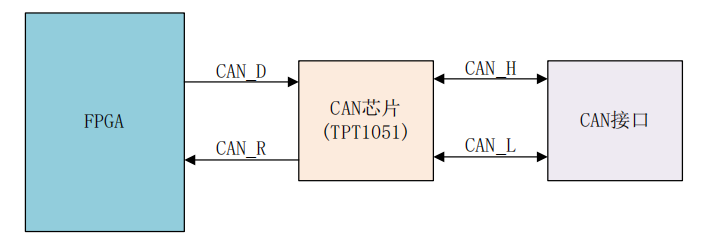

在 FPGA 内部已经写好了CAN 控制器的 Verilog 代码(即逻辑层),然后通过 TPT1051收发器转换电平。

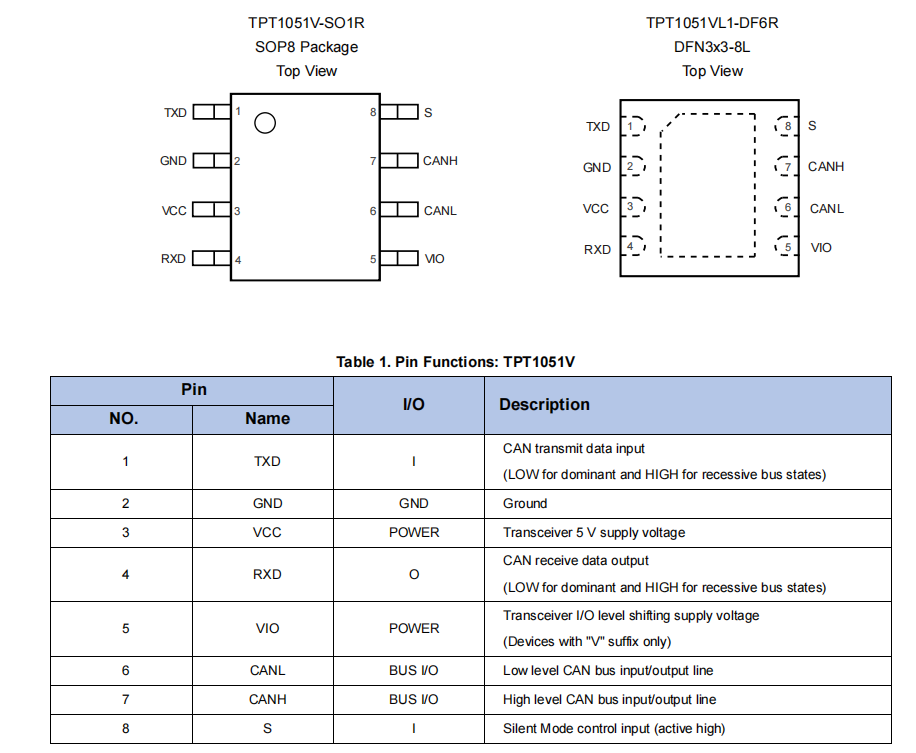

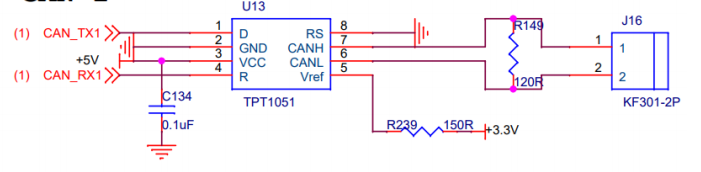

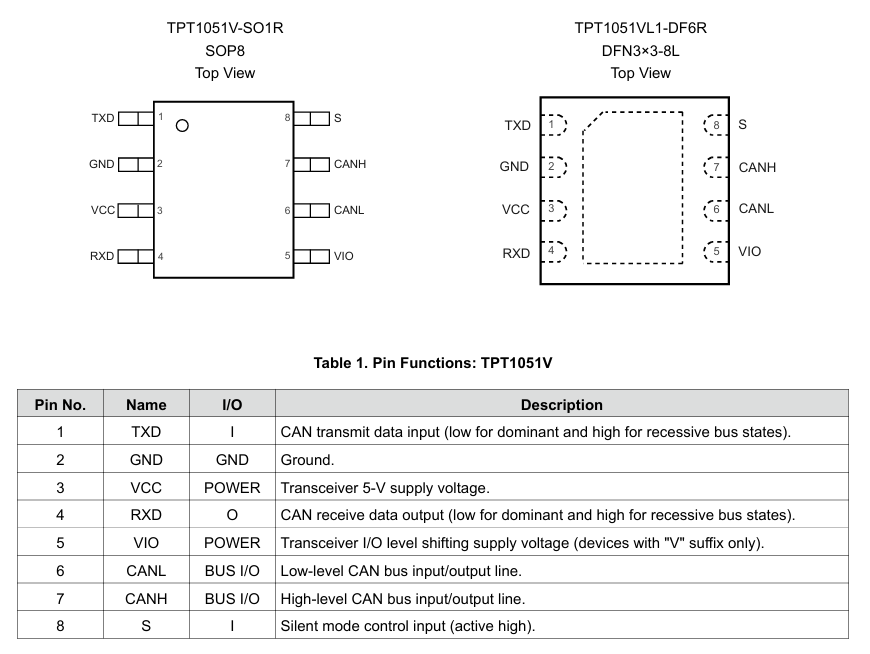

在该方案中 FPGA 内部逻辑是"大脑", TPT1051 就是"强壮的手臂"。它是一款高性能、高速的 CAN 收发器,专门负责将 FPGA 的逻辑电平转换为总线上的差分信号。其引脚图如图4-1所示。电路原理图如图4-2所示。

图 4-1 TPT1051引脚图

图 4-1 TPT1051引脚图

图 4-2 TPT1051电路原理图

图 4-2 TPT1051电路原理图

该芯片的特性如下:

-

速率支持 :全面支持 CAN FD ,在高度加载的网络中数据速率可达 5 Mbps。

-

低摆幅与低功耗:

-

典型循环延迟仅为 110 ns。

-

具有极佳的电磁兼容性(EMC)和低电磁发射(EME)。

-

-

电压与接口:

-

VCC:5V 供电。

-

VIO 引脚 (仅 V 后缀版本) :支持 2.8V 到 5.5V 的 MCU 接口,无需额外的电平转换芯片即可直接连接 FPGA 或低电压 MCU。

-

-

保护功能:

-

总线耐压 :标准版为 ±42V,H 版本高达 ±70V。

-

ESD 防护:接触放电可达 ±15kV 以上。

-

静默模式 (Silent Mode):支持监听模式,不向总线发送信号。

-

而TPT1051V多加了VIO引脚如图4-3所示,具备以下功能:

图 4-3 TPT1051V引脚图

图 4-3 TPT1051V引脚图

- 逻辑接口 (TXD/RXD) 与 VIO 电平自适应 : 与传统的 5V 收发器不同,TPT1051V 专门配备了 VIO 引脚。这使得它能直接与 2.8V、3.3V 或 5V 逻辑电平的 FPGA 直接相连,无需额外的电平转换芯片,极大地简化了 PCB 布线并节省了空间。

该方案架构如图4-4所示。

图 4-4 FPGA实现CAN协议+收发器芯片 (TPT1051)完成电平转换方案连接示意图

图 4-4 FPGA实现CAN协议+收发器芯片 (TPT1051)完成电平转换方案连接示意图

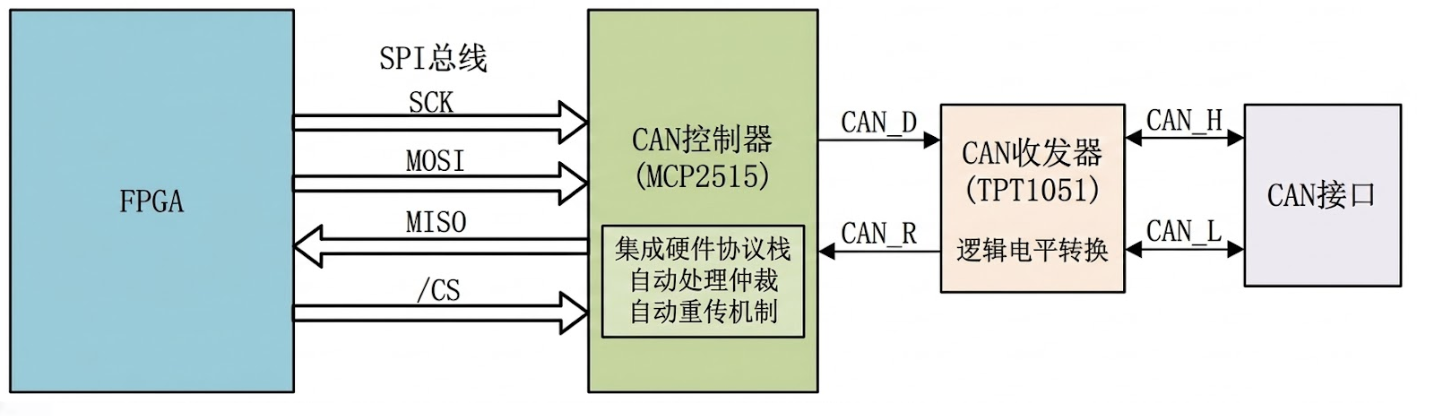

4.2 FPGA+控制器完成协议+收发器完成电平转换

该方案利用 控制器如MCP2515的硬件集成协议栈的特性,由其自动处理 CAN 总线的仲裁与重传机制。FPGA 仅需通过 SPI 总线驱动控制器,配合收发器即可完成通信。

核心优势: 屏蔽了底层协议的复杂性,大幅减少了 FPGA 逻辑资源的消耗,简化了系统设计流程。

该方案架构如图4-5所示。

图 4-5 基于MCP2515硬件协议栈的FPGACAN通信架构

图 4-5 基于MCP2515硬件协议栈的FPGACAN通信架构

5. 参考资料

(1)《CAN 总线规范 2.0 版》------ Bosch 官方文档 can20.pdf

(2)《MCP2515 独立 CAN 控制器数据手册》MCP2515 Stand-Alone CAN Controller with SPI Interface Data Sheet

以上就是关于 CAN 总线的技术笔记。