本文声明:内容来源于网络,进行整合/再创作;部分内容由AI辅助生成。

ARMv8 异常概述

在嵌入式系统中,异常(Exception) 是一个统称,指任何导致处理器暂停当前正常程序,转而去处理特定事件的情况。

虽然在实际应用中常统称为"异常",但根据事件来源的不同,它们分为两类:

|---------------------|-----------------------------------|--------------------------------|

| | 异常 (Exception) (狭义,内部源) | 中断 (Interrupt) (外部源) |

| 触发来源 | 处理器内部 | 处理器外部 |

| 触发时机 (本质区别) | 指令执行时出错 / 非法操作 | 外设发出的"信号"或"请求" |

| 管理机制 | 由处理器内核直接检测 | 通常由中断控制器统一管理、上报CPU |

| 可屏蔽性 | 通常不可屏蔽(除非关闭整个中断系统,但致命错误仍需处理) | 大部分可屏蔽(通过中断控制器使能 / 屏蔽中断请求) |

| 典型例子 | 非法指令执行 地址访问错误 触发特定状态(如系统调用) | 按键按下 传感器数据到达 定时器超时 |

尽管来源不同,但在嵌入式开发中,两者都会打断主程序,进入特定的处理器运行模式。因此,实际中往严格区分异常与中断,统称为"异常处理"。

为了确保系统的实时性、程序执行的稳定性,ARM 处理器设计了完整的异常处理机制:

- 打断正常流程:一旦检测到异常或中断,CPU会立即暂停正在执行的程序。

- 切换处理模式:CPU自动进入特定的异常处理模式。

- 执行处理程序:跳转到预设的地址,运行对应的异常处理程序。

- 恢复执行:处理完成后,CPU返回到原程序继续执行。

ARMv8 异常级别

ARMv8架构的处理器支持两种执行状态:AArch32和AArch64,且ARMv8系列的处理器在不同的执行状态下使用不同的异常处理系统。AArch32执行状态的主要目的是向下兼容ARMv7架构。

AArch32下的特权级别

在AArch32执行状态下,内核工作模式(也称处理器运行模式)可以在特权软件控制下更改,或在发生异常时自动更改。当发生异常时,内核保存当前执行状态和返回地址,进入对应的异常模式,可以选择禁用硬件中断。

AArch32处理器运行模式简介与特权级别

|--------|-------------------------------------------------------------|----------|----------------------------------|

| 模式 | 功能 | 安全状态 | 特权级别PL (Privilege Level) |

| USR | 大多数应用程序运行的非特权模式 | 安全和非安全 | PL0 |

| FIQ | 进入FIQ中断异常 | 安全和非安全 | PL1 |

| IRQ | 进入IRQ中断异常 | 安全和非安全 | PL1 |

| SVC | 在复位或软中断指令进入SVC模式 | 安全和非安全 | PL1 |

| MON | 当执行SMC指令(安全监视器调用)或处理器发生异常时输入,可将其配置为安全处理。支持在安全状态和非安全状态之间进行切换 | 安全 | PL1 |

| ABT | 进入内存访问异常 | 安全和非安全 | PL1 |

| UND | 在执行未定义的指令时进入 | 安全和非安全 | PL1 |

| SYS | 特权模式,与用户模式共享寄存器 | 安全和非安全 | PL1 |

| HYP | 由Hypervisor调用和Hyp Trap异常输入 | 非安全 | PL2 |

应用程序在最低级别的特权(PL0,无特权)下运行。操作系统运行在PL1,系统管理程序在System上运行,虚拟化扩展在PL2上运行。安全监视器作为在安全与非安全(正常)之间切换的网关,也作用于PL1。

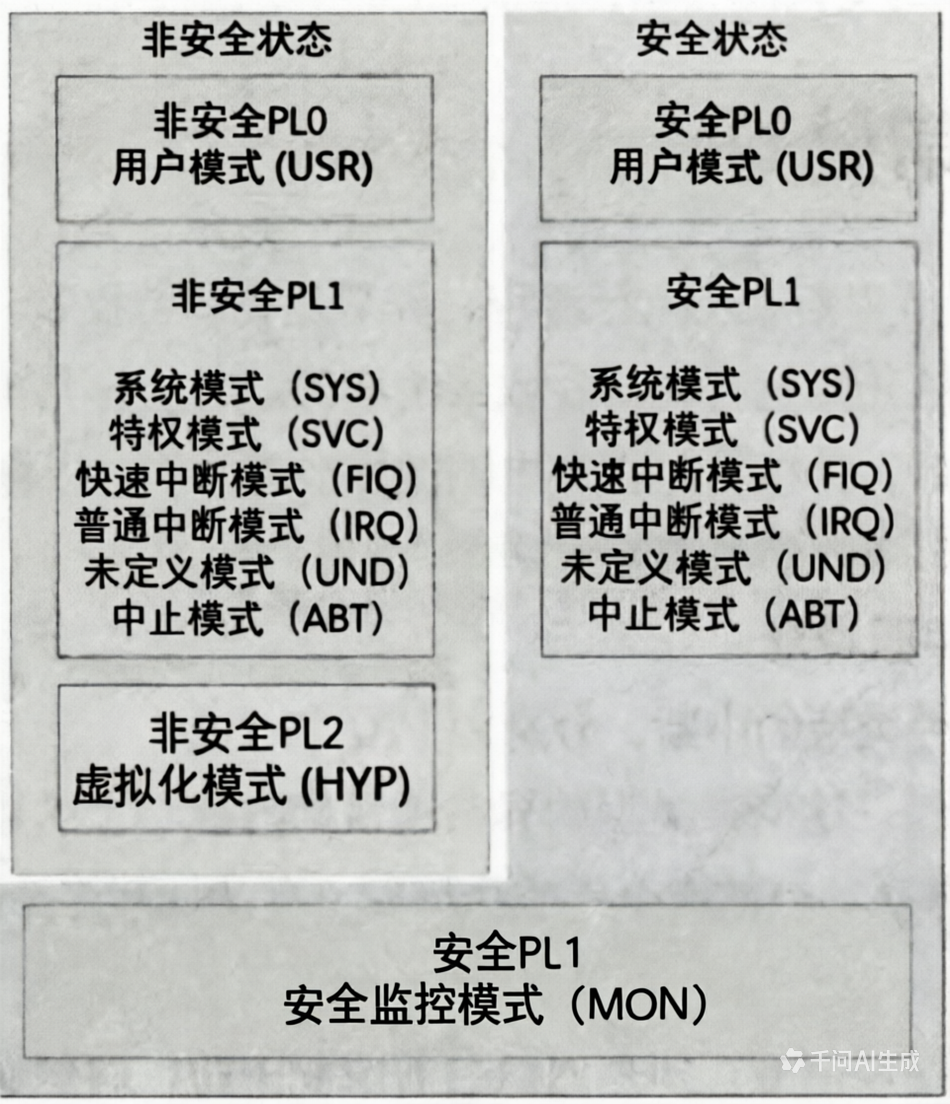

AArch32 特权级别

AArch32 特权级别

AArch64下的异常级别

在AArch64中,处理器运行模式映射到异常级别,如下图所示。与ARMv7中一样,当发生异常时,处理器将更改为支持异常处理对应的异常级别(模式)。

AArch64 异常级别

|------------------|--------------------|-------------------|-----------------------|

| 图中层次 | 正常状态 | 安全状态 | 对应异常级别 |

| 应用层 / 安全固件 | 应用程序 | 安全固件 / 可信应用 | EL0(用户态,无特权) |

| 客户操作系统层 / 安全操作系统 | 客户操作系统 (如 Linux) | 安全操作系统 (如 TEE OS) | EL1(内核态,特权) |

| 虚拟化层 (HYP) | Hypervisor (如 KVM) | 不存在 | EL2 (虚拟化态,仅在正常世界) |

| 安全监控层 (MON) | 安全监控器 | 安全监控器 | EL3 (最高特权,负责世界切换) |

可以看到,ARMv8-A架构有4个异常级别。处理器执行只能通过接收或返回异常来在异常级别之间进行切换,当处理器从更高的异常级别切换到更低的异常级别时,执行状态可以保持不变。

异常级别之间的运转遵循以下规则:

①切换到更高的异常级别,例如从EL0 → EL1,表示提高了软件执行特权。

②不能将异常切换到较低的异常级别。(异常进入是为了处理问题,必须获得更高的权限,所以只能 "往上走"。)

③若在EL0没有进行异常处理,则必须在更高的异常级别进行。

④异常会导致程序流的更改,根据异常向量表,进入到高于EL0的异常级别,执行异常处理程序。以下特殊情况除外:中断、内存系统中止、未定义指令、非特权软件对操作系统进行系统调用、保护监视程序或管理程序陷阱。

⑤异常处理结束并返回到之前的异常级别是通过执行异常返回指令(Exception Return,ERET)指令来实现的。

⑥从异常返回可以保持在相同的异常级别,也可以进入更低的异常级别,即软件执行特权保持不变或降低,但它不能进入到更高的异常级别。(异常返回是问题处理完毕,要恢复到原来的执行环境,所以可以 "往下走"。)

⑦安全状态会随着异常级别的变化而变化,但从EL3恢复到非安全状态时除外。