目录

-

- [1. 时钟源:心跳的"起搏器"](#1. 时钟源:心跳的“起搏器”)

-

- [1.1 外部时钟源------高精度、高稳定性](#1.1 外部时钟源——高精度、高稳定性)

- [1.2 内部时钟源------低成本、快速启动](#1.2 内部时钟源——低成本、快速启动)

- [2. 时钟树:从源头到终端的"血管网络"](#2. 时钟树:从源头到终端的“血管网络”)

-

- [2.1 系统时钟 SYSCLK------心脏的"主泵"](#2.1 系统时钟 SYSCLK——心脏的“主泵”)

- [2.2 AHB总线时钟 HCLK------高速"动脉"](#2.2 AHB总线时钟 HCLK——高速“动脉”)

- [2.3 APB总线时钟 PCLK------外设的"毛细血管"](#2.3 APB总线时钟 PCLK——外设的“毛细血管”)

- [3. 外设时钟门控------省电的"阀门"](#3. 外设时钟门控——省电的“阀门”)

- [4. 时钟安全系统------心跳的"监护仪"](#4. 时钟安全系统——心跳的“监护仪”)

- [5. 低功耗模式下的时钟策略](#5. 低功耗模式下的时钟策略)

- [6. 实战:时钟配置示例](#6. 实战:时钟配置示例)

- [7. 总结:时钟是系统的"节拍器"](#7. 总结:时钟是系统的“节拍器”)

如果说电源是MCU的"血液",那么时钟就是它的"心跳"。没有时钟,所有的逻辑电路都处于静止状态,CPU无法取指执行,外设无法收发数据------整个芯片就像被按下了暂停键。

这一讲,我们将深入MCU的时钟系统,看看这个"心跳"是如何产生、分配和控制的。理解时钟树,是掌握低功耗设计、外设配置以及系统稳定性的关键。

1. 时钟源:心跳的"起搏器"

MCU需要时钟源来产生稳定的振荡信号。常见的时钟源分为两类:

1.1 外部时钟源------高精度、高稳定性

| 类型 | 英文 | 特点 | 典型频率 |

|---|---|---|---|

| 外部高速晶振 | HSE | 精度高(几十ppm),启动慢,成本稍高 | 4MHz - 48MHz |

| 外部低速晶振 | LSE | 用于RTC(实时时钟),超低功耗 | 32.768kHz |

| 外部时钟输入 | --- | 由外部有源振荡器直接提供,精度由外部决定 | 任意频率 |

为什么低速晶振偏偏选32.768kHz?因为 (2^{15} = 32768),用15位计数器可以轻松产生1秒的时钟,非常适合RTC应用。

1.2 内部时钟源------低成本、快速启动

| 类型 | 英文 | 特点 | 典型频率 |

|---|---|---|---|

| 内部高速RC振荡器 | HSI | 启动快(微秒级),精度较低(1%左右) | 8MHz、16MHz等 |

| 内部低速RC振荡器 | LSI | 超低功耗,用于独立看门狗(IWDG)、RTC备用 | 约32kHz - 40kHz |

内部RC振荡器的精度受温度和电压影响较大,但胜在无需外部元件、上电即振,适合对时序要求不高的场景。

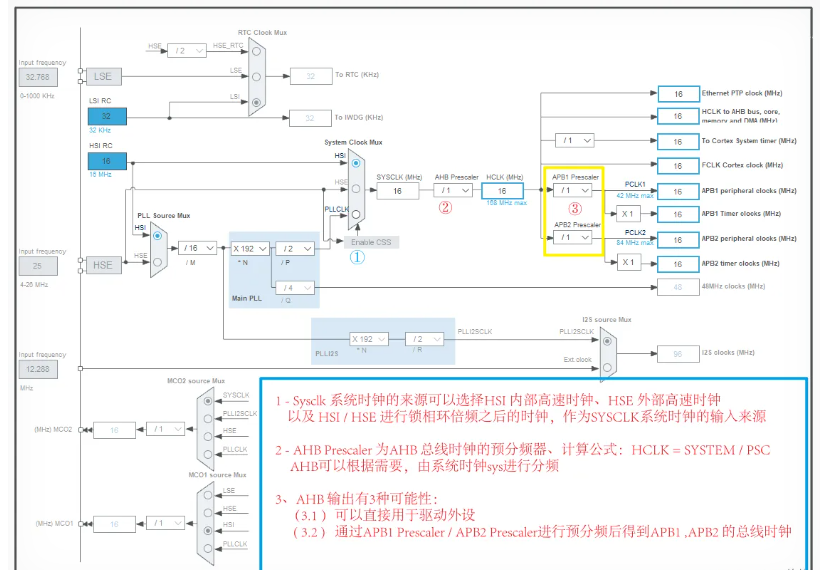

2. 时钟树:从源头到终端的"血管网络"

时钟源产生的信号并不会直接供给所有模块。它们会经过一系列选择器、分频器、倍频器 ,最终形成不同频率的时钟,供应给CPU、总线、外设。这个网络就是时钟树。

以典型的STM32F1系列时钟树为例,我们可以看到清晰的层次:

2.1 系统时钟 SYSCLK------心脏的"主泵"

系统时钟是整个MCU的最高频时钟源,它可以是:

- HSI:内部高速RC,上电默认

- HSE:外部高速晶振

- PLLCLK:锁相环输出,通常用于倍频到更高频率(如72MHz)

在复位后,MCU默认使用HSI(通常8MHz)作为系统时钟,以保证快速启动。用户需要在SystemInit()中配置PLL和时钟源,将系统时钟切换到目标频率。

2.2 AHB总线时钟 HCLK------高速"动脉"

HCLK由SYSCLK经过AHB预分频器得到(通常不分频,即HCLK = SYSCLK)。它供给:

- CPU内核

- 存储器(Flash、SRAM)接口

- DMA控制器

- AHB总线上的外设(如GPIO、CRC等)

HCLK的频率直接决定了CPU取指和总线访问的速度。对于Cortex-M3/M4,HCLK可以高达几十MHz甚至上百MHz。

2.3 APB总线时钟 PCLK------外设的"毛细血管"

系统通过APB1和APB2两条总线连接大部分外设。APB预分频器将HCLK降低到外设能够承受的频率。

- APB1:通常连接低速外设(如USART2/3、I2C1/2、SPI2/3、定时器2-7等),最大频率有限制(如STM32F1为36MHz)。

- APB2:通常连接高速外设(如GPIO、SPI1、USART1、定时器1/8等),可运行在更高频率(如72MHz)。

特别注意:APB总线上的定时器时钟可能被自动倍频。如果APB预分频系数不为1,则定时器的输入时钟 = APB时钟 × 2。这是为了在降低总线功耗的同时,仍能为定时器提供较高的计数频率。

3. 外设时钟门控------省电的"阀门"

MCU内部集成了大量的外设(GPIO、USART、SPI、I2C、定时器、ADC等)。如果所有这些外设都一直运行,功耗会非常可观。

因此,现代MCU为每个外设都配备了时钟门控 功能------一个可以独立打开或关闭该外设时钟的开关。通过设置相应的寄存器位(如RCC_APB1ENR),可以精确控制每个外设是否获得时钟。

没有时钟的外设,其寄存器无法读写,功能完全停止,几乎不消耗动态功耗。这正是低功耗设计的基础。

在实际开发中,我们应该遵循:

- 用哪个外设,开哪个时钟(在初始化时使能)。

- 用完后,及时关闭时钟(如果长时间不用)。

- 不要图省事把所有时钟都打开。

4. 时钟安全系统------心跳的"监护仪"

如果外部高速晶振(HSE)因为焊接不良、老化、振动等原因失效,MCU会怎样?如果没有保护措施,CPU会一直等待HSE稳定,导致系统卡死。

为此,Cortex-M3及更高内核的MCU通常集成了时钟安全系统。当CSS(Clock Security System)被使能后,硬件会持续监控HSE。一旦检测到HSE失效,硬件会自动:

- 将系统时钟源切换到内部HSI(通常8MHz)

- 同时产生一个NMI(不可屏蔽中断),通知软件进行紧急处理(如保存关键数据、进入安全状态、报警等)。

CSS是提高系统可靠性的重要手段,尤其在工业控制、汽车电子等对稳定性要求极高的场景中不可或缺。

5. 低功耗模式下的时钟策略

低功耗是MCU的重要指标。根据功耗和功能保留程度,通常分为几种模式:

| 模式 | CPU | 时钟源 | 外设 | 唤醒源 | 功耗 |

|---|---|---|---|---|---|

| 睡眠模式 | 停止 | 保持 | 保持(用户可选关闭) | 任意中断 | 毫安级 |

| 停止模式 | 停止 | 主时钟(HSE/HSI/PLL)关闭,LSI/LSE可选 | 大部分外设时钟关闭 | 外部中断、RTC | 微安级 |

| 待机模式 | 断电 | 几乎全部关闭,仅LSI/LSE可能保留 | 全部关闭,SRAM内容丢失 | 特定唤醒引脚、RTC、看门狗 | 纳安级 |

在停止模式下,系统时钟被关闭,但可以通过外部中断 (如按键)或RTC闹钟唤醒。唤醒后,时钟恢复需要一定时间(通常几微秒到几十微秒),软件需要重新配置PLL等。

6. 实战:时钟配置示例

我们以STM32F103为例,展示如何将系统时钟配置为72MHz(最高频率)。

c

void RCC_Configuration(void) {

// 1. 开启外部高速晶振 HSE

RCC_HSEConfig(RCC_HSE_ON);

// 等待 HSE 就绪

while(RCC_GetFlagStatus(RCC_FLAG_HSERDY) == RESET);

// 2. 配置 Flash 等待周期(因为72MHz > 24MHz,需要2个等待周期)

FLASH_SetLatency(FLASH_Latency_2);

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

// 3. 配置 PLL:HSE 9倍频 = 8MHz * 9 = 72MHz

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);

RCC_PLLCmd(ENABLE);

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET);

// 4. 切换系统时钟到 PLL

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

while(RCC_GetSYSCLKSource() != 0x08);

// 5. 配置 AHB/APB 分频器

RCC_HCLKConfig(RCC_SYSCLK_Div1); // HCLK = SYSCLK = 72MHz

RCC_PCLK1Config(RCC_HCLK_Div2); // PCLK1 = HCLK/2 = 36MHz

RCC_PCLK2Config(RCC_HCLK_Div1); // PCLK2 = HCLK = 72MHz

}这段代码展示了从HSE起振、PLL倍频到最终分配总线时钟的完整流程。注意Flash等待周期的配置------CPU频率提高后,Flash读取需要插入更多等待周期,否则无法稳定运行。

7. 总结:时钟是系统的"节拍器"

这一讲,我们全面剖析了MCU的时钟系统:

- 时钟源有内部RC和外部晶振,各有优劣。外部晶振精度高但成本高,内部RC启动快但精度低。

- 时钟树通过选择、倍频、分频,从单一的时钟源生成多路不同频率的时钟,供给CPU、总线、外设。

- 外设时钟门控是实现低功耗的关键,按需开关,避免无谓的能量浪费。

- 时钟安全系统为关键应用提供了容错能力,防止晶振失效导致系统崩溃。

- 低功耗模式通过不同程度地关闭时钟和电源,将功耗从毫安级降至纳安级。

- 时钟配置需要综合考虑晶振频率、PLL倍频、Flash等待周期、总线分频等多个因素。

理解时钟系统,不仅是为了让程序跑起来,更是为了让它跑得稳、跑得省。无论是优化性能还是降低功耗,时钟都是绕不开的核心。

下一讲预告 :我们将进入专栏的高潮------内核寄存器详解。我们将深入CPU的"工作台",逐一拆解通用寄存器、堆栈指针、程序计数器以及特殊功能寄存器,看看C语言中的变量、函数调用、中断是如何与这些寄存器交互的。

思考题:在停止模式下,如果外部中断唤醒后,系统时钟恢复到了HSI(8MHz),而你之前配置的USART波特率是基于72MHz的PLL计算的。这时直接调用USART发送数据会发生什么?如何避免这个问题?