kernel(内核):x86、8051、MIPS、ARM。

前面介绍的51单片机,使用的是8051内核,我们使用的Windows电脑用的是x86内核。本文将介绍ARM内核。

一、基本概念

1. 指令集架构

CISC (Complex Instruction Set Comouter):复杂指令集计算机。eg:x86。

- 芯片面积大,加工成本高,复杂、体积大、功耗大

- 28效应:80%的情况下只使用到20%的功能

RISC (Reduced Instruction Set Comouter):精简指令集计算机。eg:ARM。

- 芯片面积小,加工成本低,功耗低、体积小,用于便携式设备。

- 对于28效应的问题,减少了80%的功能。

2. ARM系列

ARM是一家只设计内核,不生产芯片,供给半导体厂商的公司。

ARM系列的版本经过了ARM1 ~ ARM11的升级,现在最新版本是Cortex版本。

Cortex 三大领域系列:

- A:Application,应用领域。eg:手机、应用电子领域。

- R:Real time,实时性领域。eg:汽车电子、航空航天。

- M:Micro,微控制器领域。eg:MCU、单片机。

现在的ARM,精简指令集计算机,imx6null,Cortex-A7内核,32位存储器(一条指令占4byte)

stm32(32位单片机)使用的是ARM架构的芯片,Cortex-M3内核

3. ARM内核结构组成

3.1 寄存器

R0~R12:通用寄存器,存放数据。

SP寄存器(R13):stack pointer,栈指针寄存器。用来管理栈区,可以直接使用的栈区指针,一直指向栈顶。

LR寄存器(R14):linked register,链接寄存器。保存函数的返回地址。

PC寄存器(R15):program counter,程序计数器。本质上是一个指针,指向当前正在执行指令的下一条指令。

三级流水线结构(三级同时并行执行):

PC取指令

通过译码器翻译

交给kernel执行指令

PSR(状态指示寄存器):

- cpsr寄存器:current program status register,当前程序状态寄存器。保存程序运行到某一步时的状态(溢出、进位、借位等)。

- spsr寄存器:save program status register,保存/备份程序状态寄存器。异常发生时,保存cpsr寄存器中的程序状态。

3.2 内部单元

ALU:算术逻辑单元,与R0~R12搭配使用,控制存储。

MMU:Mermory Manager Unit,内存管理单元。用于管理虚拟内存到物理内存映射,从而提高物理内存的利用率。ARM的物理内存:512MB。

Cache:高速数据缓存。直接从cache访问数据,提高CPU访问速度。

- icache:instruction,指令缓存

- dcache:data,数据缓存

内存存储架构:

冯.诺依曼架构:数据和指令存放到同一片内存。

哈佛架构:数据和指令独立存储。(ARM)

3.3 内部总线

单总线通信:通过一根线/一组线和外设通信,和某个外设通信时,其他外设接不进来。

双总线通信:

- AHB总线:先进高速总线,连接通信速率快的外设(USB、网卡、RAM)。

- APB总线:先进外设总线,连接通信速率慢的外设(GPIO、UART)。

4. 编译

s3c2440 --- ARM920T,RAM:4KB

内核代码是汇编语言。

编译流程:

- 预处理(.i):展开头文件、宏定义替换、条件编译(#if #endif)

- 编译(.s):将C语言编译成汇编语言。

- 汇编(.o):将汇编语言编译成二进制计算机语言。

- 链接 :链接成一个可执行文件。

交叉编译:在一个平台编写编译程序,在另外一个平台运行程序。

二、电子硬件

1. 三极管

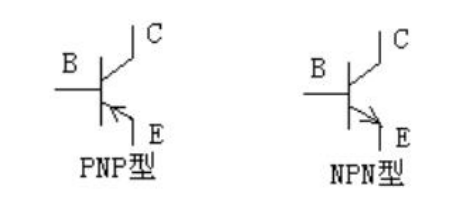

PNP发射极接VCC,基极接低电平导通;NPN发射极接GND,基极接高电平导通。

2. 存储器

计算机系统的硬件组成:控制器、运算器、输入设备、输出设备、存储器。

1). 三级存储系统:

|------------|--------|--------|----------|

| 名称 | 速度 | 容量 | 价格 |

| cache | 快 | 慢 | 小 | 大 | 昂贵 | 便宜 |

| 主存储器(RAM) | 快 | 慢 | 小 | 大 | 昂贵 | 便宜 |

| 辅助存储器(ROM) | 快 | 慢 | 小 | 大 | 昂贵 | 便宜 |

RAM:易失性存储器。最新版本:iram。

ROM:非易失性存储器。最新版本:flash闪存。

2). flash分类:

nor flash:每一个字节可以被寻址,有数据总线和地址总线。

nand flash:无法被寻址,以固定块大小写入或读取数据。

3). 指令集版本

指令集版本:armv1 - armv8

- imx6ull -> Cortex-A7 -> armv7

- S3C2440 -> ARM920T -> armv4

- exnoy4412 -> CortexA8 -> armv8

三、ARM内核架构

1. 处理器工作模式

ARM有7个基本工作模式,还有两个Cortex-A特有模式。

- **User:**非特权模式,大部分任务执行在这种模式(使用寄存器最少的模式)

- FIQ:当一个高优先级(fast)中断产生时将会进入这种模式

- IRQ:当一个低优先级(normal)中断产生时将会进入这种模式

- Supervisor:当复位或软中断指令执行时将会进入这种模式(管理员SVC,默认模式)

- Abort:当存取异常时将会进入这种模式

- Undef:当执行未定义指令时会进入这种模式

- System:使用和User模式相同寄存器集的特权模式。

2. ARM寄存器

ARM有37个寄存器,Cortex-A有40个寄存器。

ARM每个工作模式的sp、lr、pc寄存器都是独立的。

程序状态寄存器:

B5 --- T,处理器状态位

M[4:0] --- Mode,处理器模式位

- User : 10000

- FIQ :10001

- IRQ :10010

- Supervisor :10011

- Abort :10111

- Undefined:11011

- System :11111

3. 异常处理流程

1).当异常产生时, ARM :

- 拷贝 CPSR 到 SPSR

- 设置适当的 CPSR 位:改变处理器状态进入ARM态(默认状态,不用改变),改变处理器模式进入相应的异常模式

- 保存返回地址到 LR

- 设置 PC 为相应的异常向量

2).返回时, 异常处理需要:

- 从 SPSR恢复CPSR

- 从LR恢复PC

- Note:这些操作只能在 ARM 态执行

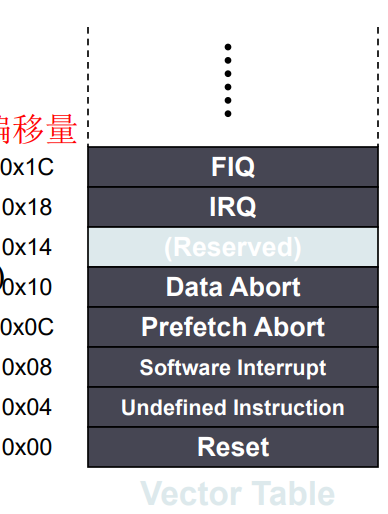

中断向量表:存放中断服务函数的入口地址的数组。

异常向量表:存放跳转到对应异常服务函数的指令的数组。

ARM有七种异常指令。

四、汇编指令

汇编指令放在.s文件中,每条指令后不用加分号。注释不用"//",用";"

1. MOV 赋值

1). MOV <Rd>,#<const>

-

Rd:目标寄存器。

-

const:常量。

MOV r0,#1 ;r0=1

2). MOV <Rd>,<Rm>

-

Rd:目标寄存器。

-

Rm:第一操作数寄存器

mov r2,r1 ;r2=r1

3). MOV <Rd>,<Rm>,<type> #<n>

-

ASR:算术右移,针对于有符号数,最高位补符号位。

-

LSR:逻辑右移,针对于无符号数,最高位补0。

-

ROR:循环右移,将移出的最低位补到最高位。

-

LSL:逻辑左移,低位补0。

mov r3,r2,lsl #3 ;r3=r2<<3

mov r4,r3,asr r0 ;r4=r3>>1

2. ADD 加法

1). ADD <Rd>,<Rn>,#<const>

add r0,r3,#2 ;r0=r3+22). ADD <Rd>,<Rn>,<Rm>

bash

add r0,r1,r2 ;r0=r1+r23). ADD <Rd>,<Rn>,<Rm>,<type>,<Rs>

cpp

mov r3,r2,r1,lsl r0 ;r3=r2+(r1<<r0)