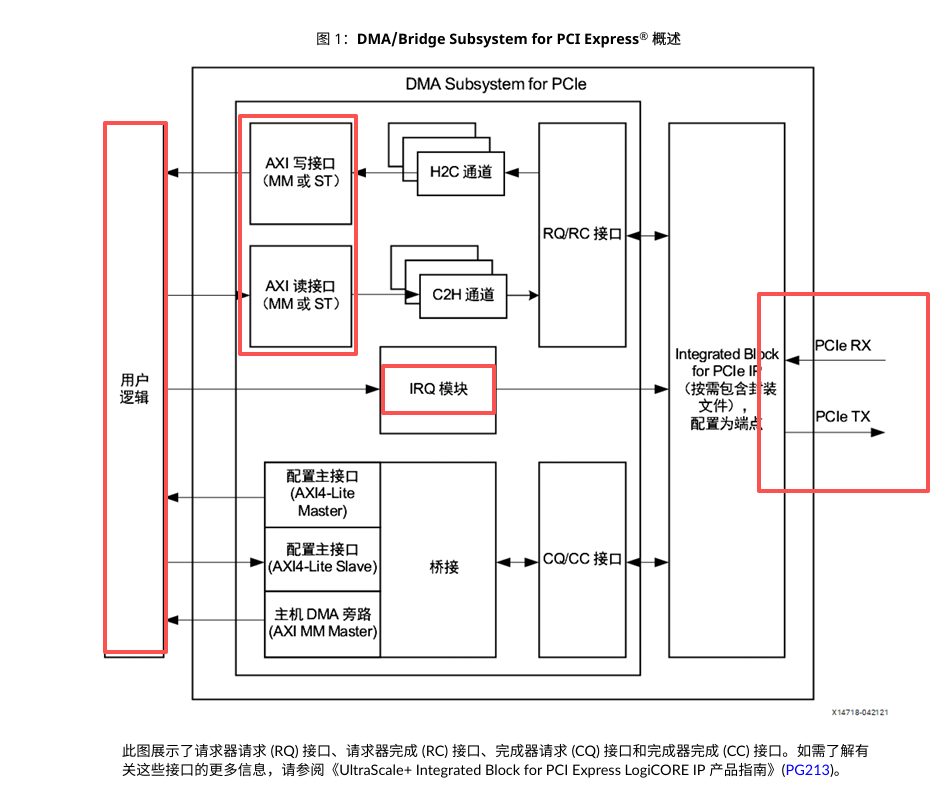

DMA和Bridge是两种模式,

DMA功能通过AXI接口或者AXI Stream接口连接至RTL逻辑。

Bridge(桥接)功能,只适用于UltraScale类器件。

以下将DMA/Bridge Subsystem for PCI Express简称为XDMA。

XDMA最根本的作用是在主机存储器与驻留在FPGA中的存储器之间移动数据。

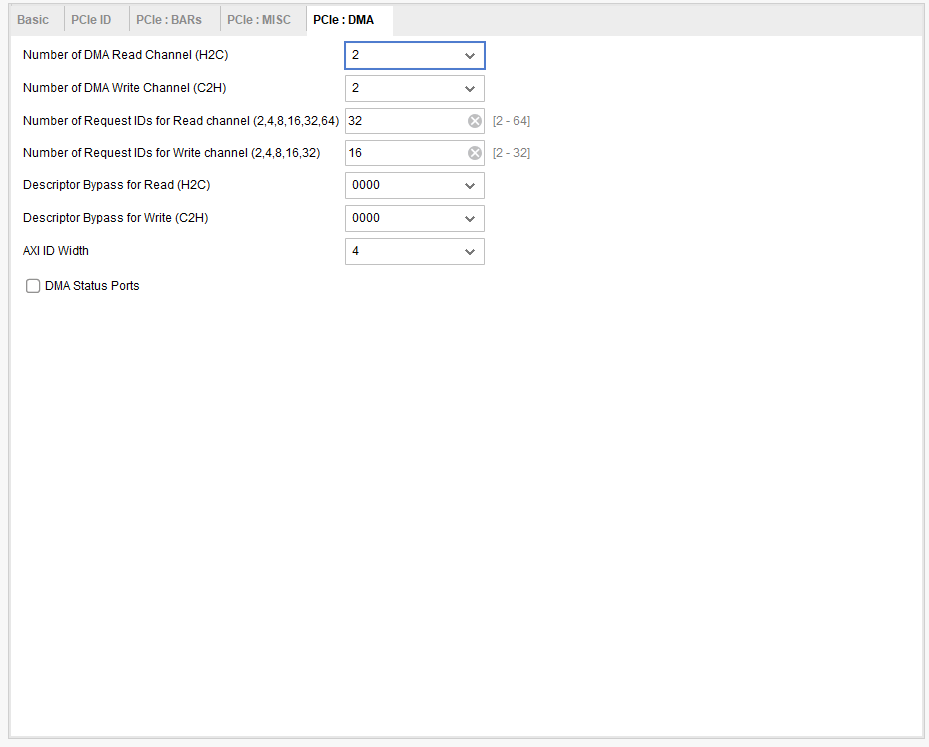

将数据从主机存储器移动到FPGA存储器上的过程称为主机到卡(Host to Card, H2C)。

相反,将数据从FPGA存储器上移动到主机存储器的过程称为卡到主机(Card to Host, C2H)。

使用XDMA实现卡到主机功能:

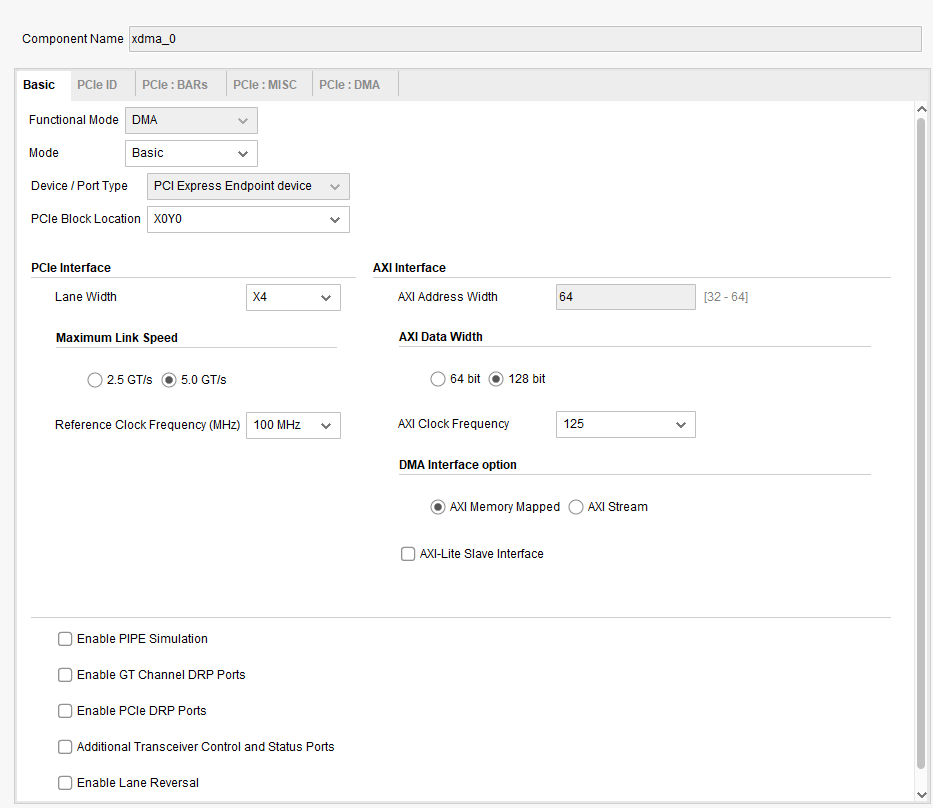

Basic选项卡

功能:选择DMA功能;

模式:选择基础模式;

器件、端口类型:只支持Endpoint类型;

PCIe块位置:用于从可用集成块中选择,以生成特定位置的约束文件和管脚分配。

通道宽度:子系统需要选择初始宽度;

最大链路速度:子系统需要选择PCIe Gen速度;

参考时钟频率:默认100mhz,但也支持125mhz和250mhz;

复位源:可选择用户复位或者物理就绪;

AXI地址位宽:当前只支持64bit;

AXI数据位宽:当前选择128bit;

AXI时钟频率:根据通道宽度和链路速度可选择;

DMA接口选项:可选项AXI或AXI Stream;

AXI Lite从接口:可以通过该接口配置少数寄存器?暂时不确定;