由于数电实验课程,需要使用modelsim这个古老的软件,用verilog语言实现数字电路逻辑,初步要求实现仿真即可。

1、下载与安装

Modelsim软件安装及高云库编译--小梅哥 本人根据视频前九分钟内容下载modelsim安装包(10.7版本)并破解,涉及链接--【软件工具合集2】 Powered by Discuz!;注意,视频中添加library等内容无需操作。

注:唯一的困难可能是百度网盘无敌的下载速度问题。

2、新建工程

练习 3:MinMax 电路

需要设计并编码一个计算最小值和最大值的组合电路。这个电路要符合下面实体声明。

module MinMax(

input Min0Max1,

input [3:0] X,

input [3:0] Y,

output reg [3:0] Z

);

endmodule

1. 当 Min0Max1 为 0 时,Z 是 X 和 Y 中的最小值(Min),当 Min0Max1 为 1 时,Z 是 X 和 Y 中的最大值(Max)。注意,我们将 X、Y 和 Z 视为无符号二进制数向量。

2.你也可以在minmax_tb.v 中找到testbench,将下面的minmax_tb.v文件和你的编写的.v程序一起编译,可以获得电路的仿真结果。

3.请提交你编写代码的全屏截图和仿真结果的全屏截图。接下来我们来完成这个任务。

首先,手动在资源管理器中新建一个文件夹,名字最好用英文,且不要数字开头,比如我新建一个code3的文件夹在桌面。

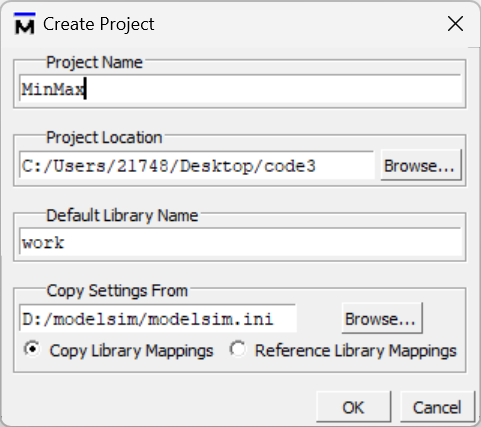

打开我们的modelsim,左上角file--new--Project...,如果有已经打开的工程,会提示你直接关掉这个工程,按需求确认即可。

之后,输入Project Name--MinMax,Project location--刚才新建的code3路径,其余保持默认即可,然后点击OK。

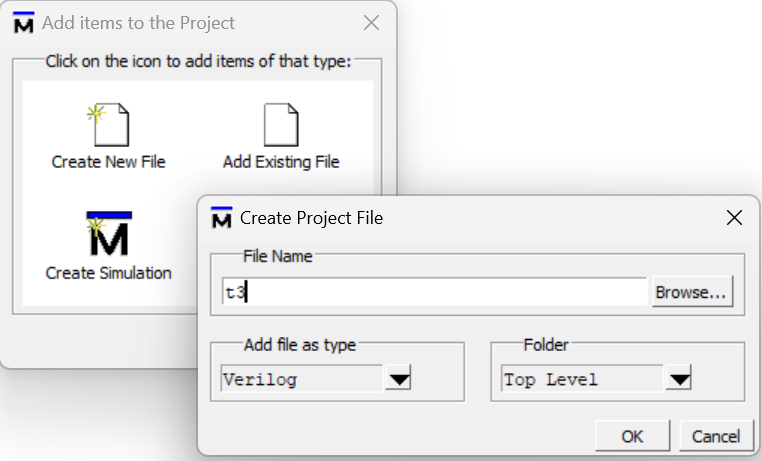

之后弹出Add界面,选择Create New File,不妨取名字t3,选择类型Verilog,然后同理新建一个t3_test,前者用于定义用到的module,后者写测试程序。

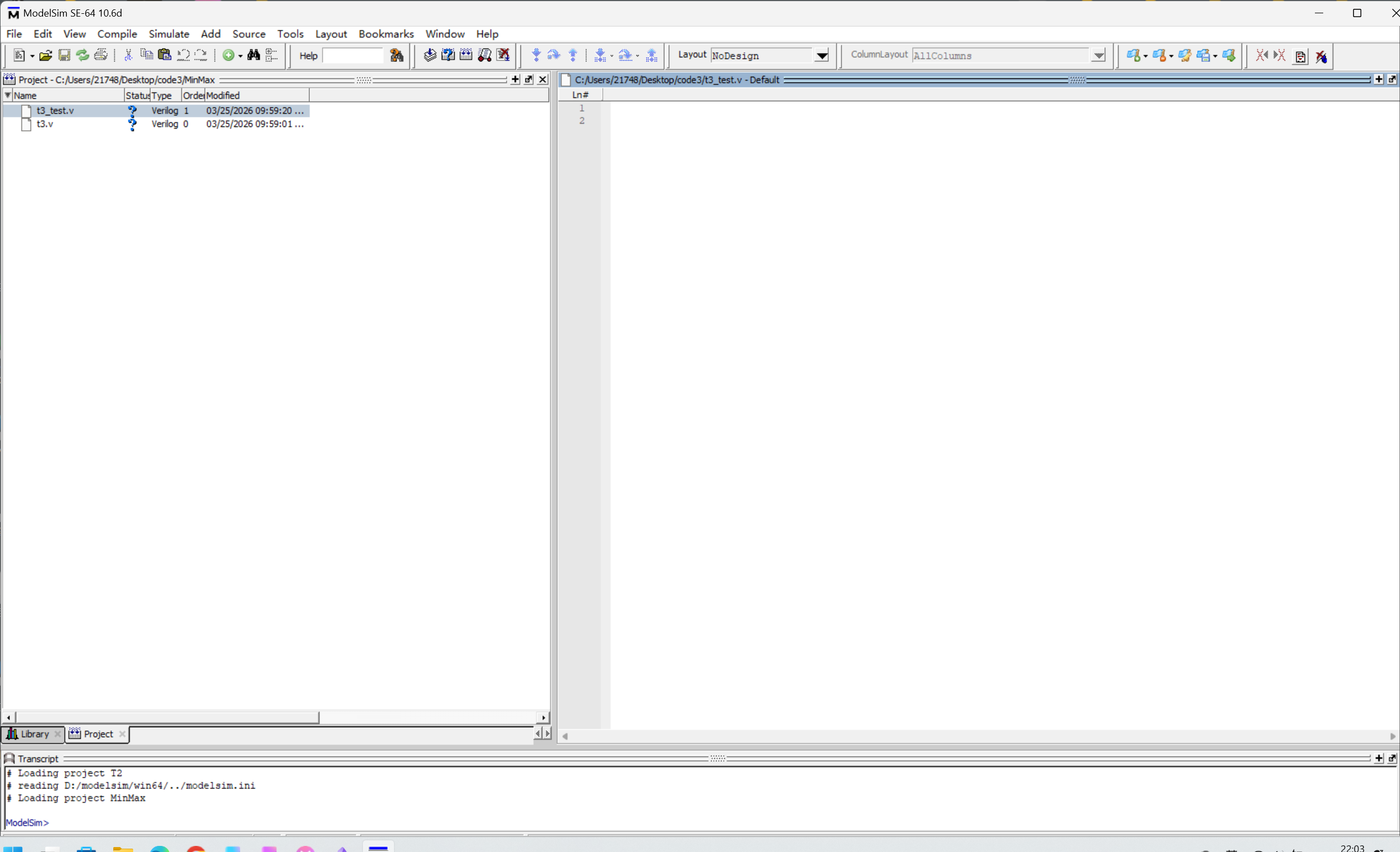

之后左键双击t3.v文件,打开右边的编辑页面。

3、第一个程序(compile/simulate)

verilog

// t3.v

module MinMax(

input Min0Max1,

input [3:0] X,

input [3:0] Y,

output reg [3:0] Z

);

always @(*) begin

if (Min0Max1 == 0) begin

// 求最小值

if (X < Y)

Z = X;

else

Z = Y;

end

else begin

// 求最大值

if (X > Y)

Z = X;

else

Z = Y;

end

end

endmodule该文件定义了MinMax的module,包含了MinMax 的端口声明以及数据流(DATAFLOW)架构,后者其实就是always寻找最大最小值的那部分代码,即标志位Min0Max1为0时求最小值,为1返回最大值Z。数据都是4bit的数。

verilog

//t3_test.v

`timescale 1ns/1ps

module MinMax_tb;

reg Min0Max1;

reg [3:0] X, Y;

wire [3:0] Z;

MinMax uut (

.Min0Max1(Min0Max1),

.X(X), .Y(Y), .Z(Z)

);

initial begin

// 测试最小值模式

Min0Max1 = 0; X = 4'd3; Y = 4'd7; #10; // Z 应为 3

Min0Max1 = 0; X = 4'd12; Y = 4'd5; #10; // Z 应为 5

Min0Max1 = 0; X = 4'd9; Y = 4'd9; #10; // Z 应为 9

Min0Max1 = 0; X = 4'd0; Y = 4'd15; #10; // Z 应为 0

// 测试最大值模式

Min0Max1 = 1; X = 4'd3; Y = 4'd7; #10; // Z 应为 7

Min0Max1 = 1; X = 4'd12; Y = 4'd5; #10; // Z 应为 12

Min0Max1 = 1; X = 4'd9; Y = 4'd9; #10; // Z 应为 9

Min0Max1 = 1; X = 4'd0; Y = 4'd15; #10; // Z 应为 15

$stop;

end

endmodule这个verilog文件使用了MinMax的module,然后编写了测试逻辑,即通过编辑激励来仿真;之后我们就simulate这个文件。

细节1:一定要先ctrl+s先保存两个文件,然后再compile编译,不然编译的是空文件,导致后面的work没有可以simulate的文件。

可以在上边栏选择编译选项,也可以右键文件选择编译,也可以最本质的命令行编译,之后文件上的红色问号变成了绿色对号。

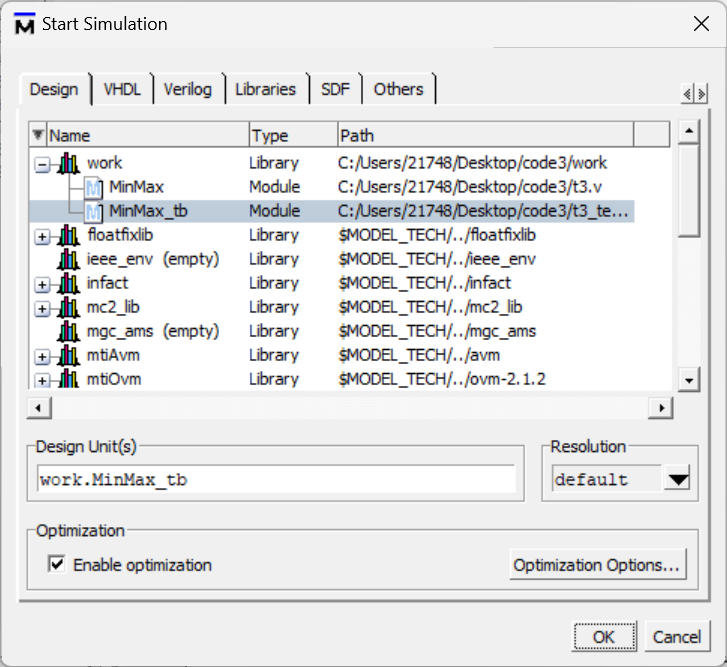

编译完成后,点击上栏的Simulate--Start Simulation,

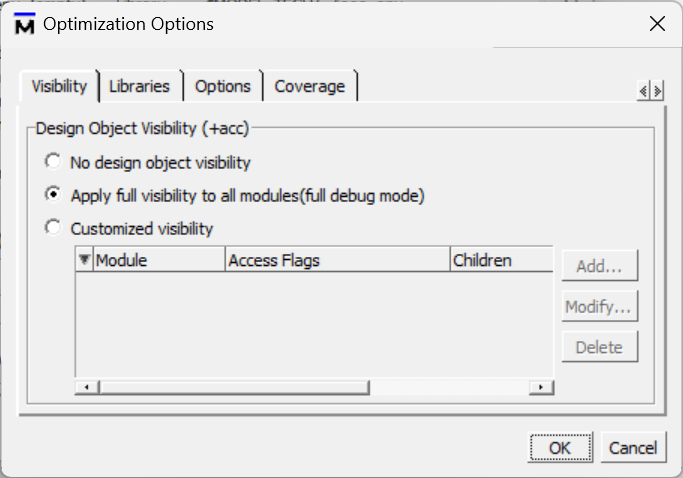

首先点击左下角的Optimization Option选项,确保选择的Apply full visibility...而不是No design object visibility,不然下一步向wave中添加object却发现没有。

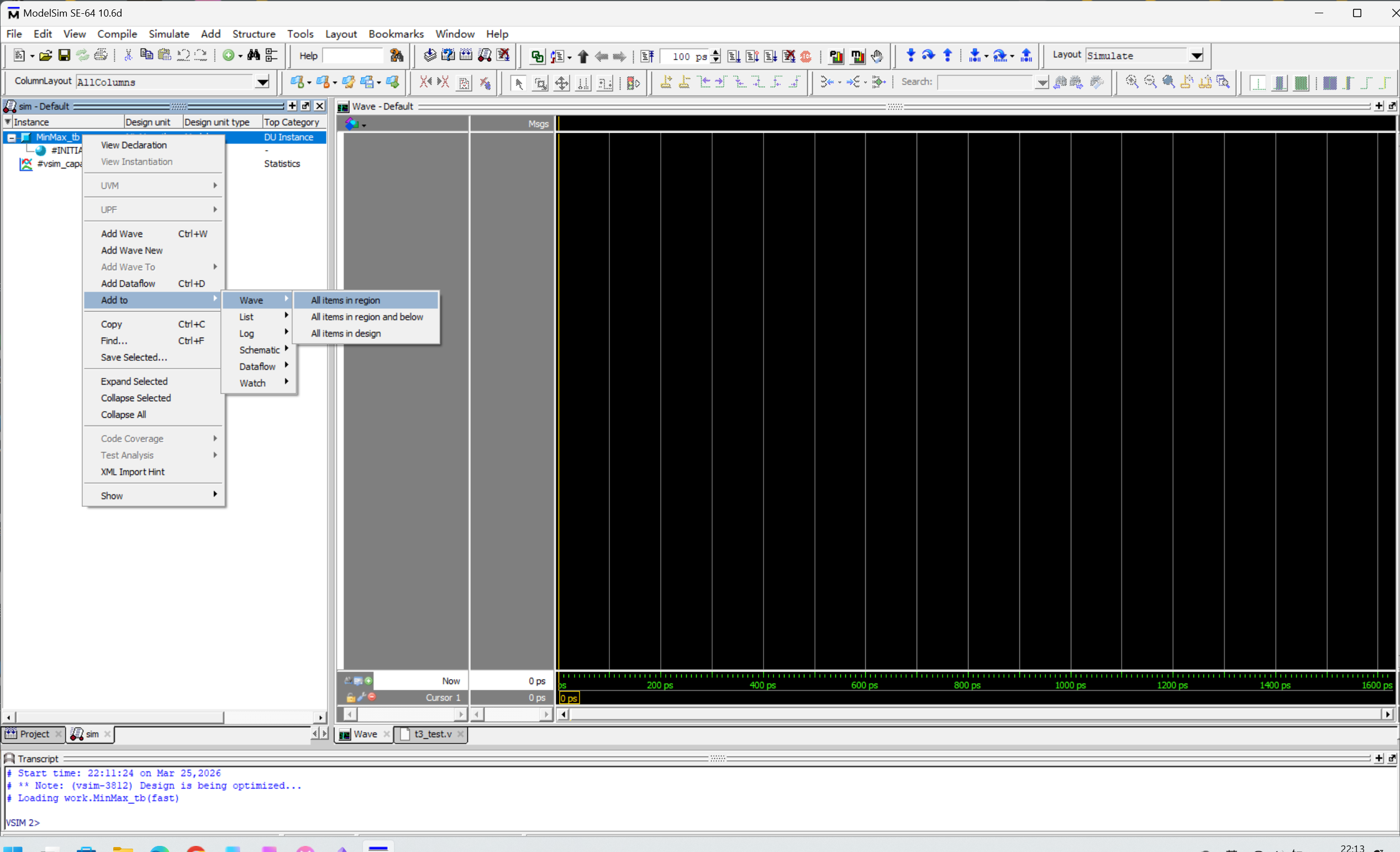

之后在刚才的simulate页面选择work中的MinMax_tb文件(这个文件只有成功编译才会生成,如果没保存就编译则无),点击OK。

4、查看波形

然后尝试查看波形,点击上栏View--wave

然后按图中操作,向wave中添加object,

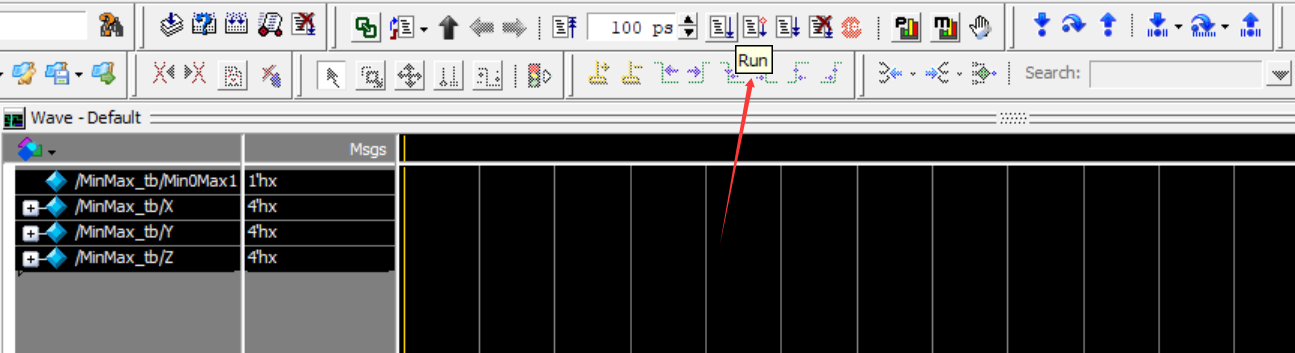

之后在上栏中直接点击run,或者根据代码要求,手动在终端输入命令,比如run 100ns,因为我的测试程序波形跑了80ns,但是直接run只会跑100ps。

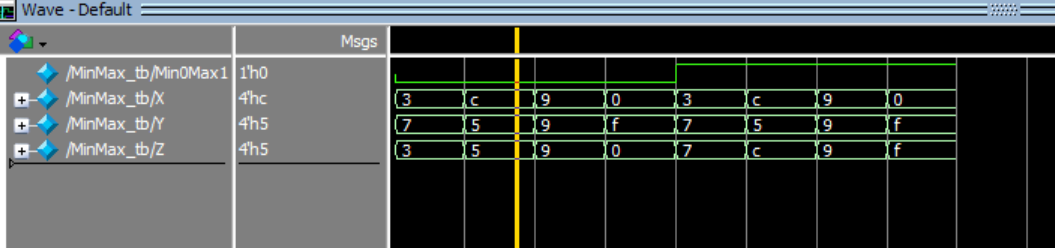

通过波形图黄色线所在时刻可以看到,Min0Max1=0挑选最小值;而X=4'hc,即4bit的十六进制数c,即十进制数12,而Y=5,则选择较小值幅值给Z,Z=5符合代码逻辑。成功了!

ctrl+鼠标滑轮可以条件时间轴缩放。