目录

前言

这段时间学习ESP32,手里有一块微雪的ESP-32P4的开发板,对其中的串口烧录电路产生了一些疑惑。经过多种分析,找到了一种自洽方案,记录一下,同时也有一定的参考意义。

一、硬件基础

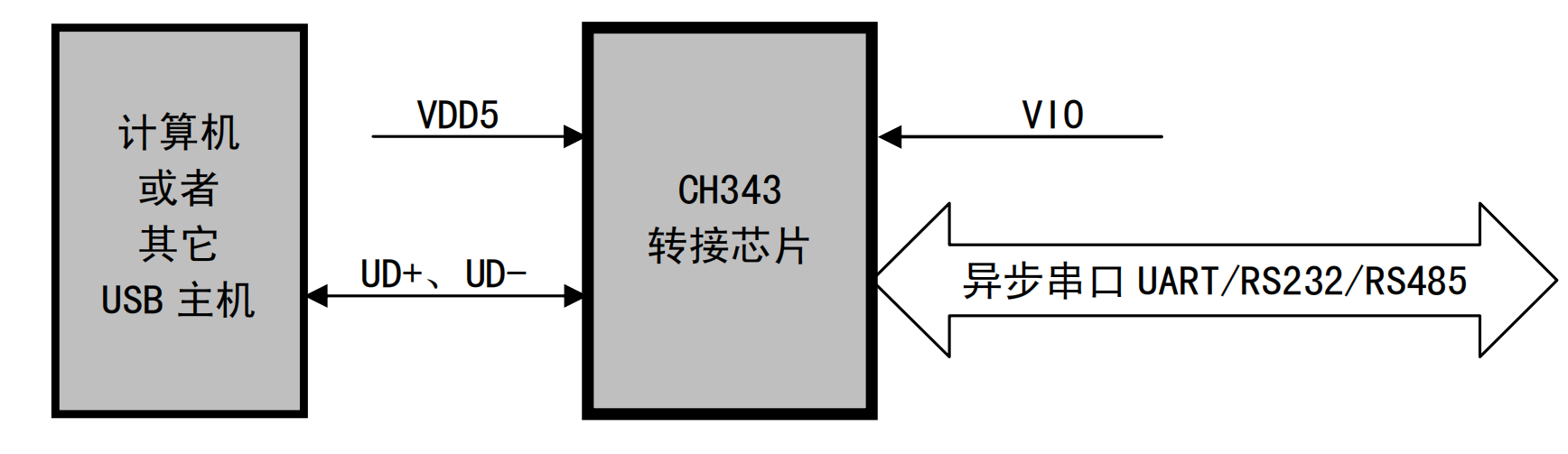

USB串口信号主要是一对差分信号,想要实现和芯片之间的通信,需要转换成UART串口信号。而CH343是一款由沁恒微电子(WCH)推出的USB转串口芯片,主要用于实现USB接口与UART(通用异步收发传输器)之间的双向通信。该芯片内置USB控制器和UART控制器,支持多种波特率配置,适用于工业控制、嵌入式设备调试等场景。

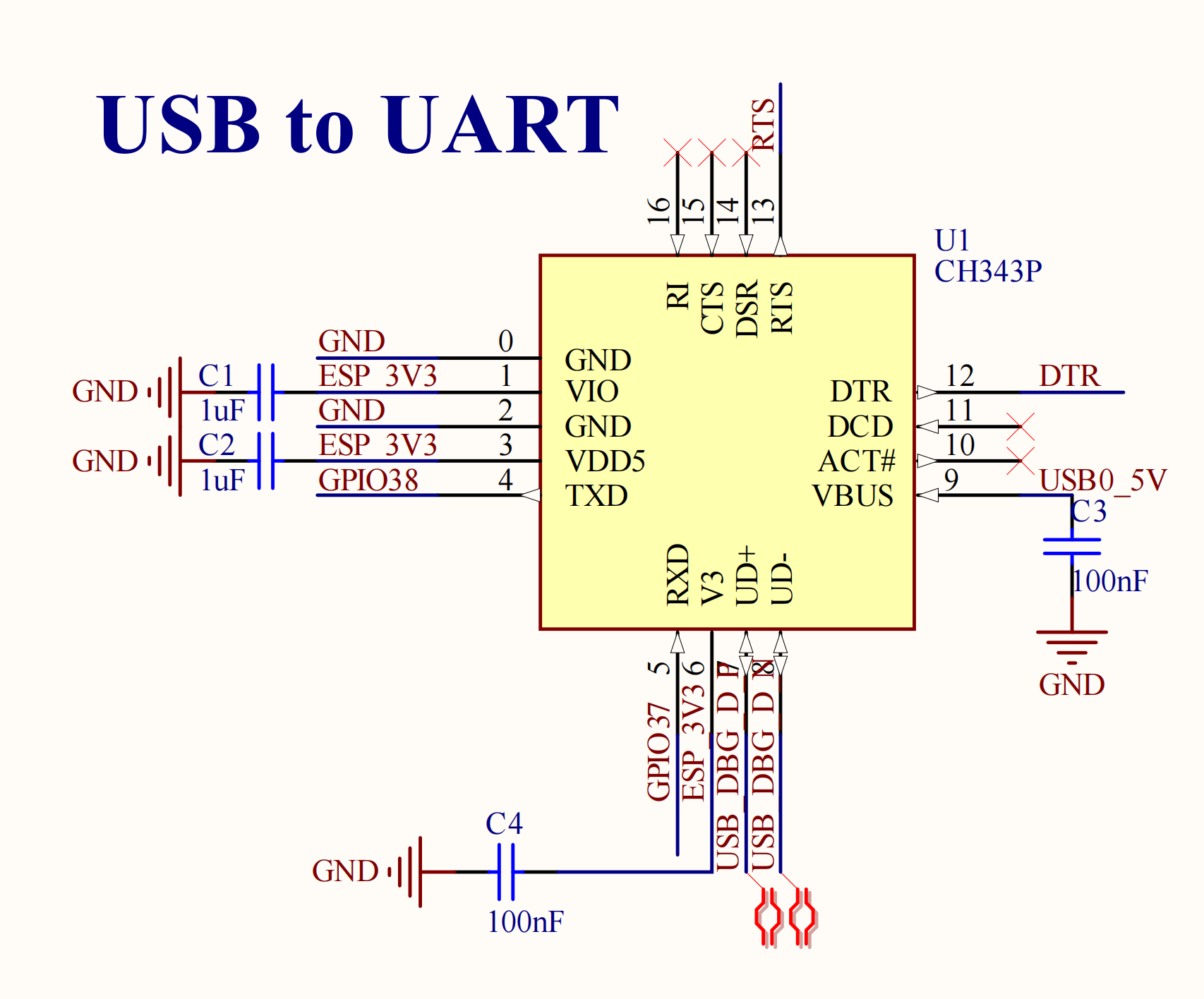

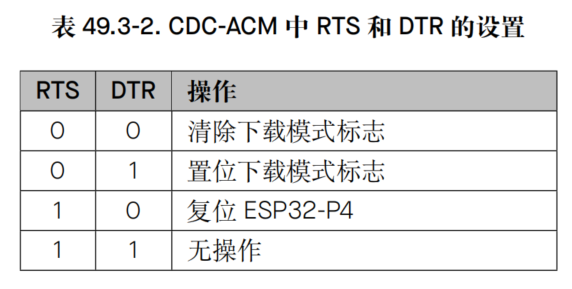

CH343不仅可以用来实现芯片和计算机之间的双向通信,还可以复位芯片并选择使其进入下载模式,从而烧录新的固件。这 一功能可通过设置虚拟串口的 RTS 和 DTR 线来实现。下图是CH343的外围电路图。

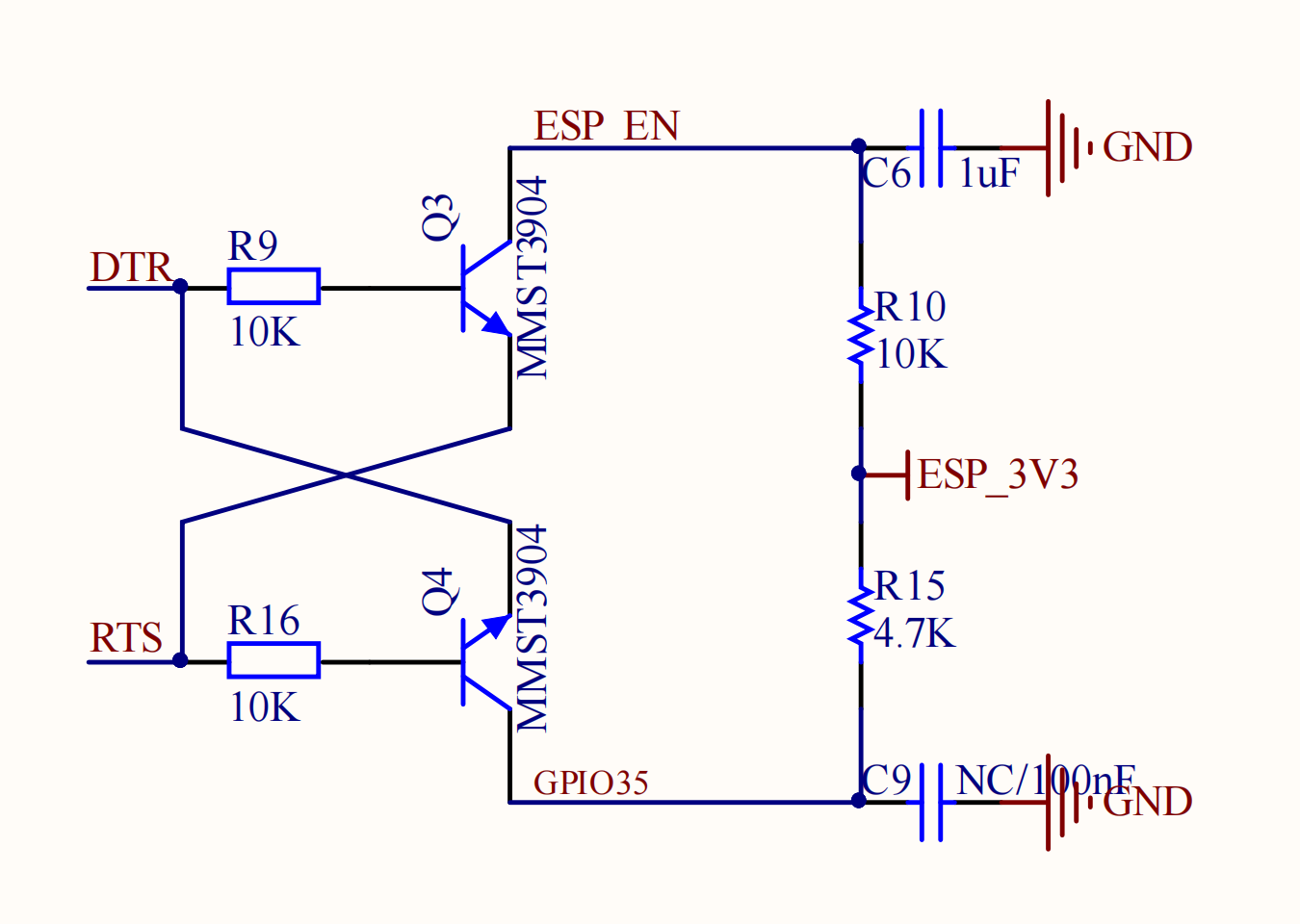

第一张图很好理解,只要用过这类芯片的同学都看得懂。D+和D-接到USB的差分信号上;RXD和TXD接到芯片的UART串口IO上。所以这就能实现通信了,但第二张图是RTS 和 DTR外围设计图,来看一下如何实现的。

二、烧录模式时序

ESP_EN是芯片的复位引脚,GPIO35是芯片的BOOT引脚。ESP32-P4 进入下载模式的必要条件是:

- 先拉低 BOOT (GPIO35=L)(让芯片复位时采样到下载模式)

- 再拉低 EN (ESP_EN=L)(触发芯片复位)

- 保持两者同时为低至少 10ms

- 先释放 EN (ESP_EN=H)(芯片重启,采样 BOOT 电平)

- 最后释放 BOOT (GPIO35=H)

其中最重要的是当ESP_EN 上升沿后检测BOOT的电平,如果是低电平则进入下载模式。

那对我们这个电路分析一下RTS 和 DTR电平对应ESP_EN和GPIO35的电平。如下图。

| DTR | RTS | Q3 状态 | ESP_EN | Q4 状态 | GPIO35 |

|---|---|---|---|---|---|

| H | H | 截止 | H | 截止 | H |

| H | L | 导通 | L | 截止 | H |

| L | H | 截止 | H | 导通 | L |

| L | L | 截止 | H | 截止 | H |

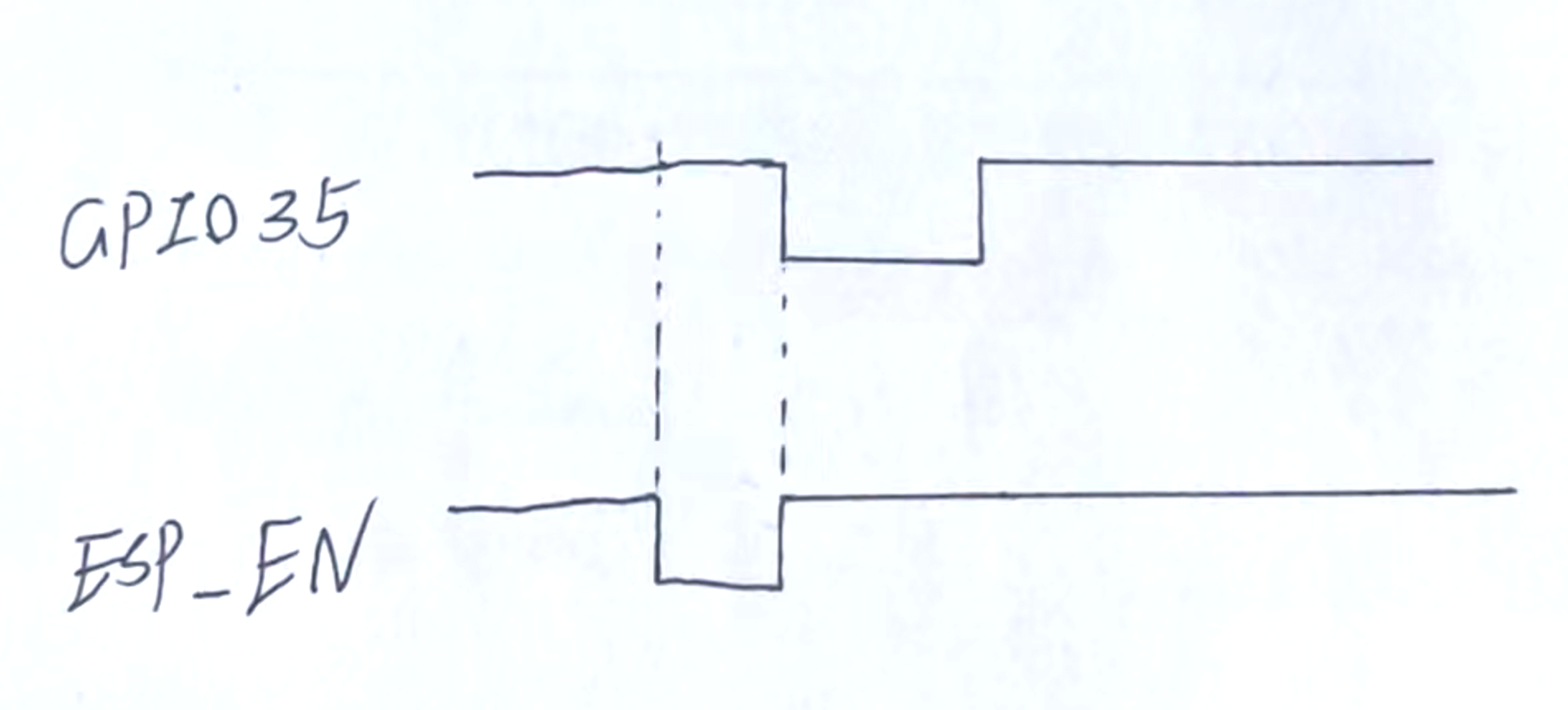

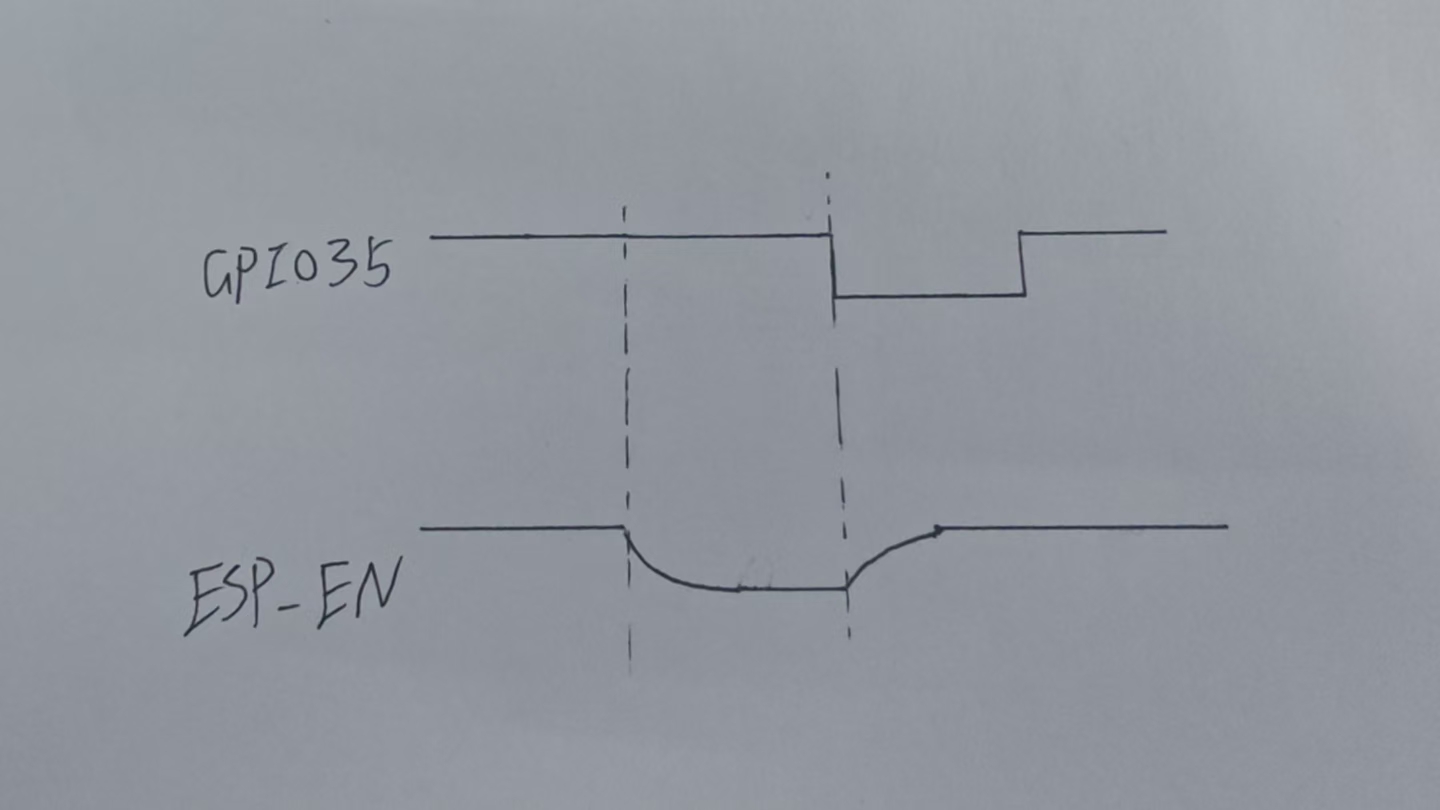

芯片的RTS 和 DTR时序如下

那么此时的BOOT和ESP_EN电平变化如下,怎么看都不符合进入下载模式的电平要求。

我们再回看第二张图,发现ESP_EN和GPIO35是通过RC电路实现电平变化的。时间常数如下。

| 引脚 | 电容 | 上拉电阻 | 时间常数 τ = R×C |

|---|---|---|---|

| ESP_EN | 1uF | 10kΩ | 10k×1uF = 10ms |

| GPIO35 | NC/100nF | 4.7kΩ | 4.7k×100nF = 0.47ms(甚至更小) |

因为电容两端电压不能突变,电平变化时间为2.2RC,所以ESP_EN的一个跳变沿的时间是22ms,实际中GPIO35的电容没有接,可以看成瞬间变化。那么把这一部分时间加入到上图时序中如下:

再ESP_EN从低电平跳变到高电平需要花费至少22ms,按芯片高电平压阈值一般在2.3V左右,也就是需要上升到3.3V的70%,按公式,计算得 t = 1.2RC = 12ms。加上三极管还有结电容和开关速度,最后的值只会大于这个数。从而满足:保持两者同时为低至少 10ms,的要求。电路能够实现进入下载模式实现烧录。

总结

以上电路设计从理论上能实现烧录功能,实际上更是没问题。但电路设计的有些复杂和极限,不知道是不是还有其他角度的问题需要考虑。

本文我不确保我分析角度的一定准确,只是找到了我自己知识点的一种自洽,这种自洽足够说服我自己。但仅供大家参考