一、C语言

套接字:

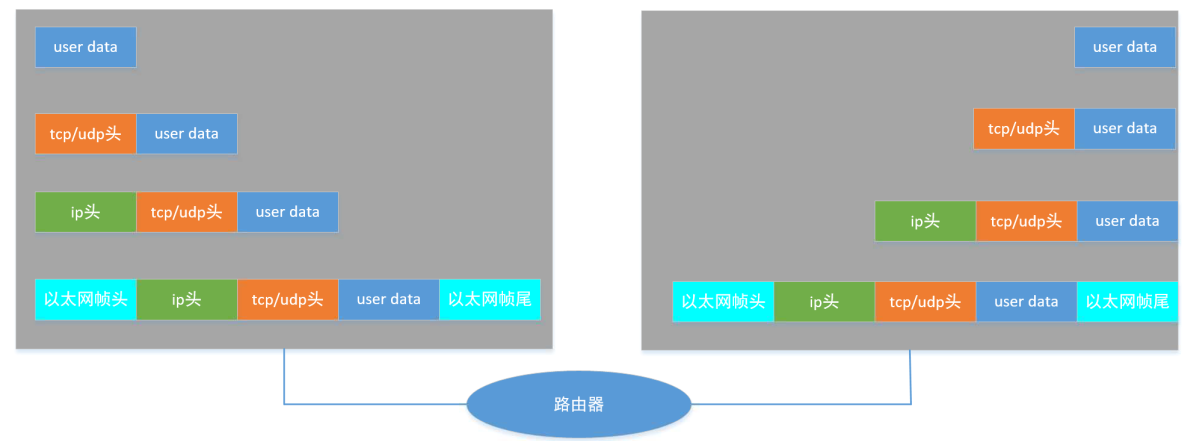

- 交换机:二层设备,基于 MAC 地址转发,只在同一网段工作,无路由能力;

- 路由器:三层设备,基于 IP 地址转发,跨网段互联;

- 网关:网络的 "出口点",路由器常充当内网的默认网关

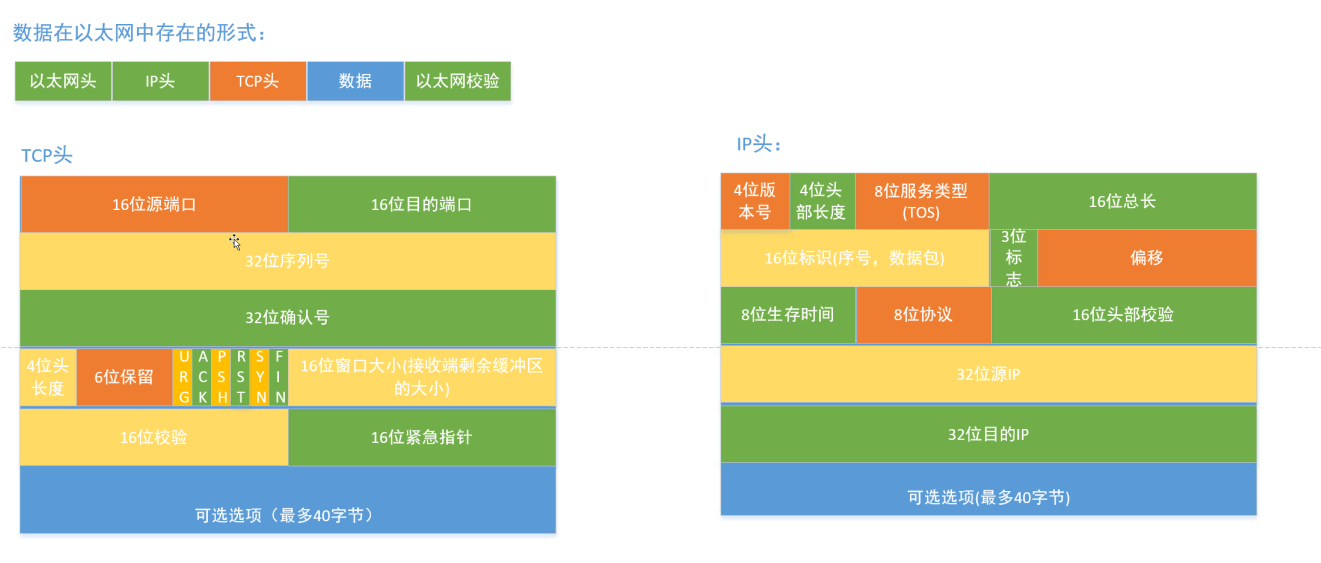

URG:紧急指针有效。

作用 :标记数据包中包含紧急数据,需要优先处理,无需等待缓冲区满。

ACK:确认号有效

作用 :除了第一次建立连接的 SYN 包外,几乎所有 TCP 数据包都会置位 ACK,是

可靠传输的基础。

PSH:立即推送数据

作用 :要求接收方立即将数据推送给应用层,不要在缓冲区等待更多数据。

RST:重置连接

作用 :强制异常关闭连接,拒绝继续通信,清空所有缓冲区数据。

SYN:同步序列号(建立连接)

作用 :用于建立 TCP 连接,发起方向接收方同步初始序列号(ISN)。

FIN:释放连接

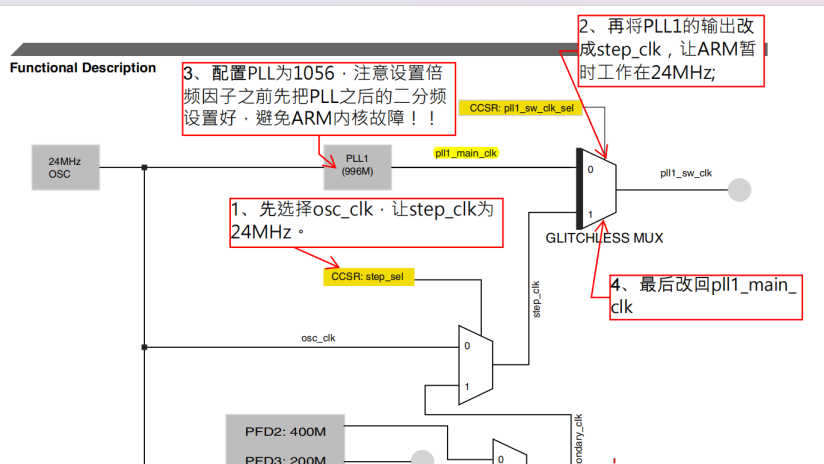

二、arm时钟

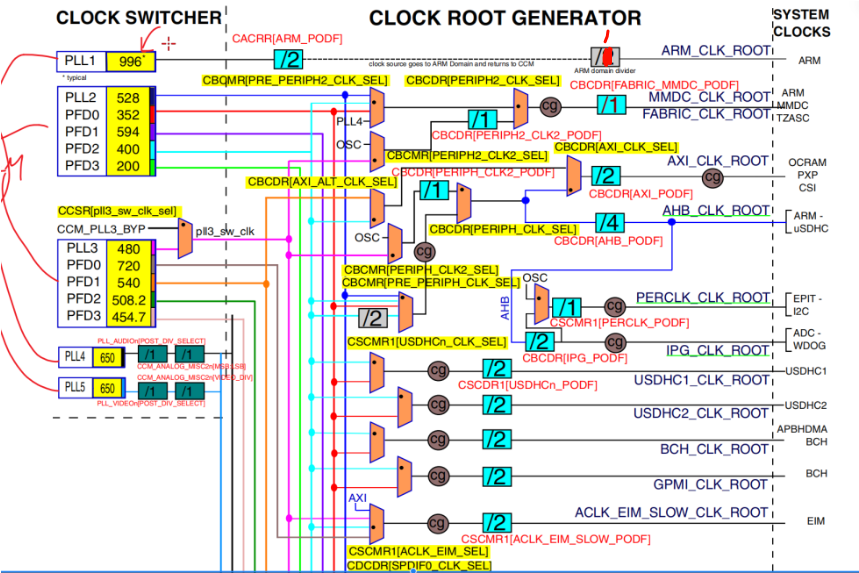

输入时钟源(左侧 CLOCK SWITCHER)

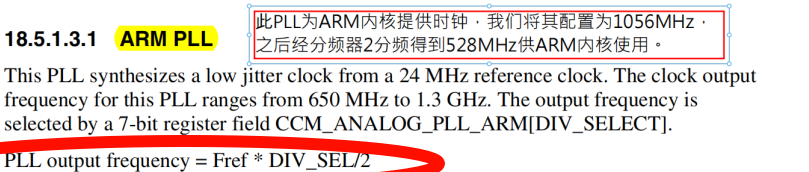

- PLL1 (建议996MHz):ARM PLL,专门给 CPU 内核提供高频时钟。内核 默认528Mhz

- PLL2 (固定528MHz):系统 PLL,带 4 路 PFD 分频输出(352/594/400/200MHz),用于DDR、外设等。

- PLL3 (固定480MHz):USB / 系统 PLL,带 4 路 PFD 分频输(720/540/508.2/454.7MHz),用于 AHB、IPG 等总线。

- PLL4 (650MHz):Audio PLL,用于音频外设。

- PLL5 (650MHz):Video PLL,用于显示 / 视频外设。

- 还可旁路 PLL,直接使用 OSC 24MHz 或其他外部时钟。

关键寄存器控制

- CBxMR 系列 :时钟源选择寄存器(如

CBQMR[PRE_PERIPH2_CLK_SEL]),用于选择多路输入中的一路。 - CBCDR/CSCDR 系列 :时钟分频寄存器(如

CBCDR[AHB_PDF]),设置后分频系数。 - CACRR:专门用于 ARM 时钟的分频控制。

- cg:时钟门控位,用于关闭未使用模块的时钟以降低功耗。

- **MUX:**复用选择,多路选择器,从多个输入时钟源中选择一路作为当前时钟路径的输入。

| 符号颜色 | 名称 | 位宽 | 分频范围 | 用途 |

|---|---|---|---|---|

| 灰色 | Static Divider | 固定 | 固定分频比(如 ÷2、÷4) | 固定比例的时钟分频 |

| 深绿色 | 2-bit Divider | 2bit | 1~4(即 ÷1、÷2、÷3、÷4) | 简单、少档位的分频 |

| 青色 | 3-bit Divider | 3bit | 1~8 | 中等范围分频 |

| 橄榄绿 | 6-bit Divider | 6bit | 1~64 | 精细、大范围分频(如外设时钟微调) |

CCM:时钟控制器(Clock Controller Module)CCM_ANALOG:模拟 PLL 锁相环控制器- PFD(PLL2) 频率 = 基准频率(528) × 18 / PFD_FRAQ

- PFD(PLL3) 频率 = 480 × 18 / FRAC

cs

void clk_init(void)

{

//ARM clk 528

CCM->CCSR &= ~(1 << 8);

CCM->CCSR |= (1 << 2);

unsigned int tmp = CCM->CACRR;

tmp &= ~(0x7 << 0);

tmp |= (0x1 << 0);

CCM->CACRR = tmp;

tmp = CCM_ANALOG->PLL_ARM;

tmp &= ~(0x3 << 14);

tmp |= (0x1 << 13);

tmp &= ~(0x7f << 0);

tmp |= (88 << 0);

CCM_ANALOG->PLL_ARM = tmp;

CCM->CCSR &= ~(1 << 2); // ARM PLL 528M

//PLL2 pfd0~3 352-27 594-16 400(396)-24 200-48

tmp = CCM_ANALOG->PFD_528;

tmp &= ~((0x3f << 0) | (0x3f << 8) | (0x3f << 16) | (0x3f << 24));

tmp |= ((27 << 0) | (16 << 8) | (24 << 16) | (48 << 24));

CCM_ANALOG->PFD_528 = tmp;

//PLL33 pfd0~3 720-12 540-16 508.2-17 454.7-19

tmp = CCM_ANALOG->PFD_480;

tmp &= ~((0x3f << 0) | (0x3f << 8) | (0x3f << 16) | (0x3f << 24));

tmp |= ((12 << 0) | (16 << 8) | (17 << 16) | (19 << 24));

CCM_ANALOG->PFD_480 = tmp;

//AHB_CLK_ROOT 132M

tmp = CCM->CBCDR;

tmp &= ~(0x7 << 10);

tmp |= (0x2 << 10);

tmp &= ~(0x1 << 25);

tmp &= ~(0x3 << 8);

tmp |= (0x1 << 8); //IPG_PODF 1/2 66M

CCM->CBCDR = tmp;

tmp = CCM->CBCMR;

tmp &= ~(0x3 << 18);

tmp |= (0x2 << 18);

CCM->CBCMR = tmp;

//PERCLK_CLK_ROOT 66M

CCM->CSCMR1 &= ~(0x7f << 0);

clk_gate_allenable();

}三、定时器相关

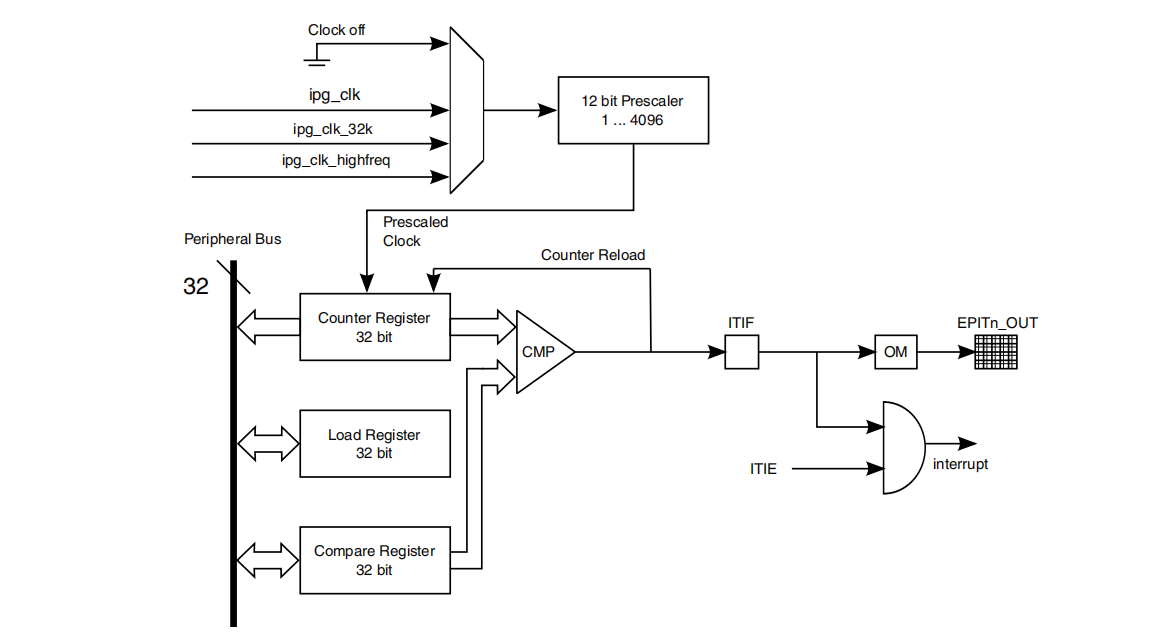

EPIT:Enhanced Periodic Interrupt Timer(增强型周期性中断定时器)

向下递减

就是芯片里一个专门用来定时、产生中断的外设

- Counter Register (32bit) :32 位倒计时计数器,你标注的

100就是它的初始值,会在每个预分频时钟 沿减 1,直到减到0。- Load Register (32bit) :32 位重载寄存器,你标注的

10是它的值。当计数器减到0时,会自动把这个值重新加载到计数器,开始下一轮倒计时。- Compare Register (32bit) :32 位比较寄存器,通常设为

0,当计数器值等于比较值时触发比较事件。- Prescaled Clock:经过分频后的时钟,是计数器递减的驱动节拍。