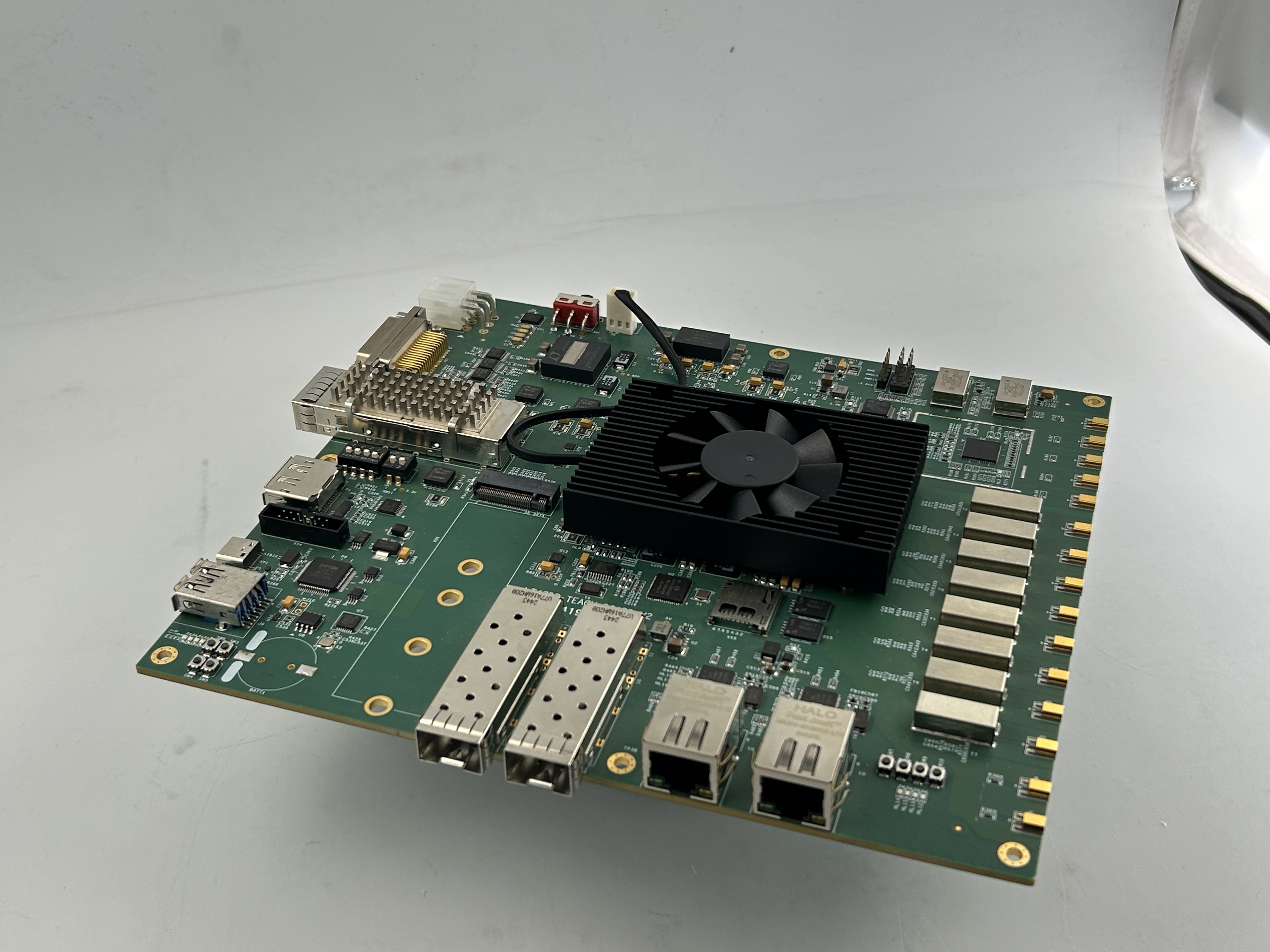

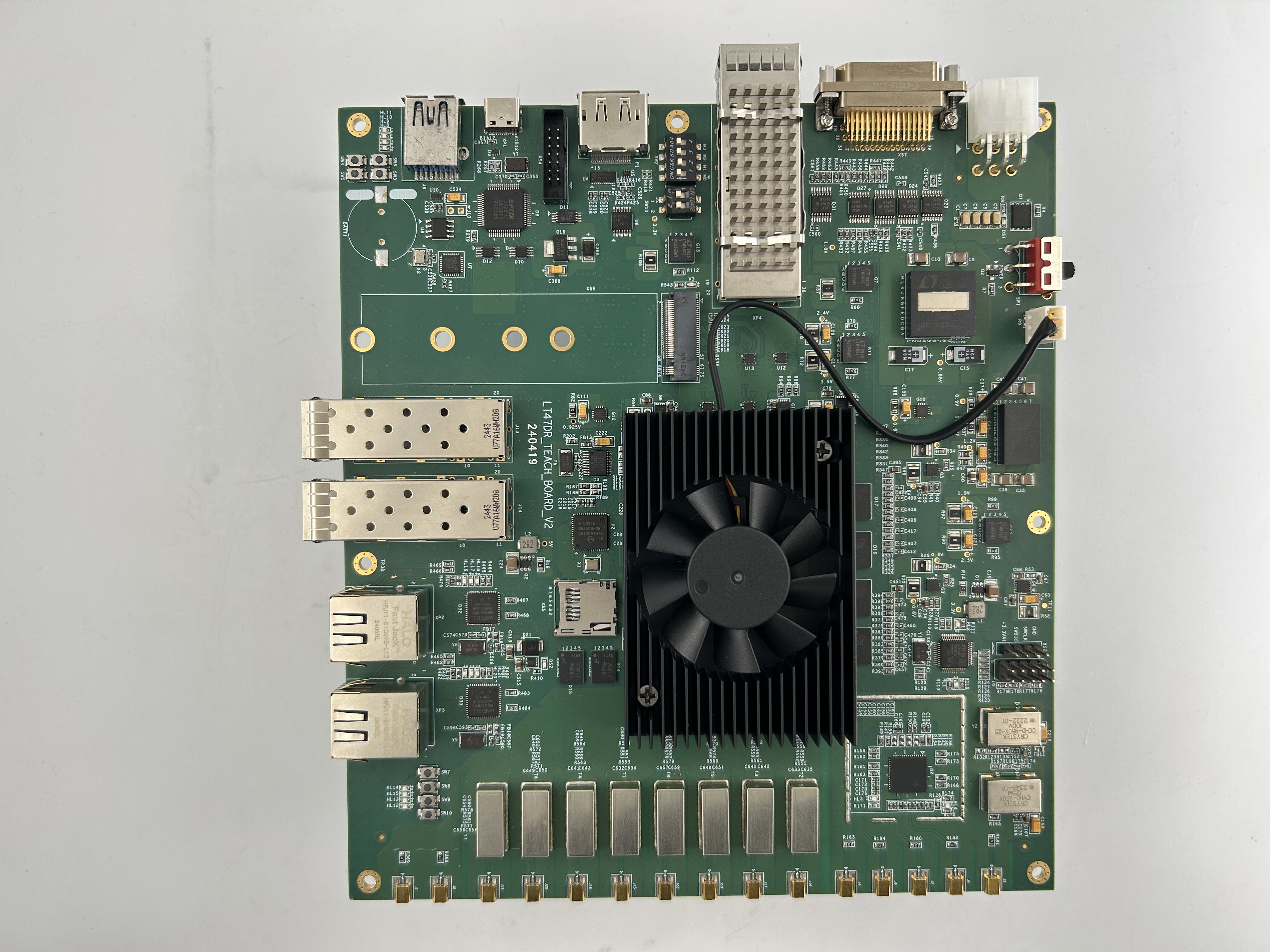

核心特性:

主控芯片:Zynq UltraScale+ RFSoC XCZU47DR

射频架构:4发4收,射频直采

模拟带宽:6.0 GHz

ADC采样率:5 GSPS

DAC采样率:9.85 GSPS

可编程逻辑资源:930K LUT

DSP资源:4272个DSP Slice

数字变频:内置可编程硬件DUC(数字上变频)和DDC(数字下变频)模块

板载接口与资源:

高速光口:2× 10G SFP+,1× 100G QSFP28

存储接口:1× NVMe(支持高速固态硬盘)

网络接口:PS端千兆以太网、PL端千兆以太网

串行通信:RS422、RS485、RS232

通用I/O:GPIO

配套资料:提供技术文件、参考工程、驱动程序

适用于射频直采、软件无线电、雷达、5G通信等高性能应用场景。