增强型周期中断定时器

set-and-forget(设置即忘)

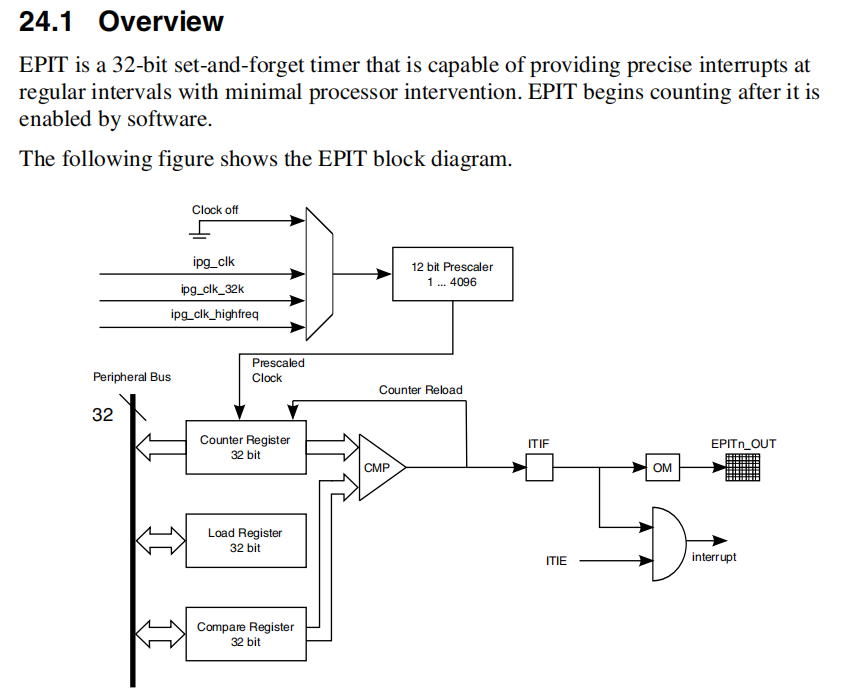

是嵌入式硬件的核心设计理念,指开发者只需在初始化阶段完成时钟、分频、计数周期、中断等关键参数的一次性配置,启动后硬件便会自动循环执行计数、比较、触发与重载的完整流程,全程无需 CPU 反复干预或重设参数,仅在中断触发时才需要响应,以此解放 CPU 资源、提升系统效率。

在上图的例子便是在计数寄存器counter register和load register,假设counter register和load register里面都是100,开始计数之后,counter register就会开始递减,当counter register减到0之后,load register里面的100便会装进去,然后再重新开始计数。

(counter register的计数频率便是分频过后的)

而compare register是比较寄存器,当counter register中的数字减到跟其相等的时候便产生一个中断信号。

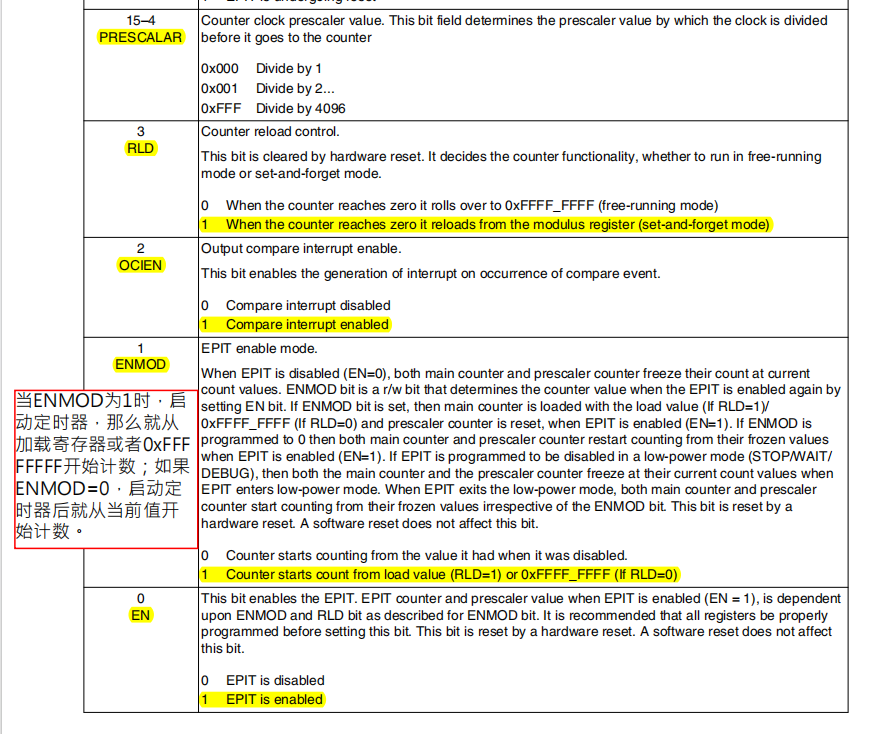

freerunning(自由运行模式)

是定时器 / 计数器的一种典型工作模式,指计数器在启动后会持续自动计数,不受单次匹配或溢出事件的终止影响,仅在硬件复位或软件停止时才会结束计数。

以 EPIT 为例,在自由运行模式下,计数器从初始值开始递减计数,计数到 0 后不会停止,而是自动重载加载寄存器的预设值,继续循环执行递减计数流程,始终保持连续的计时状态,无需 CPU 干预即可实现永久周期性的定时触发,常被用于系统节拍、任务调度等需要持续稳定计时的场景。

以上图为例,当counter register从100减到0之后,便从0xffff开始继续减。

配置寄存器

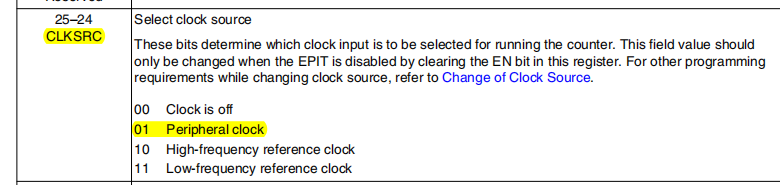

EPITx**_CR配置**

cpp

unsigned int tmp = EPIT1->CR;

tmp &= ~(0x3 << 24);

tmp |= (1 << 24);

tmp |= (1 << 17);

tmp &= ~(0xfff << 4);

tmp |= (65 << 4);

tmp |= (1 << 3);

tmp |= (1 << 2);

tmp |= (1 << 1);

EPIT1->CR = tmp;EPITx**_LR**

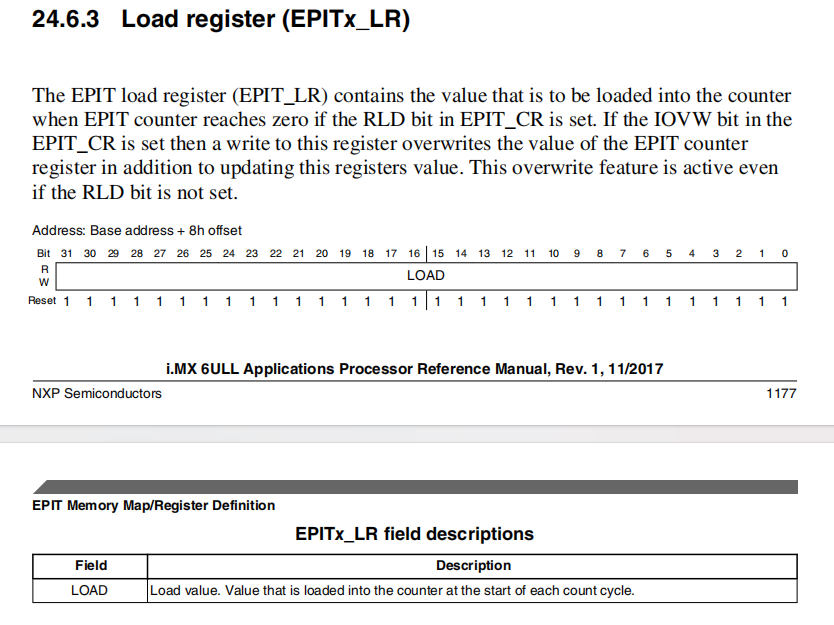

EPIT 加载寄存器(EPITx_LR)用于存储计数器重载值 ,是 EPIT 实现周期性计数的核心配置寄存器,地址偏移为0x8h,复位值为0xFFFFFFFF。

EPITx**_CMPR**

EPIT 比较寄存器(EPITx_CMPR)是 32 位寄存器,用于存储计数匹配阈值,是触发中断或输出信号的核心判断依据。

在计数过程中,硬件会实时比对计数寄存器(CNT)与CMPR中的数值:

当两者相等时,会触发比较匹配事件,硬件自动置位中断标志位(ITIF),若中断使能位(ITIE)已开启,则向处理器发送定时中断;

同时匹配信号可通过输出模式模块(OM)从EPITn_OUT引脚输出,用于触发外设或生成波形

EPIT 计数寄存器(EPITx_CNR)

EPIT 计数寄存器(EPITx_CNR)是 32 位只读寄存器,用于实时记录当前递减计数的剩余计数值,是定时器计数状态的直观体现。

上述寄存器根据具体情况配置

配置中断函数

cpp

void system_irq_handler(IRQn_Type irq_num)

{

if (irq_num == GPIO1_Combined_16_31_IRQn)

{

if (GPIO1->ISR & (1 << 18))

{

led_on();

beep_on();

GPIO1->ISR |= (1 << 18);

}

}

}