目录

[硬件描述语言(Hardware Description Language,HDL)](#硬件描述语言(Hardware Description Language,HDL))

[Verilog HDL语言程序段范例](#Verilog HDL语言程序段范例)

[Verilog HDL与其他HDL的差异](#Verilog HDL与其他HDL的差异)

[Verilog HDL发展史](#Verilog HDL发展史)

[Verilog HDL与PLD设计](#Verilog HDL与PLD设计)

[Verilog HDL基本要素](#Verilog HDL基本要素)

[PLD vs. ASIC](#PLD vs. ASIC)

[PLD vs. MCU/CPU/DSP](#PLD vs. MCU/CPU/DSP)

[CPLD vs. FPGA](#CPLD vs. FPGA)

逻辑设计概念及Vivado基础

数字量与数字电路

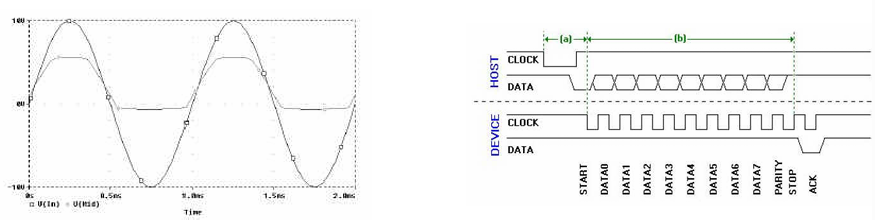

模拟信号与数字信号

- 连续变化的变量为模拟量,离散取值的变量为数字量

- 自然界绝大多数物理量都是模拟量,如温度、湿度、语音等

- 数字量可以被用来近似表示出模拟量

- 数字系统用高低电平构成二进制数系统处理信号

数字电路系统的优点

保真度高(结果再现性强)

- 易存储、易传输、高精度

- 抗噪声、受环境影响小

易于设计,EDA支持强

- 灵活性和功能性

- 可编程性

处理速度快

经济性

数字电路及其设计技术的发展

数字系统的发展

- 门电路和触发器

- 集成电路

- 可编程逻辑器件和超大规模专用集成电路

数字系统设计技术的发展

- 公式法/卡诺图化简

- 计算机辅助设计

硬件描述语言(HDL)

软件综合与仿真

硬件编程语言(HDL)概述

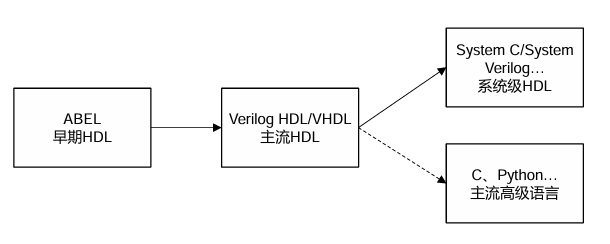

硬件描述语言(Hardware Description Language,HDL)

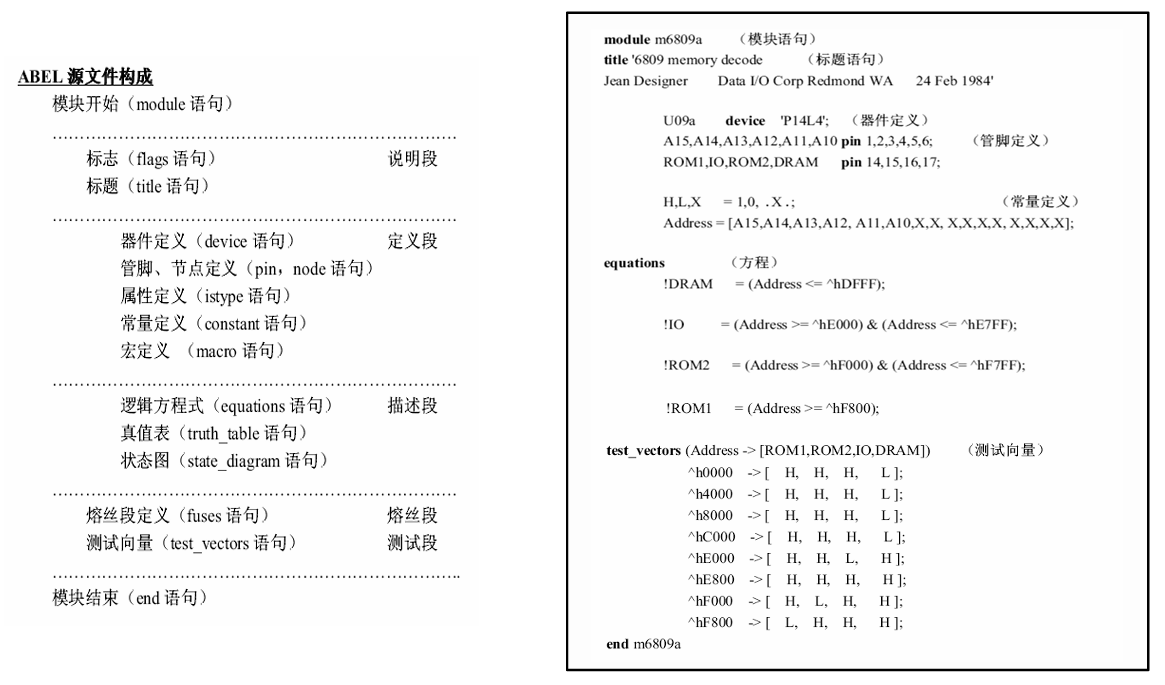

ABEL语言程序段示例

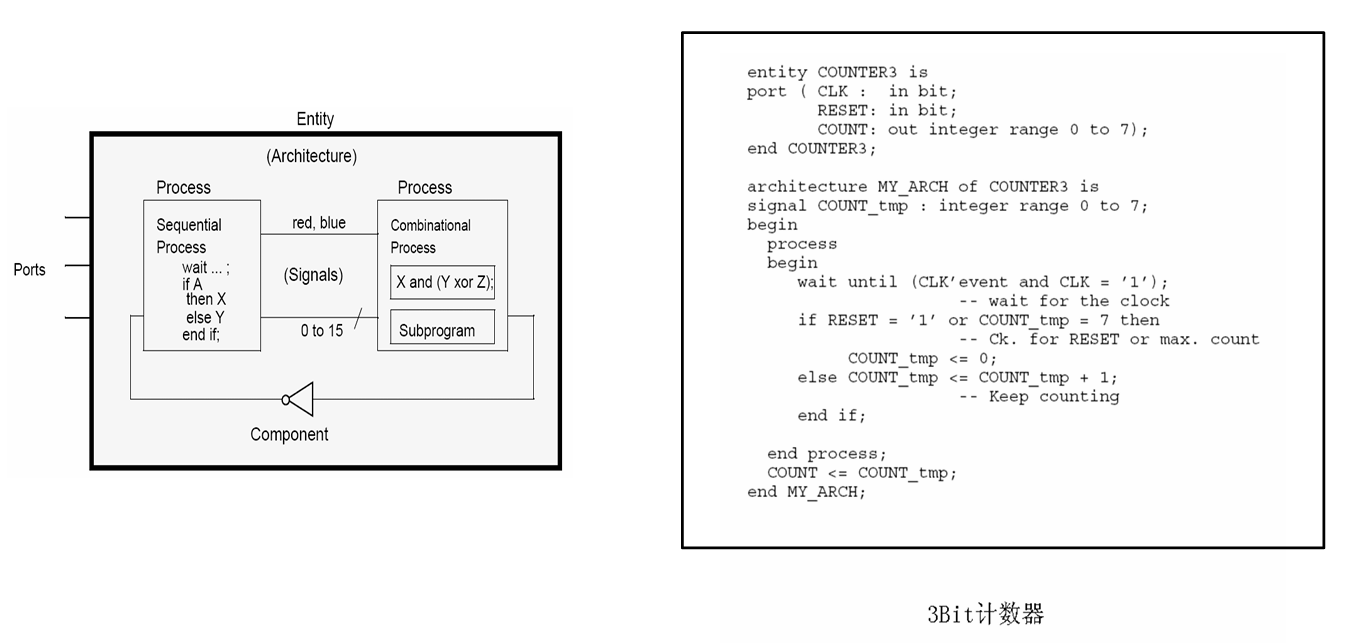

VHDL语言程序段示例

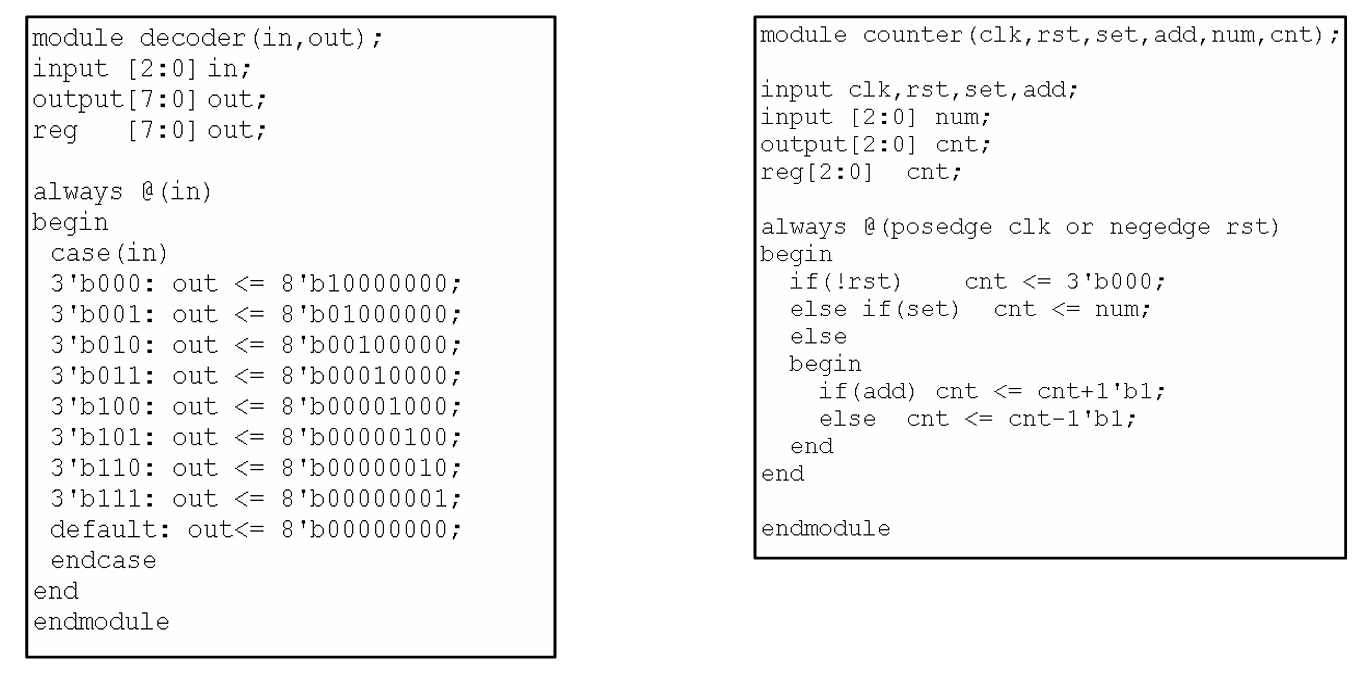

Verilog HDL语言程序段范例

Verilog HDL与其他HDL的差异

与ABEL等早期语言相比

- 上述语言多应用逻辑等式来描述逻辑功能,侧重于结构描述方法

- Verilog HDL适合算法级、寄存器传输级(RTL)、门级、版图级等各类设计描述应用

与VHDL等同期语言相比

- 两者都具备良好的行为描述能力

- 一般认为,Verilog HDL在描述硬件单元的结构时更简单易读,相比较而言,VHDL的描述长度通常是Verilog HDL的两倍

Verilog HDL发展史

Verilog HDL 语言最初于1983年由Gateway Design Automation (GDA) 公司 为其模拟器产品开发的硬件建模语言

Cadence 在1989年收购GDA后,Verilog HDL语言于1990年正式对外发布

Open Verilog International ( OVI )成立,以促进Verilog语言规范的发展

1993年,OVI推出了2.0版本

Verilog语言于1995年成为IEEE标准,称为IEEE Std1364-1995,2001年 又更新了一版标准

Verilog HDL与PLD设计

PLD设计是Verilog HDL的一大应用

PLD设计仅支持Verilog HDL的一个子集

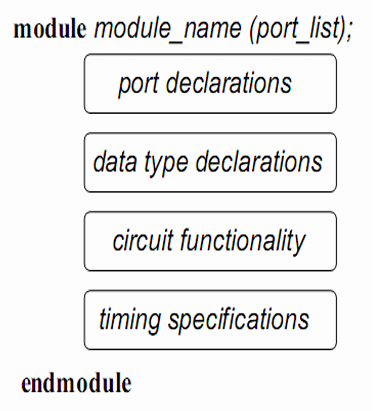

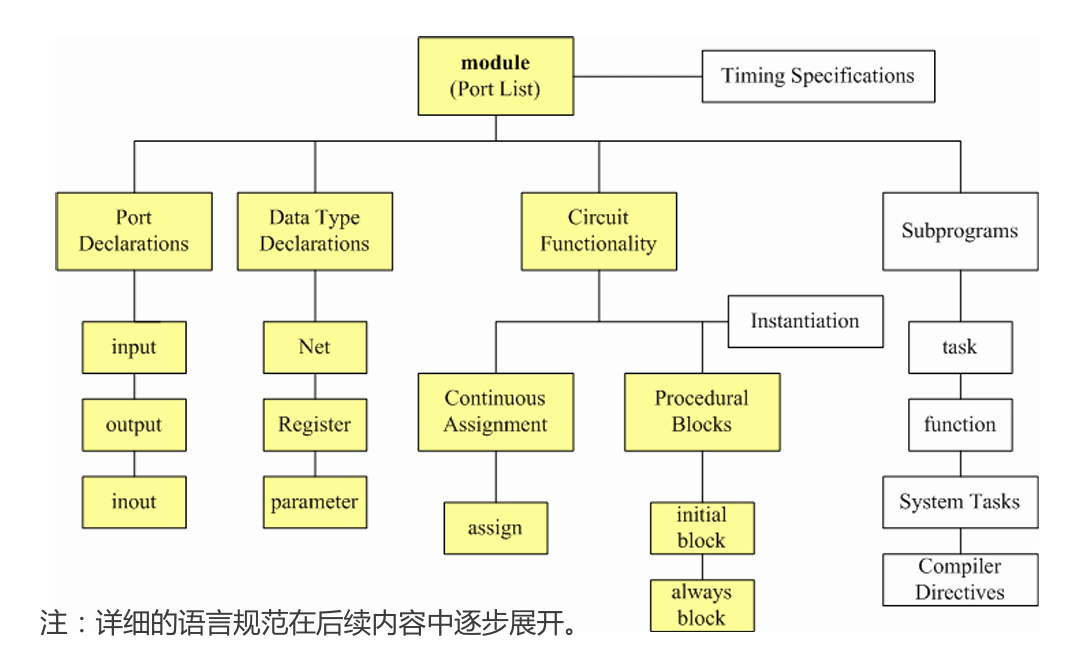

Verilog HDL基本要素

注意点:

- 大小写敏感

- 所有关键字须小写

- 空格用于增加可读性

- 分号是语句终结符

- 单行注释://

- 多行注释:/* */

- 时间规范用于仿真

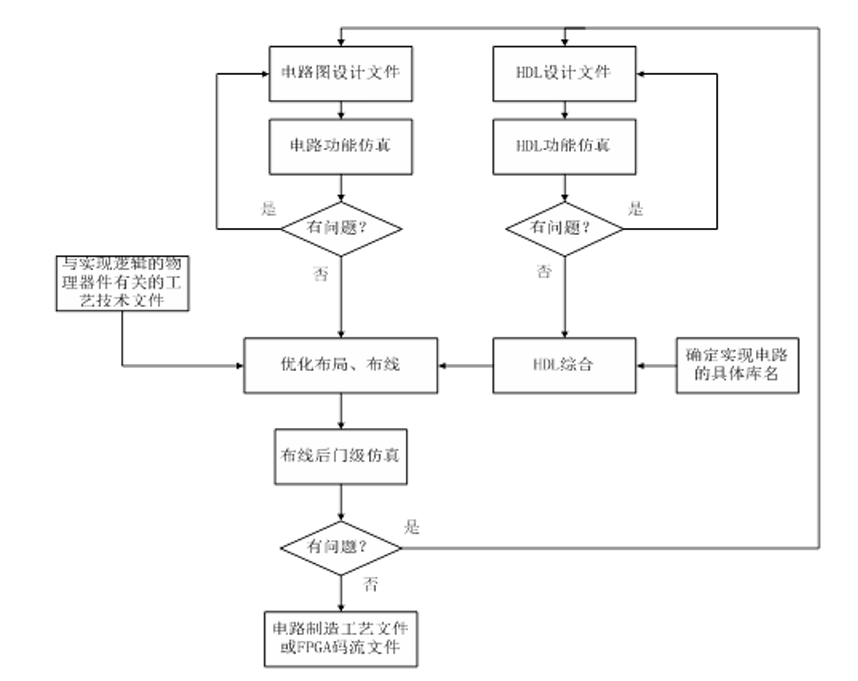

逻辑电路与系统设计流程

可编程逻辑器件基础

可编程逻辑器件概述

PLD:Programable Logic Device 可编程逻辑器件

- 可编程:执行功能"可且必须"由用户定制

- 逻辑:属于逻辑电路,不同于模拟电路

- 器件:以单独芯片形式封装和形成产品

PLD可实现通用逻辑功能设计的原理

- "与或非门+寄存器"的基本逻辑单元组合

- PLD可提供丰富的基本逻辑单元和连线资源

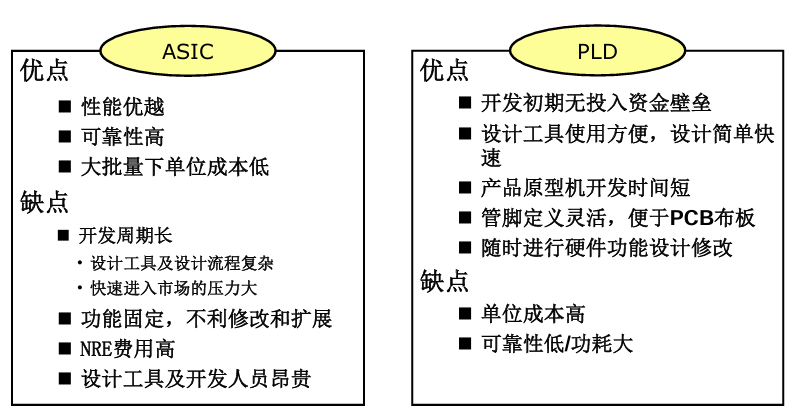

PLD vs. ASIC

PLD vs. MCU/CPU/DSP

PLD(CPLD/FPGA)开发模式的特点

- 以硬件藐视语言(HDL)或电路图作为主要开发手段

- 程序中不同的逻辑功能被设计成不同的硬件模块并存

- 高速、设计灵活性好

- 从功能角度可完全取代CPU式开发模式

CPU(MCU/CPU/DSP)开发模式的特点

- 以C语言等为主的高级语言作为主要开发手段

- 微程序模式,程序被分解后依次在同一硬件系统中执行

- 成本低、功耗小

PLD的发展史

PLD雏形:PROM/EPROM

第一代PLD(二十世纪70年代)

PLA / PAL

第二代PLD(二十世纪80年代)

GAL

第三代PLD(二十世纪90年代起)

CPLD

FPGA

其它衍生PLD产品:结构化ASIC、ASSP等

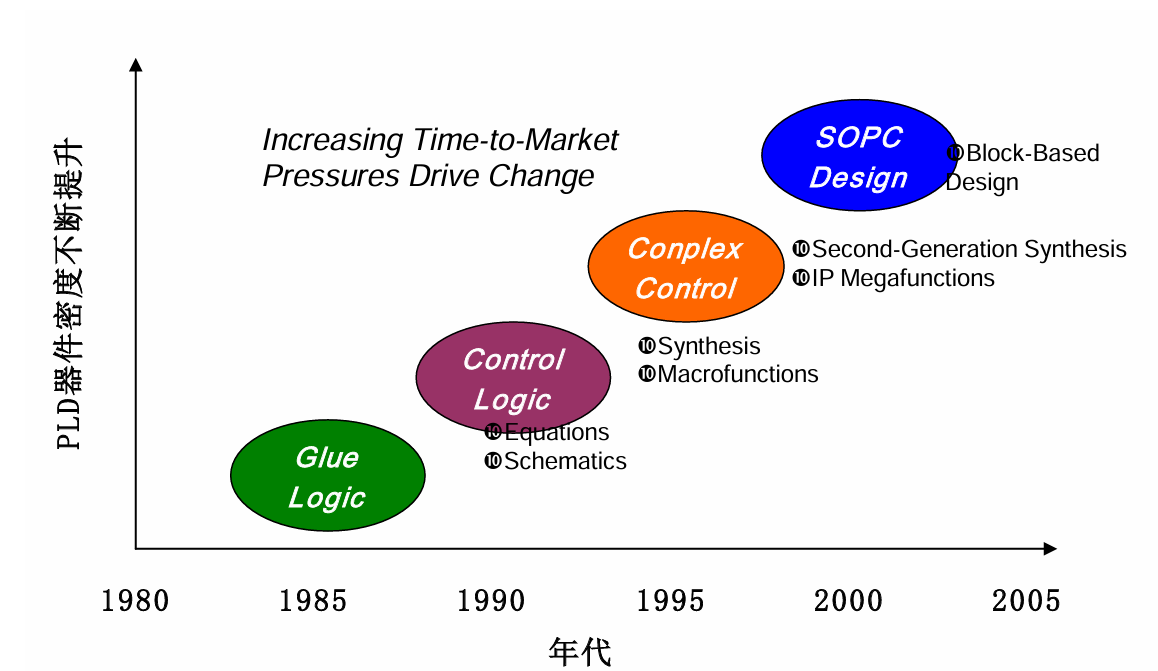

PLD的发展步伐

从一次烧写发展到可反复烧写

不断增加可编程逻辑资源的集成度

单元逻辑资源的成本和价格不断降低

由传统可编程逻辑资源集成扩展更多IP

HDL的不断成熟(标准化)和进化

设计和仿真EDA技术越来越成熟

建立向ASIC转化的方案

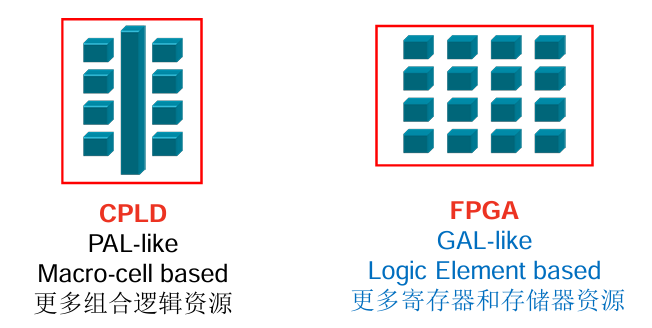

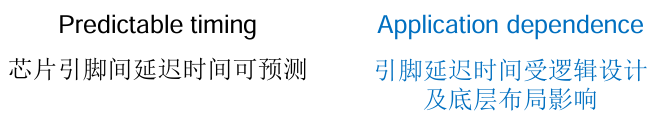

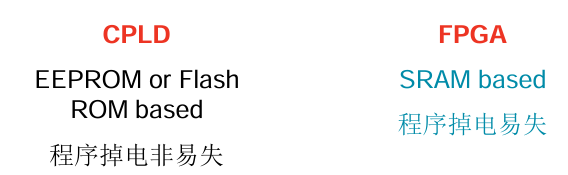

CPLD vs. FPGA

CPLD:Complex Programmable Logic Device

FPGA:Field Programmable Gate Array

传统CPLD与FPGA技术对比

- 结构对比

- 资源容量对比

- 性能对比

- 程序易失性对比

- 下载模式对比

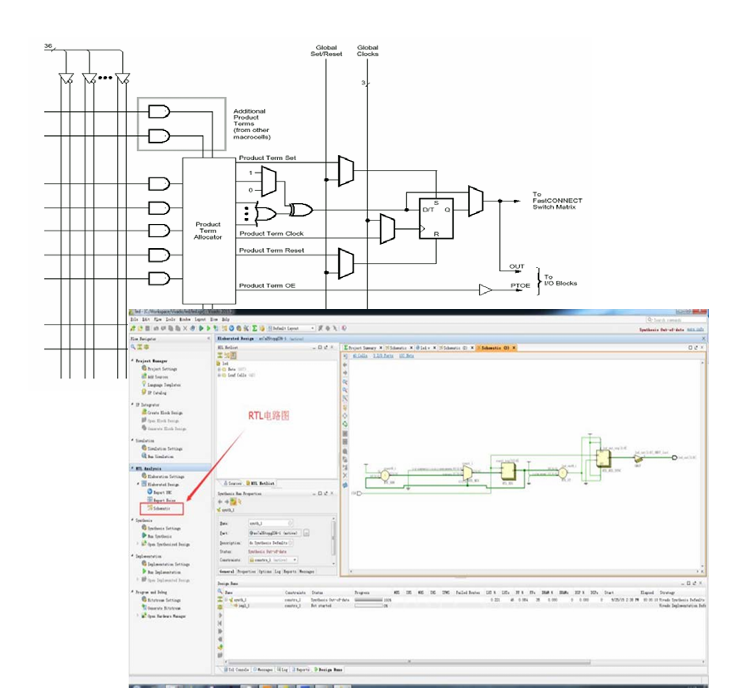

典型CPLD内部架构

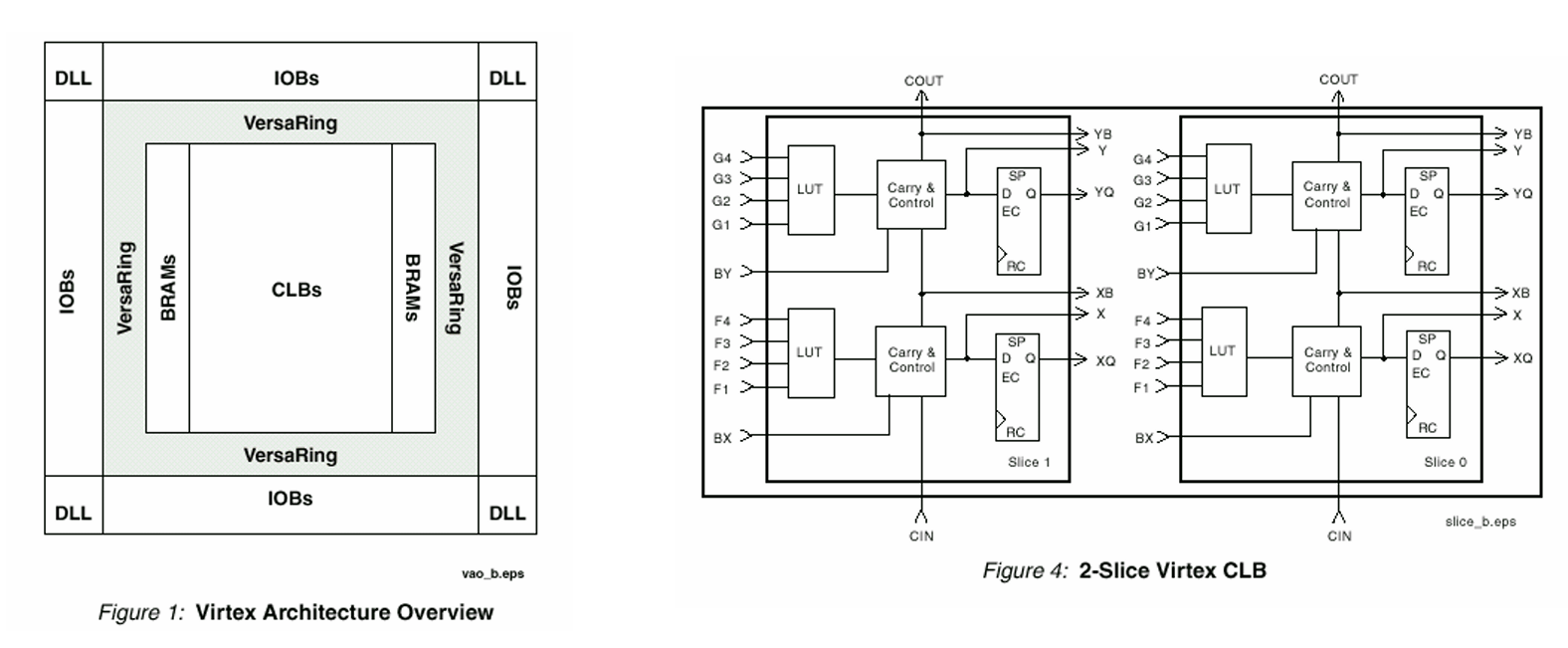

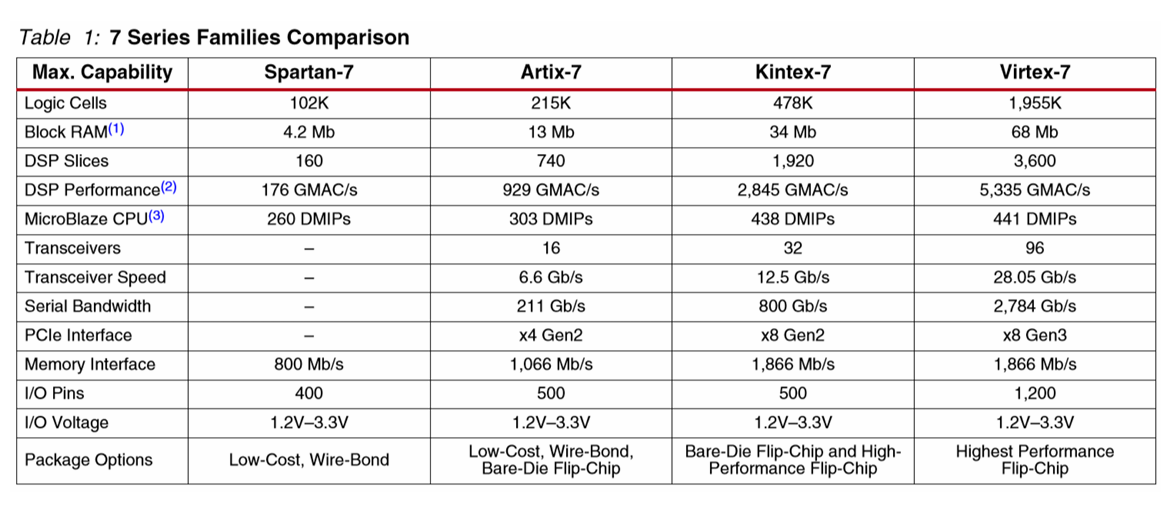

典型FPGA内部架构

发展中的新CPLD/FPGA概念

新CPLD/FPGA产品

- 新CPLD产品基于LE和非单一总线构架

- 新FPGA产品具有掉电非易失特性

目前区分CPLD/FPGA的主要标准

- CPLD主要是逻辑资源较少、配置方式单一、具备掉电非易失特性的PLD产品, 通常内部仅含传统可编程逻辑资源及少量存储器

- FPGA在集成大量可编程逻辑资源的基础上通常包含大量PLL、RAM、多功 能I/O等资源

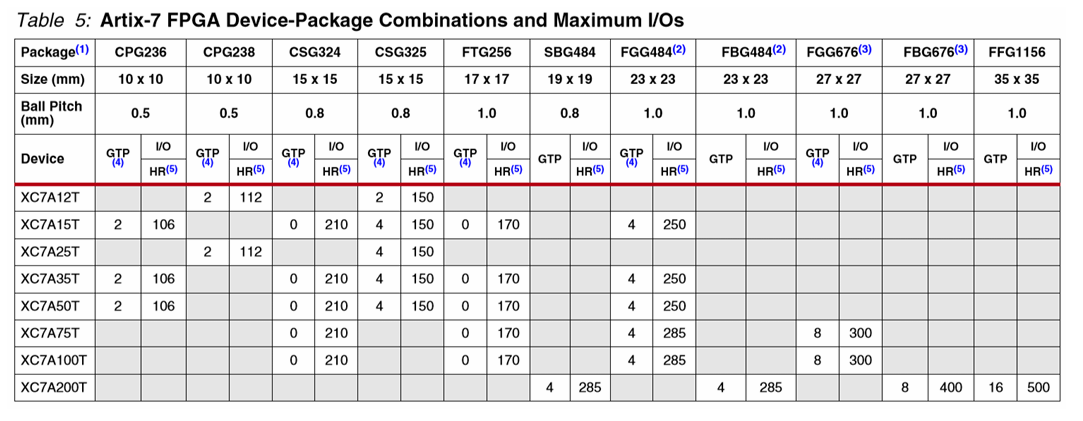

Xilinx公司主流7系列FPGA产品

FPGA芯片选型

选型考虑因素

- 管脚数量(IO)

- 逻辑资源

- 片内存储器

- DSP资源

- 功耗

- 封装

PLD设计方法的演变

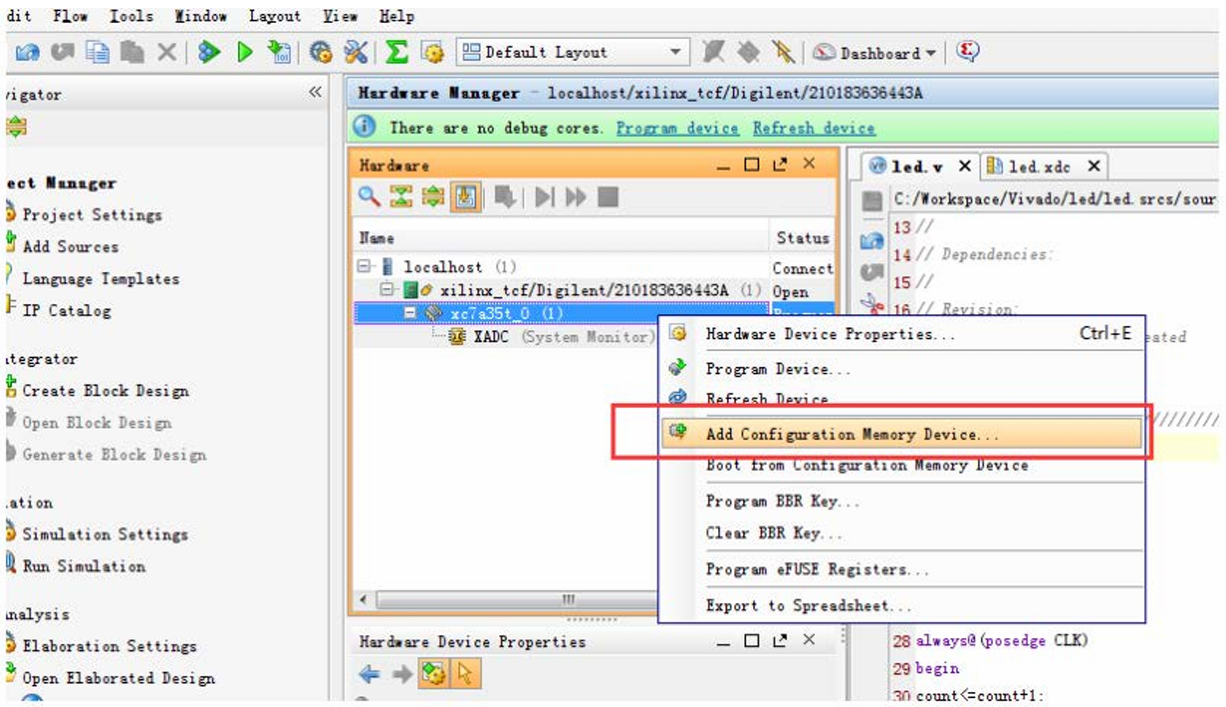

Vivado开发环境及流程演示

Vivado综合开发环境功能介绍

Vivado 是Xilinx公司基于其FPGA产品进行开发设计的综合开发环境,集成文本编辑器 、逻辑函数库、编译/布线/仿真工具、下载器等功能;

相比较原来的 ISE综合开发环境,主要特点在于:

-- 支持Xilinx公司新一代(7系列、28nm以下工艺器件)可编程逻辑器件;

-- 整合高层次综合(HLS)、高级语言编译等功能;

-- 支持IP库自定义封装;

-- 增量式工程变更管理,编译速度提升。

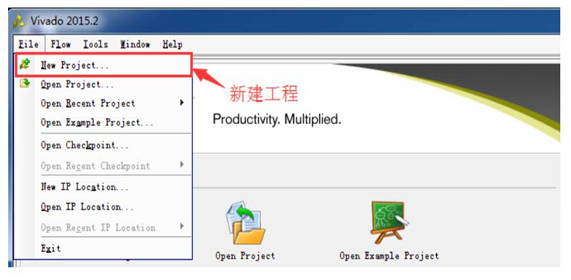

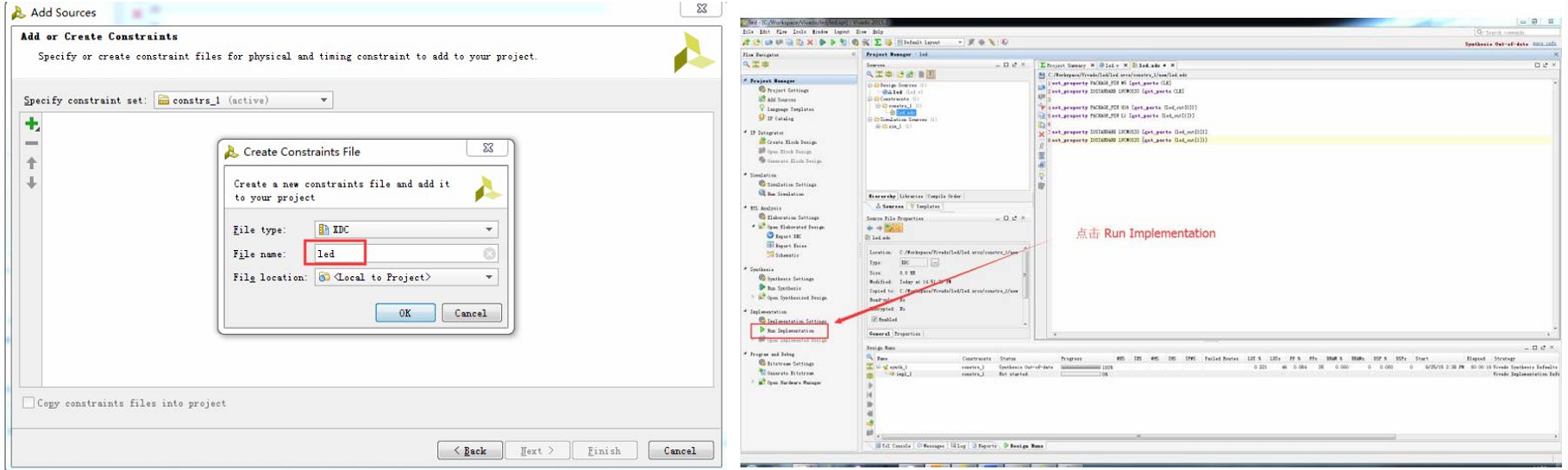

一、启动Vivado,新建工程

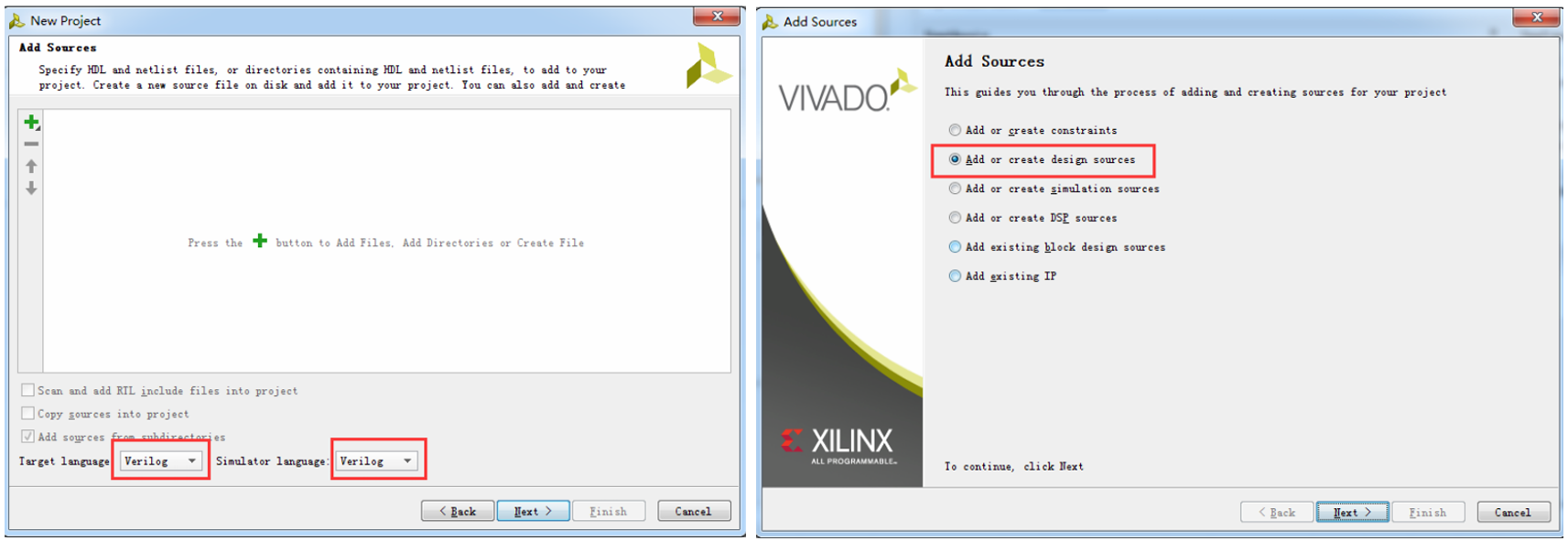

二、利用向导,新建项目,语言选择为Verilog,亲戚间选择与平台相关的,新建Verilog HDL文件

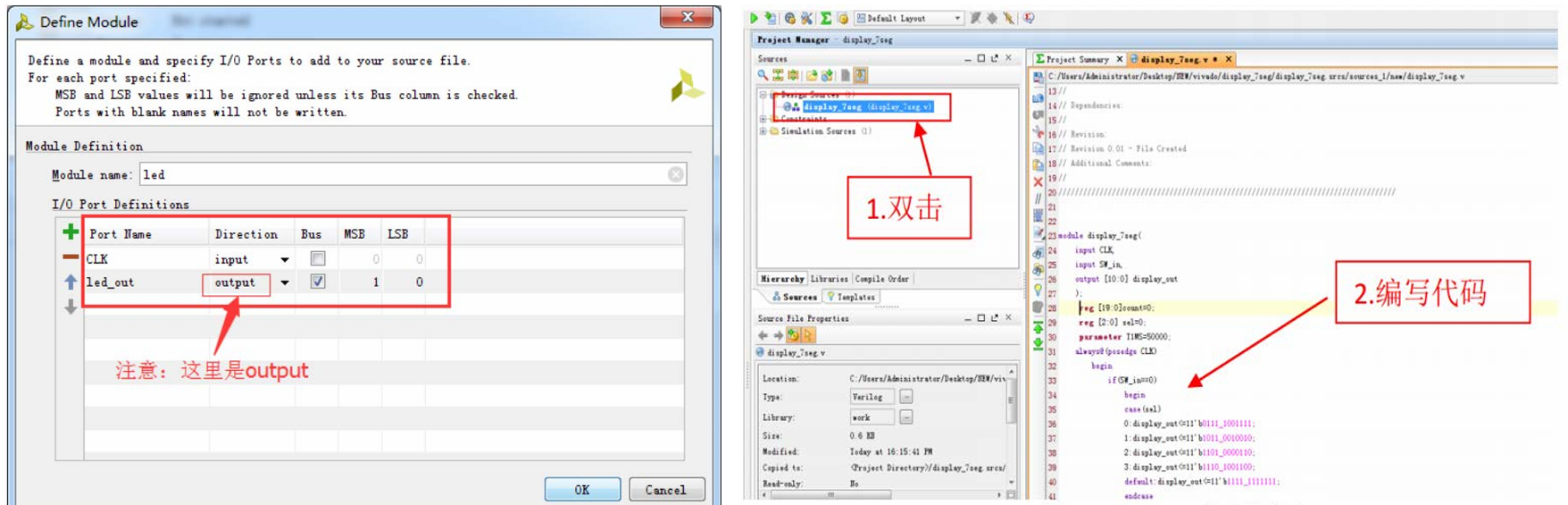

三、填写模块名称和端口,文件窗口区编写代码

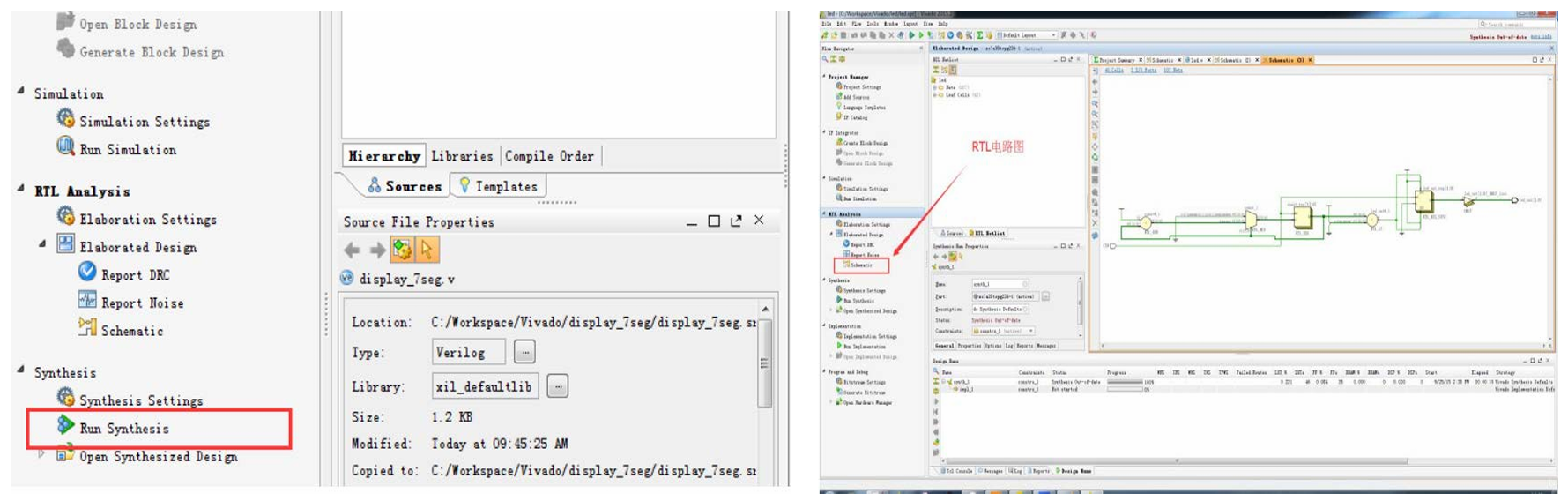

四、Vivado程序编译,查看RTL级电路

五、分配引脚,运行代码

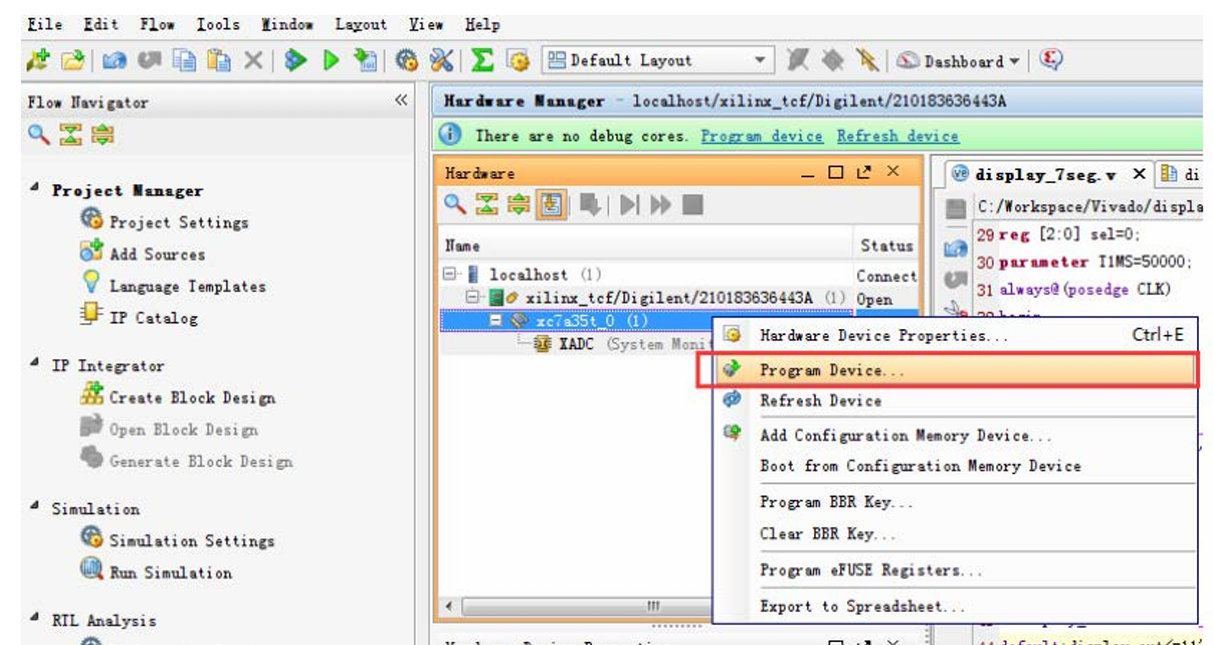

六、连接电脑下载演示

七、ROM烧写,掉电不丢失