【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

hls的开发虽然比较方便,但是本质上hls转成一个ip,还是需要c翻译成verilog的。所以从这个角度上来说,c语言就是一个中介。只是因为用c语言的人比较多,所以hls选择了c/c++作为开发的基础语言。就像android开发的话,选择java是一个道理。

verilog说简单也简单,主要是和c的思维不太一样,它的驱动就是clk,起始点就是reset。

1、最简单的verilog,就是clk、rst和led

最简单的verilog,其实就类似于c语言里面的hello world,它有时钟,有复位,有输出。这就是一个最小工程了。

2、状态机的引入

如果只是写一些led程序,基本照着verilog语法写就可以了。但是需要处理一些协议的话,就需要引入状态机,比如串口。不管什么接口,首先拆分成不同的状态,这样不同的信号在不同状态下的逻辑,就可以慢慢写出来了。

3、输入去抖

有了输出,还要有输入。而输入最简单的信号就是按键输入,然而输入的key一般是机械装置,这个时候就要引入防抖算法。这部分,可以借助于之前谈到的状态机,就可以轻松解决。

4、开始输出时钟

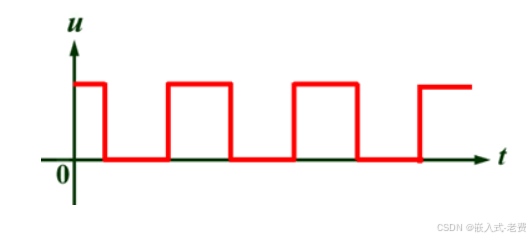

有一些协议不管是信号的输入、输出,有时候还需要输出时钟。对于低速的时钟,不需要pll倍频。直接使用verilog的输入时钟,分频处理就可以了,最典型的就是iic时钟、spi时钟。有了前面的输入、输出,再加上本次提到的时钟输出,就可以和外界芯片通信处理了,非常有效。

5、pll倍频

除了低速接口,还有一些高速接口需要处理,比如说vga、比如说sdram。这些接口的速率都比fpga的输入时钟要高。所以没办法,处理这些信号就有必要引入pll倍频ip。好在不管是altera,还是xilinx,本身eda都提供了对应的ip,直接拖过来使用即可。

6、引入fifo解决频率差异问题

既然模块倍频了,那么肯定会出现不同频率模块需要进行相互通信的case。最典型的就是图像处理的场景。一方面是图像采集的速度,一方面是图像播放的速度。为了解决速度差的问题,一般先把图片放到ddr,然后再从ddr送出去。由于ddr处理速度非常快,所以采集速度、ddr速度、播放速度都不一样。这个时候就引入fifo就可以完美解决这一问题,一个是read fifo,一个是write fifo。

7、延迟打拍

这一招在图像处理的时候经常需要用到的。比如采集到的图像需要做某个算法,或者是做某个统计值,这个时候就可以采用延迟打拍的方法来处理。比如说,最简单的就是把彩色的图像,转成黑白的图像,此时只需要把所有图像延迟几拍即可。

8、与mcu或者mpu协作

有一些功能用fpga来做并不是很合适,比如纯文件系统处理,或者是纯网络系统处理。这个时候就适合旁边接一个小mcu,或者是mpu,通过spi连接,获取fpga送过来的数据、信号、甚至是图片,这都是很合适的方式。

当然fpga的优势,还是在中高速接口、多接口、算法领域使用,比较合适。