目录

[1 中断流程核心步骤](#1 中断流程核心步骤)

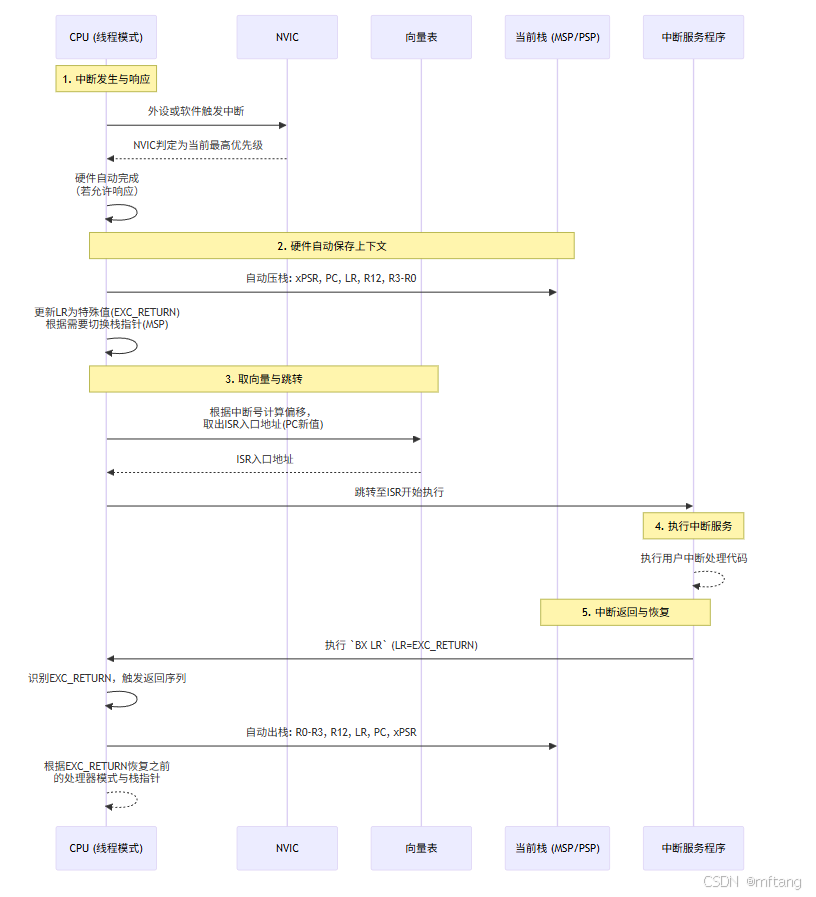

[1.1 中断跳转流程框图](#1.1 中断跳转流程框图)

[1.2 步骤详解](#1.2 步骤详解)

[1.3 关键机制与调试要点](#1.3 关键机制与调试要点)

[2 RTOS配置优先级以优化任务调度](#2 RTOS配置优先级以优化任务调度)

[2.1 配置优先级原则](#2.1 配置优先级原则)

[2.2 配置详解与代码实现](#2.2 配置详解与代码实现)

[3 EXC_RETURN 各个位的具体含义](#3 EXC_RETURN 各个位的具体含义)

[3.1 EXC_RETURN 位字段详解](#3.1 EXC_RETURN 位字段详解)

[3.2 常见EXC_RETURN值及其行为解析](#3.2 常见EXC_RETURN值及其行为解析)

概述

Cortex-M的中断跳转是其实时性 的核心保障,整个过程绝大部分由硬件自动完成 ,确保了极低且确定的中断延迟。其内部原理可以概括为:硬件自动保存现场、硬件自动查找跳转地址、执行中断服务程序、硬件自动恢复现场。

1 中断流程核心步骤

1.1 中断跳转流程框图

1.2 步骤详解

1) 中断触发与响应

外设或软件设置中断挂起位。

NVIC 比较该中断与当前CPU优先级,若其更高,则CPU会在当前指令边界挂起当前任务,准备响应。

2) 硬件自动保存上下文

CPU将8个寄存器 自动压入当前活动堆栈 (MSP或PSP):

xPSR,PC,LR,R12,R3-R0。此操作对于C语言程序员完全透明,是中断延迟的主要部分。将返回地址和模式信息编码成一个特殊值(

EXC_RETURN)存入LR寄存器。处理器模式切换为Handler模式 ,并强制使用MSP作为栈指针。

3) 取向量与跳转

CPU根据中断号(如IRQ#10)计算出在向量表中的偏移量。

从向量表对应位置(如

0x08000000 + 4 * (16 + 10))取出中断服务程序的入口地址,加载到PC寄存器。程序随即跳转到 ISR 开始执行。

- 中断服务与返回

执行用户编写的ISR代码。

ISR末尾通常是一条

BX LR指令。此时LR中的EXC_RETURN值告知硬件这是一个异常返回,而非普通函数返回。

- 硬件自动恢复上下文

硬件识别

EXC_RETURN,启动返回序列:将步骤2中压栈的8个寄存器自动弹出,恢复到CPU。关键的

PC被恢复,CPU因此返回到被中断的原程序流。根据

EXC_RETURN的值,处理器模式切换回之前的模式 (线程模式),并恢复之前使用的栈指针(MSP或PSP)。

1.3 关键机制与调试要点

- 向量表

位于内存起始(如

0x08000000)的地址数组。第一个字是MSP初始值,第二个是复位向量,后续便是中断向量。链接脚本和启动文件负责其正确放置。

- EXC_RETURN

一个形如

0xFFFFFFFX的魔值,其低位编码了返回时应使用的栈指针(MSP或PSP)和处理器模式。这是硬件自动化的调度指令。

- 嵌套中断

如果高优先级中断打断了低优先级ISR,硬件会再次自动保存上下文,形成嵌套。NVIC的优先级管理确保了确定性的嵌套行为。

- 性能保障

整个压栈、跳转过程通常只需12个时钟周期(Cortex-M3/M4),这种确定性是实时系统的基石。

2 RTOS配置优先级以优化任务调度

2.1 配置优先级原则

在RTOS(如FreeRTOS)中,优化任务调度的核心中断配置原则是:将SysTick设置为"次高优先级",将PendSV设置为"最低优先级"。这一经典配置是保障系统实时性与调度稳定性的基石。

下表对比了这两个关键异常的典型配置与作用:

| 异常 | 典型优先级配置 | 核心职责 | 优先级设计的原理与系统行为 |

|---|---|---|---|

| SysTick | 次高优先级 (例如 2) | 提供系统节拍,触发任务时间片检查与调度请求。 | 1. 确保准时 :能抢占大部分用户任务和中断,保证节拍准确。 2. 避免阻塞高优先级中断 :优先级低于关键硬件中断(如通信),保证其实时性。 3. 快速退出 :仅标记调度需求并挂起PendSV,不立即切换任务,处理极其迅速。 |

| PendSV | 最低优先级 (例如 15或255) | 执行实际的上下文切换。 | 1. 作为"惰性"上下文切换器 :等待所有更高优先级中断(包括SysTick)处理完毕后才执行,确保切换发生在安全、无中断嵌套 的时刻。 2. 保障实时性:避免高耗时任务切换阻塞对紧急中断的响应。 |

2.2 配置详解与代码实现

在FreeRTOS中,这一配置主要通过 FreeRTOSConfig.h 中的宏定义实现。其设计哲学是:SysTick仅触发调度请求,PendSV在安全时执行切换。

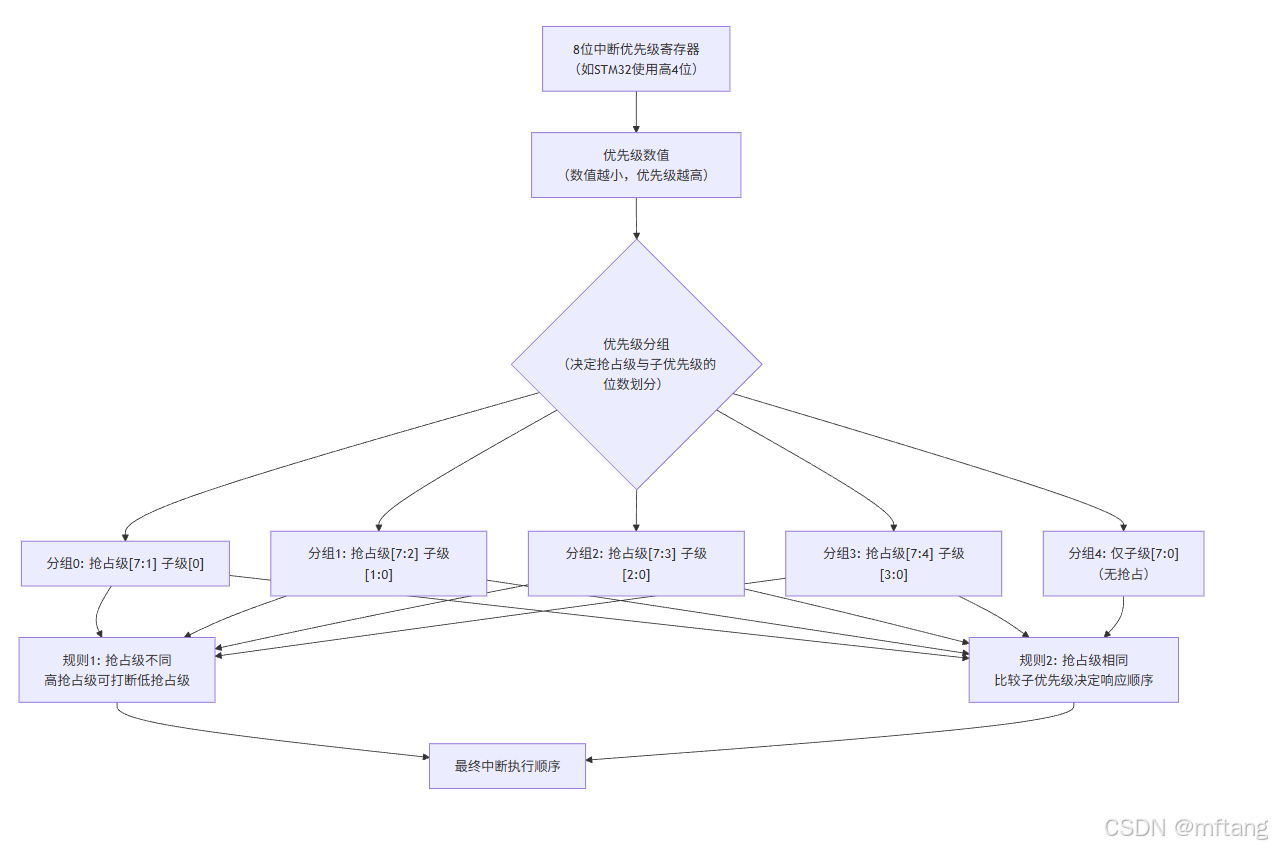

1) 优先级数值与分组设定

通常,系统使用 4位优先级分组(共16个优先级级别,0为最高,15为最低)。关键在于理解以下两个宏:

configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY:定义了可以安全调用FreeRTOS中断专用API的最高中断优先级 。例如,设置为5,意味着优先级为0-4的中断不会被RTOS延迟,它们拥有"至尊"特权;而优先级在5-15的中断,其处理函数可以安全使用xQueueSendFromISR()等API。

configLIBRARY_LOWEST_INTERRUPT_PRIORITY:定义了系统可用的最低中断优先级。PendSV和SysTick的优先级应基于此数值设置。

2) FreeRTOS中的典型配置示例

以下是基于Cortex-M3/M4(使用4位优先级)的典型配置片段:

cpp

// FreeRTOSConfig.h

// 1. 定义优先级数值 (假设使用4位,则范围0-15)

#define configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY 5 // 优先级数值 5

#define configLIBRARY_LOWEST_INTERRUPT_PRIORITY 15 // 优先级数值 15

// 2. 内核实际使用的优先级,由FreeRTOS内部根据架构计算

// (通常不需要用户直接修改,但需理解其来源)

#define configKERNEL_INTERRUPT_PRIORITY ( configLIBRARY_LOWEST_INTERRUPT_PRIORITY << (8 - __NVIC_PRIO_BITS) )

#define configMAX_SYSCALL_INTERRUPT_PRIORITY ( configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY << (8 - __NVIC_PRIO_BITS) )

// 3. SysTick和PendSV优先级在port.c中设置(以ARM_CM4为例):

// SysTick 被设置为"次高",即 configLIBRARY_MAX_SYSCALL_INTERRUPT_PRIORITY

// PendSV 被设置为"最低",即 configLIBRARY_LOWEST_INTERRUPT_PRIORITY3) 工作流程

SysTick是准时、高效的"调度发令员",而PendSV则是等待所有"重要事务"(高优先级中断)都处理完后,才上场进行"搬家工作"(上下文切换)的"勤杂工"。

基于此配置的调度流程完美体现了其设计意图:

SysTick中断发生(优先级5),它抢占低优先级任务。

SysTick中断服务例程(由FreeRTOS提供)会:

更新系统时钟。

检查任务时间片,判断是否需要调度。

若需要,则仅向NVIC挂起PendSV异常 ,而不执行任何上下文切换。

然后立即退出。

由于PendSV优先级为15(最低),此时CPU会返回到被SysTick打断的现场 。如果有任何优先级高于5但低于15的挂起中断,它们将立刻得到执行。

当所有更高优先级中断都处理完毕后,PendSV(最低优先级)才会真正执行。

PendSV处理程序执行实际的保存当前任务上下文、切换任务控制块、恢复新任务上下文等一系列耗时操作。

3 EXC_RETURN 各个位的具体含义

EXC_RETURN是ARM Cortex-M架构中用于触发和引导硬件完成异常返回流程的特殊值 。它不是普通的指令地址,而是一个由硬件根据进入异常时的处理器状态生成的"魔数"(Magic Number)。当异常返回指令(如 BX LR)执行时,CPU会检查 LR 寄存器中的值,如果其高位为全1(即属于EXC_RETURN范围),便会触发一整套硬件自动的现场恢复和状态切换操作

3.1 EXC_RETURN 位字段详解

EXC_RETURN是一个32位值,其位定义遵循特定的结构,下表清晰地展示了其位布局与含义:

| 位域 | 名称/描述 | 取值与含义 |

|---|---|---|

| 31:24 | 固定前缀 | 0xFFFFFF。高24位全为1,是识别EXC_RETURN值的标志。 |

| 23:6 | 保留 | 必须为0。 |

| 5 | S | 安全状态位 (ARMv8-M TrustZone) 。0: 返回安全状态;1: 返回非安全状态。 |

| 4 | ES | 异常连续状态位 (ARMv8-M)。与S位一同使用,指示返回前后的安全状态是否一致。 |

| 3 | Mode | 返回后模式指示 。在ARMv7-M及ARMv8-M的非基线架构中,此位指示返回后是否使用浮点上下文。0: 返回后需要恢复浮点上下文(如果使用了FPU);1: 不恢复。 |

| 2 | SPSEL | 栈指针选择位 。0: 返回后使用主栈指针(MSP) ;1: 返回后使用进程栈指针(PSP)。这是决定返回线程模式后使用哪个栈的关键。 |

| 1:0 | Mode/安全 | 组合状态位 。这是最重要的两位,决定了返回后的基本模式和安全状态。 • 0b00 : 保留。 • 0b01 : 返回Handler模式 (异常嵌套等特殊情况)。 • 0b10 : 保留。 • 0b11 : 返回Thread模式。 |

注 :对于不带浮点单元(FPU)的Cortex-M3/M0+等内核 ,或ARMv8-M Baseline架构,位3及以上的定义可能有所不同或保留,需以具体内核手册为准。

3.2 常见EXC_RETURN值及其行为解析

1) EXC_RETURN值

结合上表,我们可以解读几个在编程和调试中最常遇到的EXC_RETURN值。这些值由硬件在进入异常时自动生成并装入 LR 寄存器。

| EXC_RETURN值 | 对应二进制 (高24位省略) | 含义解析 | 典型场景 |

|---|---|---|---|

0xFFFFFFF1 |

...1111 0001 |

返回Handler模式 ,使用 MSP。 | 从异常(如SysTick)返回,但继续嵌套在另一个异常中。 |

0xFFFFFFF9 |

...1111 1001 |

返回Thread模式 ,使用 MSP。 | 复位后首次进入线程模式,或异常返回到使用主栈的裸机应用。 |

0xFFFFFFFD |

...1111 1101 |

最重要、最常见 。返回Thread模式 ,使用 PSP。 | RTOS中任务的运行环境。异常(包括PendSV)返回后,任务在其私有栈上运行。 |

0xFFFFFFE1 |

...1110 0001 |

返回Handler模式,使用MSP,且指示需要恢复浮点上下文(位3=0)。 | 在使用了FPU的异常处理之后返回。 |

0xFFFFFFED |

...1110 1101 |

返回Thread模式,使用PSP,且指示需要恢复浮点上下文。 | RTOS中使用了浮点运算的任务,在异常返回后恢复。 |

2) 对开发者与调试的意义

自动化流程 :程序元无需手动构造这些值。当CPU以某种状态(如使用PSP的Thread模式)进入异常时,硬件会自动生成对应的EXC_RETURN值并存入

LR。调试关键线索 :在调试器中,观察

LR寄存器的值,可以立即判断:

当前是否在异常处理程序中。

中断返回后将使用哪个栈(MSP还是PSP),这是判断系统状态(在RTOS内核还是用户任务中)的重要依据。

是否涉及浮点状态的保存与恢复。

安全状态指示(ARMv8-M):对于带有TrustZone的Cortex-M23/M33等,EXC_RETURN的位4和位5指明了返回后的安全世界,是硬件强制安全隔离的关键一环。