目录

[四、PCA9554A 必懂寄存器与位操作(详细、易懂)](#四、PCA9554A 必懂寄存器与位操作(详细、易懂))

[表 1:PCA9554A 关键寄存器表](#表 1:PCA9554A 关键寄存器表)

[ASCII 流程图 1:驱动调用链(应用层到 I2C 层)](#ASCII 流程图 1:驱动调用链(应用层到 I2C 层))

[六、PCA9554A_I2C_Write 逐行思路讲解(重点)](#六、PCA9554A_I2C_Write 逐行思路讲解(重点))

[七、goto + error_exit、软件锁、防重入、recover 的工程意义](#七、goto + error_exit、软件锁、防重入、recover 的工程意义)

[ASCII 流程图 2:I2C_Write 成功路径与错误收尾路径](#ASCII 流程图 2:I2C_Write 成功路径与错误收尾路径)

[表 2:错误码与含义(含触发条件)](#表 2:错误码与含义(含触发条件))

[表 3:调试速查表](#表 3:调试速查表)

[附加:可复制模板 / 10条自检 / 面试STAR](#附加:可复制模板 / 10条自检 / 面试STAR)

1) 可复制的 I2C 写事务健壮模板代码(简化版) 可复制的 I2C 写事务健壮模板代码(简化版))

2) 下次做 I2C 外设的 10 条自检清单 下次做 I2C 外设的 10 条自检清单)

3) 面试中如何讲这个项目(STAR,简洁) 面试中如何讲这个项目(STAR,简洁))

开篇摘要

这个项目的目标很明确:用 F280049C(I2CA)稳定驱动 PCA9554A,完成 GPIO 方向配置与电平读写。

现场最典型的问题是 I2C 地址阶段 NACK,软件侧表现为驱动返回错误码(ERR_NACK)。

最终定位的关键点不是"电阻太大/太小",而是地址位理解:PCA9554A 地址位按 A2/A1/A0 组织。

在问题修复后,又进一步补上了驱动健壮性设计:统一错误收尾、防重入锁、总线恢复接口。

本文把完整方法整理成可复用的工程笔记,重点讲"现象 -> 推理 -> 结论 -> 实施"。

一、项目背景与硬件条件

核心结论(先说人话)

项目不是"把函数写完"就结束,而是"硬件、电气、协议、代码"四层一起对齐。

先把硬件边界写清楚,调试会快很多。

原理解释(为什么)

I2C 问题常常跨层:

- 硬件层:电源、上拉、地址脚、连线

- 协议层:地址帧、ACK/NACK、时序

- 驱动层:状态机、超时、错误收尾

如果边界不清,排查会反复绕圈。

实现方法(怎么做)

本项目硬件条件归档如下:

- 主控:TI F280049C

- I2C 实例:I2CA(SysConfig 配置)

- 从机:PCA9554A(3.3V)

- 地址脚:A2/A1/A0 参与地址编码

- 总线:SDA/SCL 上拉 2.2k

- 速率:10kHz(调试期)

常见误区(容易踩坑)

- 只确认"连线通",不确认"地址位逻辑"。

- 只看代码,不测实际引脚电平。

- 以为低速一定不会出错,忽略协议层错误(如地址不匹配)。

二、问题现象与现场证据(波形/状态码/触发条件)

核心结论(先说人话)

故障不是随机噪声,而是可复现的地址阶段 NACK。

原理解释(为什么)

I2C 一帧里最关键的是第 9 个时钟(ACK 位):

- ACK(0):从机应答

- NACK(1):从机未应答

如果地址阶段 NACK,后续寄存器写肯定失败。

实现方法(怎么做)

现场证据链:

- 驱动返回 ERR_NACK(状态码 3)。

- 失败点在 PCA9554A_I2C_Write() 的 NACK 检查路径。

- 波形解码看到主机反复发地址写帧,ACK 位为 1。

- 触发场景:调用 PCA9554A_SetPortDirection(...) 进行寄存器写。

常见误区(容易踩坑)

- 看到"有 SCL/SDA 波形"就认为协议没问题。

- 不看 ACK 位,直接改驱动逻辑。

- 把 NACK 当成"偶发电气问题",忽略地址编码问题。

三、根因定位过程(重点:为什么是地址位顺序问题)

核心结论(先说人话)

根因是地址位顺序理解错误。PCA9554A 地址按 A2/A1/A0 解释,不是按引脚名称顺手拼接。

原理解释(为什么)

PCA9554A 的 7-bit 地址基址是 0x38,低 3 位由 A2 A1 A0 决定。

也就是说:

addr7bit=0x38+(A2A1A0)2addr7bit=0x38+(A2A1A0)2

如果位序理解错,主机发出的地址和芯片实际地址就不一致,结果就是稳定 NACK。

实现方法(怎么做)

定位路径是"证据递进":

- 确认芯片型号、供电、SDA/SCL连通性。

- 用示波器解码地址帧,确认主机实际发出的 7-bit 地址。

- 对照手册地址位定义(A2/A1/A0)。

- 修正地址位后复测:ACK 恢复,通信恢复。

常见误区(容易踩坑)

- 把地址脚顺序写成"自己习惯的顺序"。

- 只看原理图标注,不回手册核对位定义。

- 没做"波形地址解码 vs 手册地址表"的交叉验证。

四、PCA9554A 必懂寄存器与位操作(详细、易懂)

核心结论(先说人话)

把 CONFIG/OUTPUT/INPUT 三个寄存器吃透,驱动就通了大半。

原理解释(为什么)

PCA9554A 把 8 个 GPIO 全部映射到 8 位寄存器。

你改的是"位",不是"变量"。

实现方法(怎么做)

表 1:PCA9554A 关键寄存器表

| 寄存器 | 地址 | 访问 | 作用 | 位语义 |

|---|---|---|---|---|

| INPUT | 0x00 | R | 读当前引脚电平 | bit=1 高,bit=0 低 |

| OUTPUT | 0x01 | R/W | 输出锁存值 | bit=1 输出高,bit=0 输出低 |

| POLARITY | 0x02 | R/W | 输入极性翻转 | bit=1 反相 |

| CONFIG | 0x03 | R/W | 方向配置 | bit=1 输入,bit=0 输出 |

位操作小例子(RMW)

设 pin=2:

-

设输出(清位)

cppcfg = cfg & ~(1U << 2); -

设输入(置位)

cppcfg = cfg | (1U << 2); -

读电平

cpplevel = (in & (1U << 2)) != 0;

常见误区(容易踩坑)

- 忘了 RMW,直接写整字节,误伤其它 pin。

- 把 CONFIG 位语义写反(很多人第一天会反)。

- 把 OUTPUT 当成真实引脚采样值使用。

五、驱动架构设计(I2C层/寄存器层/GPIO层)

核心结论(先说人话)

分层不是"形式主义",是为了缩短定位路径。

原理解释(为什么)

把问题分层后,错误能快速归因:

- I2C层错:时序/状态机

- 寄存器层错:地址/命令字

- GPIO层错:位操作逻辑

实现方法(怎么做)

ASCII 流程图 1:驱动调用链(应用层到 I2C 层)

cs

[Application]

|

| 例如: SetPinAsOutput(dev, pin)

v

[GPIO Layer]

|

| ReadReg(CONFIG) -> bit操作 -> WriteReg(CONFIG)

v

[Register Layer]

|

| WriteReg/ReadReg 组包 [reg, data]

v

[I2C Layer]

|

| I2C_Write / I2C_WriteRead

v

[Hardware I2C Peripheral + Bus]常见误区(容易踩坑)

- 上层直接拼 I2C 帧,后续维护成本很高。

- 所有逻辑写在一个函数里,调试时不知道错在哪层。

六、PCA9554A_I2C_Write 逐行思路讲解(重点)

核心结论(先说人话)

这个函数的价值不只是"写出去",而是"写失败也能安全退出"。

原理解释(为什么)

I2C 外设是状态机。若异常路径没有收尾,容易出现 SCL 卡低、BUSY 不清、后续事务全挂。

实现方法(怎么做)

函数可理解为 9 步:

- 参数检查(空指针、长度)

- 尝试加锁(防并发)

- 等待 STOP 清除

- 等待 BUS 空闲

- 清残留状态位(NACK/STOP/ARDY)

- 配置地址、长度、发送模式

- 装载数据并发送 START

- 轮询发送完成 + 实时检查 NACK + 超时保护

- 正常 STOP 收尾;若中途失败走统一 error_exit

常见误区(容易踩坑)

- timeout 分支直接 return,不做 STOP/清状态。

- 未覆盖所有失败路径的 unlock。

- 只盯"成功路径",忽略失败路径质量。

七、goto + error_exit、软件锁、防重入、recover 的工程意义

核心结论(先说人话)

这里的 goto 是"工程正确用法",不是"坏味道"。

原理解释(为什么)

在 C 驱动里常见多个失败点。

如果每个失败点都写一遍清理代码,很容易漏。

统一 error_exit 的目标是:保证每次失败都执行同一套收尾动作。

实现方法(怎么做)

- label(如 write_error_exit:)是跳转目标,不是变量。

- goto write_error_exit; 用于集中清理。

- 软件锁 g_pca9554aI2CBusy + try_lock/unlock 防止并发重入。

- RecoverBus() 在异常后执行模块级恢复,提升鲁棒性。

ASCII 流程图 2:I2C_Write 成功路径与错误收尾路径

cs

+---------------------------+

| I2C_Write |

+---------------------------+

|

v

参数检查 / try_lock

|

+-------+--------+

| |

失败 成功

| v

| 总线检查/配置/START

| |

| 轮询完成 + NACK检查

| |

| +-------+--------+

| | |

| 失败 成功

| | v

+------> error_exit STOP/wait

| |

| v

force cleanup unlock

| |

+-------> return status常见误区(容易踩坑)

- 把 goto 和"乱跳转"混为一谈。

- 有 lock 无 unlock(死锁)。

- 有 recover 接口但不在错误路径使用。

八、示例接口设计(pin级与port级,参数解耦)

核心结论(先说人话)

pin级适合业务可读性,port级适合批量效率。两者都应该保留。

原理解释(为什么)

- pin级:上层容易写,语义直观。

- port级:一次事务改 8 位,通信开销更低。

- 参数解耦:调用方不必知道位移细节。

实现方法(怎么做)

- pin级:SetPinAsOutput、SetPinOutputLevel、GetPinLevel

- port级:SetPortDirection、SetPortOutput

- 8 参数接口:SetOutput8Level(p0...p7) 内部组装位图

示例:1,1,1,0,0,1,0,1

表示 P0/P1/P2/P5/P7 = 高,其余低。

常见误区(容易踩坑)

- 只做 pin 级,后期批量操作性能差。

- 只做 port 级,上层业务可读性变差。

- 参数不做标准化(非0即1)导致行为不一致。

九、硬件侧关键知识:上拉电阻、总线电容、I2C速率

核心结论(先说人话)

I2C 稳定性不是单一参数决定,而是 Rp + Cb + 速率 的组合问题。

原理解释(为什么)

SDA/SCL 是开漏,靠上拉形成高电平。

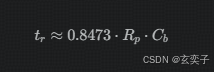

上升沿近似由 RC 决定:

- Rp 大:上升慢,速率高时风险增大

- Rp 小:灌电流大,功耗增大

实现方法(怎么做)

- 调试期先低速(如 10k/100k)跑通协议。

- 用示波器看上升沿、ACK 位低电平深度。

- 统计总线上拉"等效值"(注意并联)。

- 提速前先做波形确认。

常见误区(容易踩坑)

- 认为"低速就一定没协议问题"。

- 忽略并联上拉导致等效阻值偏小。

- 用长地线探头导致波形误判。

十、排障速查表(现象->原因->验证->修复)

核心结论(先说人话)

把故障映射成固定排查动作,比"凭感觉改代码"快得多。

原理解释(为什么)

可复用的排障路径能减少反复试错。

实现方法(怎么做)

表 2:错误码与含义(含触发条件)

| 错误码 | 名称 | 典型触发条件 |

|---|---|---|

| 0 | PCA9554A_OK | 事务正常完成 |

| 1 | PCA9554A_ERR_PARAM | 空指针、长度为0、参数非法 |

| 2 | PCA9554A_ERR_BUS | 总线忙、重入、STOP未清、锁冲突 |

| 3 | PCA9554A_ERR_NACK | 从机地址/命令未应答 |

| 4 | PCA9554A_ERR_TIMEOUT | 状态位在限定时间内未达到预期 |

表 3:调试速查表

| 现象 | 更可能原因 | 如何验证 | 修复动作 |

|---|---|---|---|

| 地址后第9位为NACK | 地址位编码不匹配 | 解码7-bit地址并核对A2/A1/A0 | 修正地址位与代码映射 |

| 事务偶发失败 | 并发重入 | 打印 busy 标志,统计调用源 | 加锁、错峰调用 |

| SCL长期低,SDA高 | 异常路径未收尾 | 看超时/NACK分支是否统一清理 | 强制STOP清理 + recover |

| 写一个pin影响其它pin | 未做RMW | 比较写前写后寄存器值 | 改为读改写 |

| 看起来有波形但不通信 | 引脚复用/实例不一致 | 核对 SysConfig 与板级连线 | 修正 I2C 实例与 pinmux |

常见误区(容易踩坑)

- 用"猜测"代替"证据链"。

- 一遇到 NACK 就先怀疑电阻,忽略地址和位序。

十一、我的可复用开发清单(checklist)

核心结论(先说人话)

驱动质量靠流程,不靠临场发挥。

原理解释(为什么)

Checklist 能把经验固化,减少重复踩坑。

实现方法(怎么做)

- 先确认器件型号和地址规则(含位序)。

- 先做最小事务(地址写 + ACK 验证)。

- 建立三层驱动结构。

- 所有位操作采用 RMW。

- 所有轮询加超时。

- 所有失败路径统一收尾。

- 加并发互斥。

- 提供 recover 接口。

- 示例接口同时提供 pin级 + port级。

- 用波形和日志共同验收。

常见误区(容易踩坑)

- 先堆功能,后补基础。

- 无统一日志,出问题难复盘。

- 没有"可复现最小用例"。

结尾:经验总结与下一步优化方向

这次项目真正的收获有三点:

- 定位方法升级:先证据后结论,波形第 9 位是关键抓手。

- 代码思维升级:成功路径重要,失败路径更重要。

- 工程能力升级:分层 + RMW + 锁 + recover,形成可复用骨架。

下一步建议:

- 给 WriteRead 增加更细粒度状态日志(时间戳+状态位)。

- 把软件锁升级到中断安全版本(如临界区/RTOS mutex)。

- 增加"上电自检函数":地址应答、寄存器读回、错误码报告。

附加:可复制模板 / 10条自检 / 面试STAR

1) 可复制的 I2C 写事务健壮模板代码(简化版)

cpp

typedef enum { OK=0, ERR_PARAM, ERR_BUSY, ERR_NACK, ERR_TIMEOUT } status_t;

static volatile bool g_i2c_busy = false;

static bool try_lock(void) {

if (g_i2c_busy) return false;

g_i2c_busy = true;

return true;

}

static void unlock(void) { g_i2c_busy = false; }

static void force_cleanup(uint32_t base) {

I2C_sendStopCondition(base);

// wait stop clear ...

// clear status ...

}

status_t dev_i2c_write(uint32_t base, uint8_t addr, const uint8_t *buf, uint16_t len)

{

status_t st = OK;

bool started = false;

if (!buf || len == 0) return ERR_PARAM;

if (!try_lock()) return ERR_BUSY;

// bus ready check ...

// set addr/mode/count ...

// put data ...

I2C_sendStartCondition(base);

started = true;

// poll done + check nack + timeout ...

// if error: st=ERR_xxx; goto error_exit;

I2C_sendStopCondition(base);

// wait stop clear ...

unlock();

return OK;

error_exit:

if (started) force_cleanup(base);

unlock();

return st;

}2) 下次做 I2C 外设的 10 条自检清单

- 型号和手册版本确认。

- 地址位顺序确认(A2/A1/A0)。

- 7-bit 与 8-bit 地址不混用。

- RESET 脚状态确认。

- SysConfig 的 I2C 实例与引脚复用确认。

- 上拉等效阻值确认(含并联)。

- 超时机制覆盖所有轮询点。

- 错误路径统一 STOP + 清状态 + unlock。

- 并发访问路径(中断/任务/主循环)梳理。

- 示波器必须看 ACK 位,不只看有无波形。

3) 面试中如何讲这个项目(STAR,简洁)

S :F280049C 驱动 PCA9554A,现场出现稳定 NACK 和偶发总线异常。

T :在不牺牲可读性的前提下完成驱动落地并提升鲁棒性。

A :用波形+状态码建立证据链,定位地址位序问题;代码侧补齐分层、RMW、统一错误收尾、防重入锁、recover。

R:通信恢复并稳定运行,形成可复用的 I2C 驱动模板与排障流程。