目录

一、前言

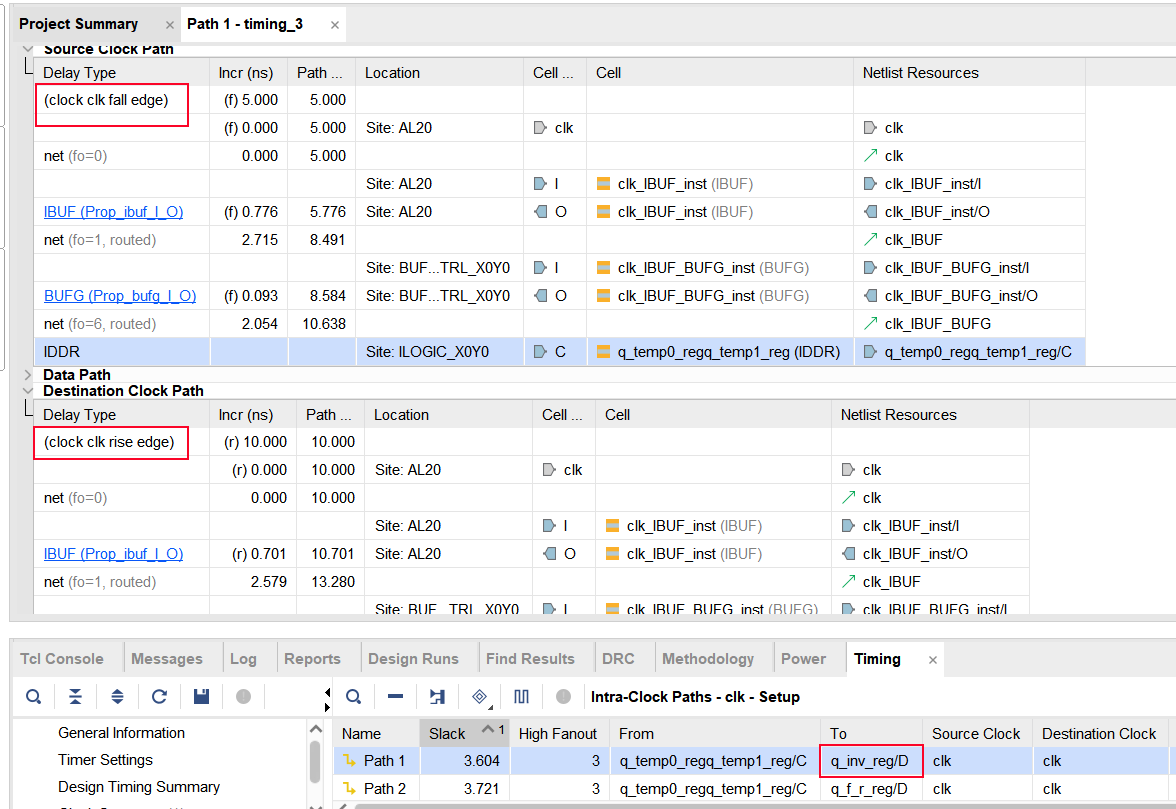

查看设计的时序报告中,在任意一条时序路径中,source clock path或 Destination Clock path下的第一行要么为clock xxx rise edge,要么为clock xxx fall edge,如何理解这个内容呢?下面将详细介绍。

二、触发器的边沿触发

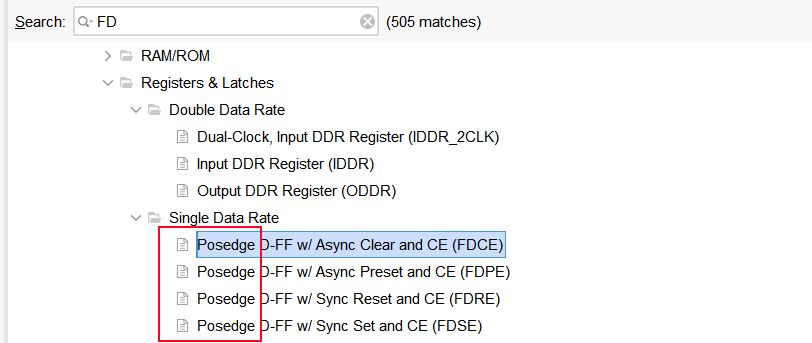

FPGA中的触发器在硬件上是既支持上升沿触发,也支持下降沿触发。在实际设计中,通常默认是上升沿触发,从各触发器的原语也可看出是posedge,有时也需要使用到下降沿触发,如DDR的双边沿数据采集。

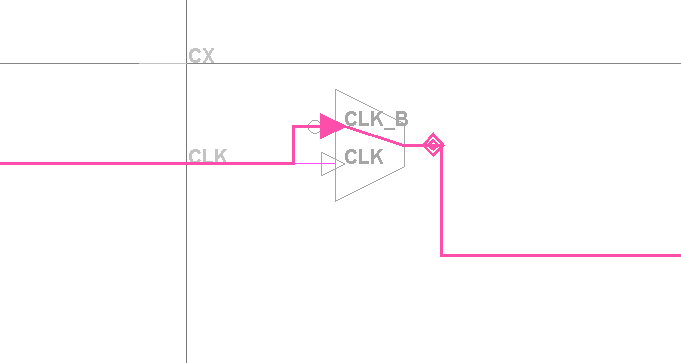

在SliceL单元中,时钟信号进入到触发器时,会先经过一个CLKMUX的单元,下图中CLK_B即经过了取反处理后输出,CLK则是直接输出。

在具体的verilog代码中,触发的边沿则是体现在always语句块中时钟信号(如示例的clk信号)前面是posedge还是negedge,如果是posedge,在时钟信号进入到触发器q_r_r的时钟引脚上时上升沿触发,否则是下降沿触发

// 数据接收,接收时钟上升沿有效

always @(posedge clk or negedge rst) begin

if (!rst) begin

q_r_r <= 1'b0; // 异步复位

end else

q_r_r <= q_temp0;

end

// 数据接收,接收时钟下降沿有效

always @(negedge clk or negedge rst) begin

if (!rst) begin

q_r_f <= 1'b0; // 异步复位

end else

q_r_f <= q_temp0;

end三、设计示例

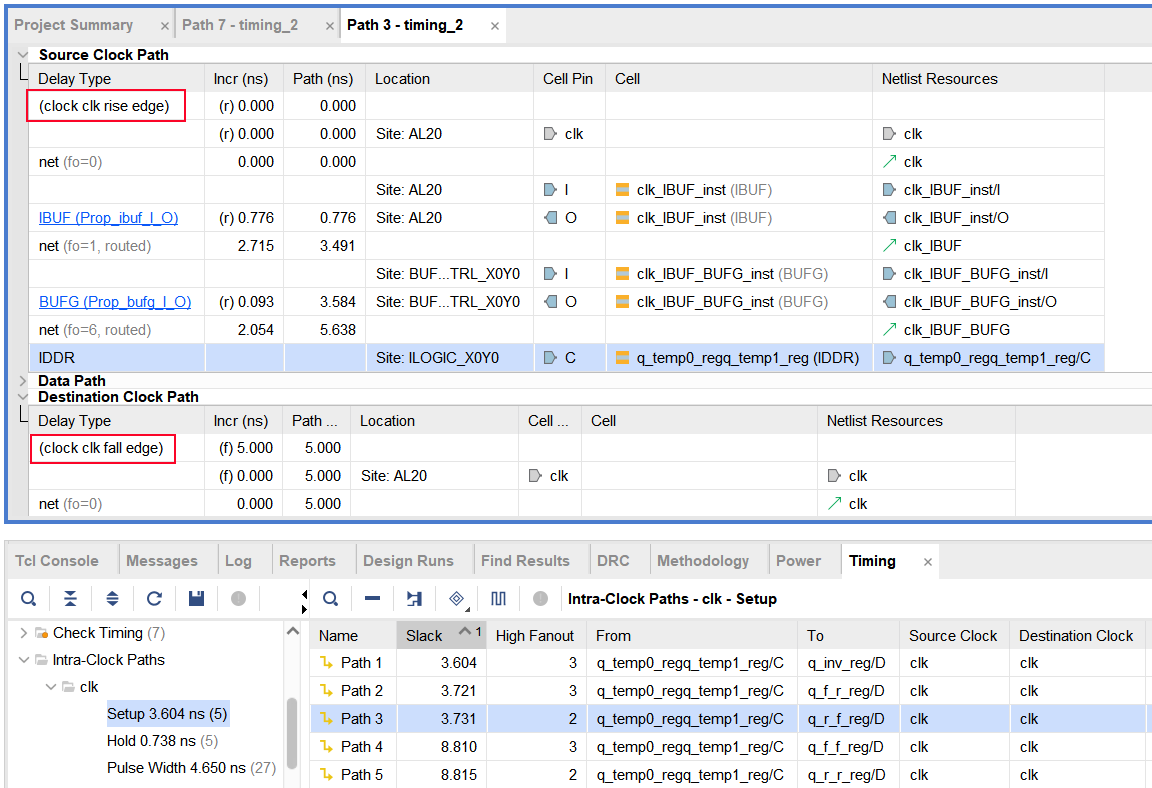

下面以时序路径中源时钟和目的时钟分别为posedge和negedge的场景进行说明,同时增加一个时钟信号经过取反后到达触发器的场景来加深理解,示例代码如下,设计中输出寄存器q_r/f_r/f中第一个r/f表示原时钟的边沿,第二个r/r表示目的时钟的边沿

module clk_rise_fall (

input wire data, // 输入数据

input wire clk, // 时钟信号

input wire rst, // 异步复位信号,低电平有效

output reg q_r_r, // 触发器输出

output reg q_r_f, // 触发器输出

output reg q_f_r, // 触发器输出

output reg q_f_f, // 触发器输出

output reg q_inv // 触发器输出

);

reg q_temp0,q_temp1; // 中间寄存器,

// 数据发送,发送时钟上升沿有效

always @(posedge clk or negedge rst) begin

if (!rst)

q_temp0 <= 1'b0; // 异步复位

else

q_temp0 <= data;

end

// 数据接收,接收时钟上升沿有效

always @(posedge clk or negedge rst) begin

if (!rst) begin

q_r_r <= 1'b0; // 异步复位

end else

q_r_r <= q_temp0;

end

// 数据接收,接收时钟下降沿有效

always @(negedge clk or negedge rst) begin

if (!rst) begin

q_r_f <= 1'b0; // 异步复位

end else

q_r_f <= q_temp0;

end

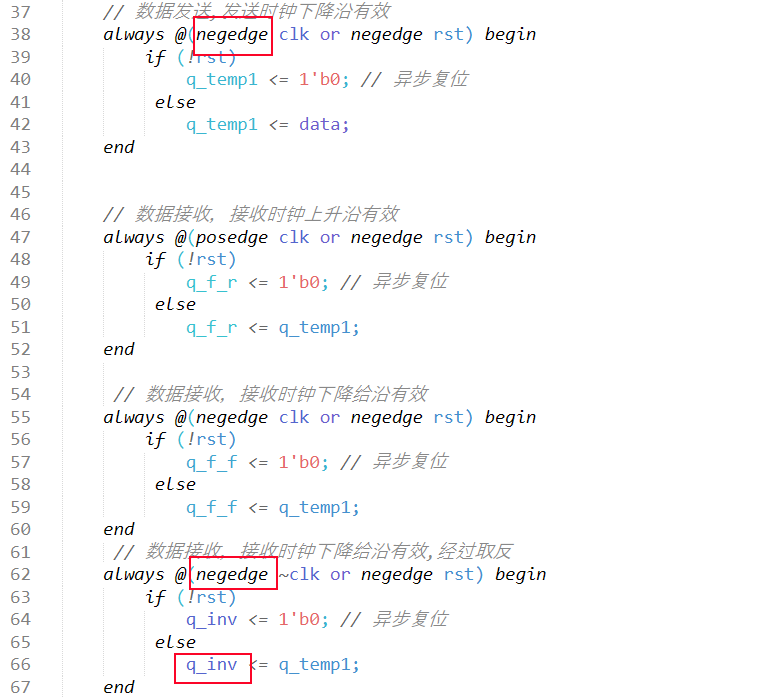

// 数据发送,发送时钟下降沿有效

always @(negedge clk or negedge rst) begin

if (!rst)

q_temp1 <= 1'b0; // 异步复位

else

q_temp1 <= data;

end

// 数据接收,接收时钟上升沿有效

always @(posedge clk or negedge rst) begin

if (!rst)

q_f_r <= 1'b0; // 异步复位

else

q_f_r <= q_temp1;

end

// 数据接收,接收时钟下降给沿有效

always @(negedge clk or negedge rst) begin

if (!rst)

q_f_f <= 1'b0; // 异步复位

else

q_f_f <= q_temp1;

end

// 数据接收,接收时钟下降给沿有效,经过取反

always @(negedge ~clk or negedge rst) begin

if (!rst)

q_inv <= 1'b0; // 异步复位

else

q_inv <= q_temp1;

end

endmodule时序报告结果如下,以Path3为例,q_r_f表示原时钟为上升沿rise,目的时钟边沿为fall,和实际结果符合预期

再看源时钟和目的时钟设计中使用negedge,但目的时钟前存在取反的操作,

时序报告中目的时钟的边沿为rise,并非fall(negedge),这就是由于触发器q_inv的触发时钟为negedge ~clk的原因,只有时钟触发沿为rise,后面经过取反后进入到q_inv的边沿才会为fall