本篇文章用来记录自己对DSMC通信协议的理解。

1.DSMC概述

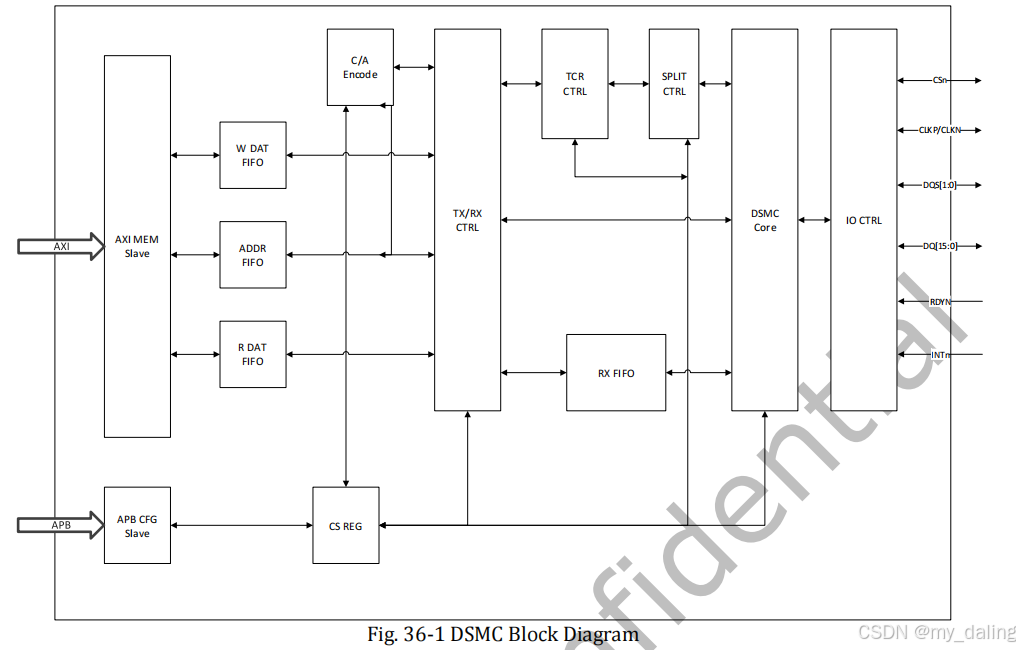

Double Data Rate Serial Memory Controller(DSMC),双倍速率串行存储器控制器,通过命令、地址、数据线分时复用,数据上下沿传输,具有少引脚数、高带宽的特点。

2.DSMC硬件接口介绍(RK3576)

详细接口如下(主机侧)

| 强制接口 ||||

| 引脚 | 方向 | 电平 | 说明 |

|---|---|---|---|

| CLKP CLKP | O | - | 通信时钟,差分时钟用于1.8V设备,3.0V以上设备只使用CLKP 主机发送数据和时钟交叉沿中心对齐(从机在时钟跳变沿采样) |

| CSn0~CSn3 | O | - | 片选,支持4个从设备 |

| DQ0~DQ15 | I/O | - | 双向数据总线 |

| DQS0 DQS1 | I/O | - | RWDS读写选通信号,CA命令期间用来向主机表示是否需要额外延时 主机读数据期间和数据信号沿对齐用于主机获取数据 主机写数据期间用于数据掩码(localbus模式下无效) |

| 可选接口 | |||

| RESETN | O | 上拉 | 复位信号 |

| RDYN | I | 开漏 | 从机准备好信号 |

| INTn0~INTn3 | I | 开漏 | 中断信号 |

3. DSMC总线模式(支持的协议)

.Hyperbus PSRAM、

.Xccela PSRAM

.Local bus

4.DSMC读写时序介绍(以HyperRAM为例)

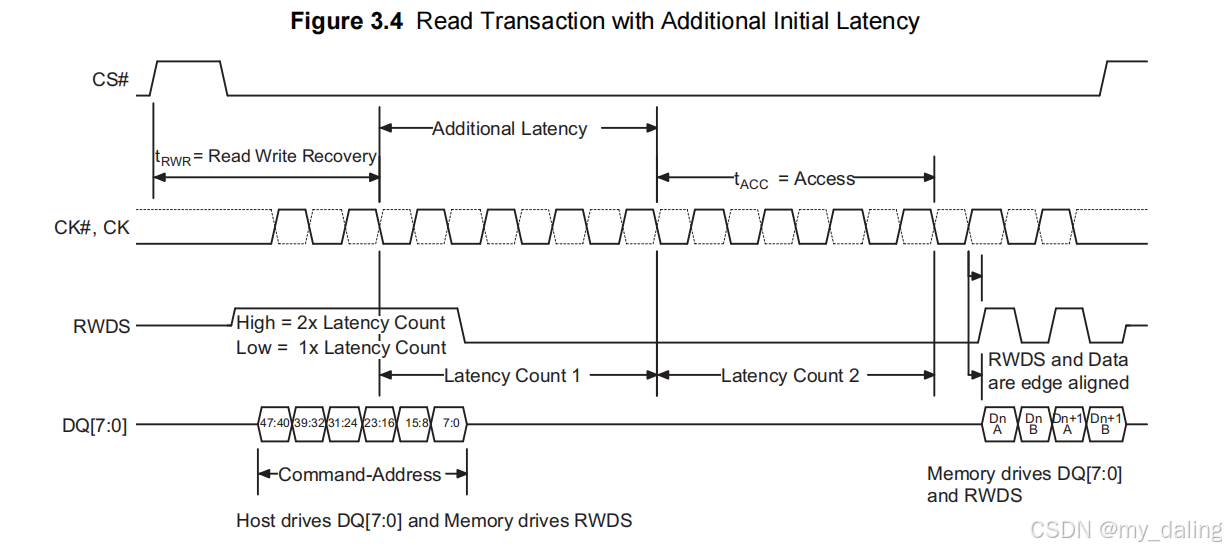

4.1读操作

1.主机会判断CS high、CLKP low、CLKN high,都符合则进行开始进入读操作

1.主机会判断CS high、CLKP low、CLKN high,都符合则进行开始进入读操作

2.拉低片选,随后传输48bit CA指令,传输指令同时主机监测DQS电平判断是否插入额外延时

3.在到达延时时间后读取DQS信号,读取对应数据

*在整个读事务期间DQS信号都由从机控制

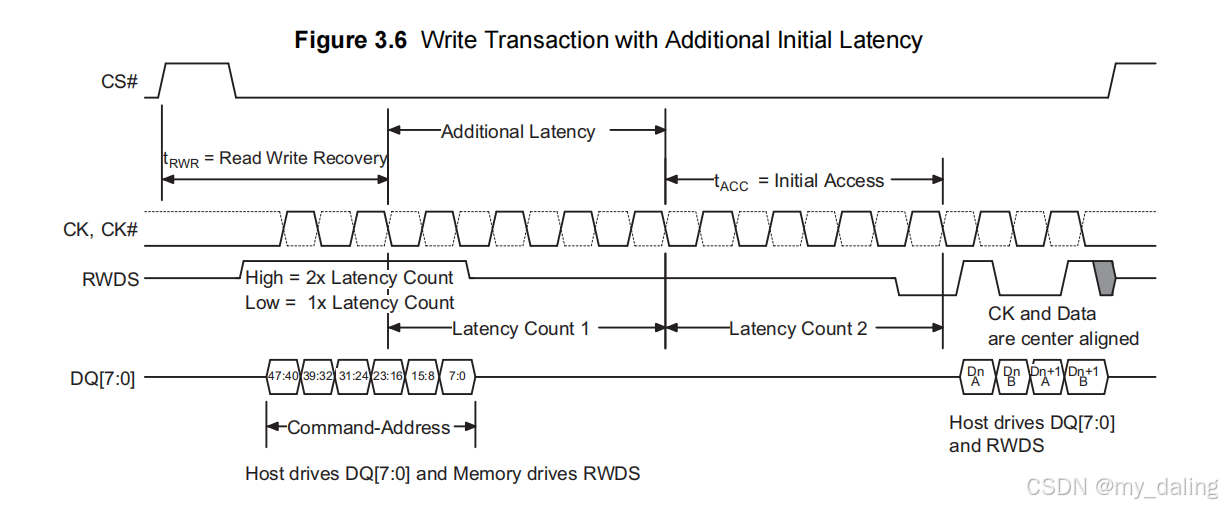

4.2写操作

1.主机会判断CS high、CLKP low、CLKN high,都符合则进行开始进入写操作

2.拉低片选,随后传输48bit CA指令,传输指令同时主机监测DQS电平判断是否插入额外延时

3.从机在接收完CA指令后释放DQS信号,主机需要在延时结束前将DQS驱动至有效低电平,从机在到达延时时间后读取DQS信号和数据信号

*写事务中DQS作为掩码功能使用,高电平指示数据写入(在零延时写入模式下主机从机都不再关心DQS信号)

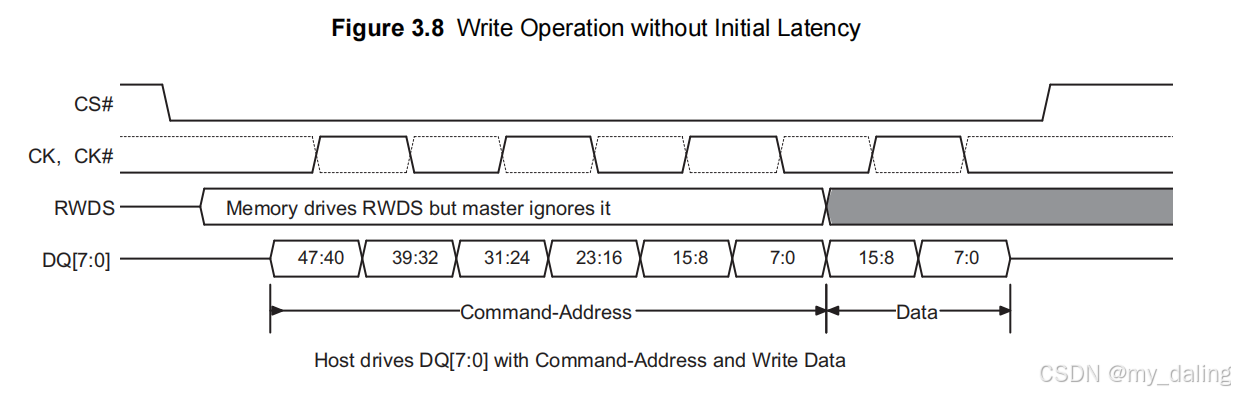

4.3零延时写操作

零延时写操作和普通写类似,区别在于写入CA指令后立刻传输数据字节,同时主机从机不再关注DQS信号。

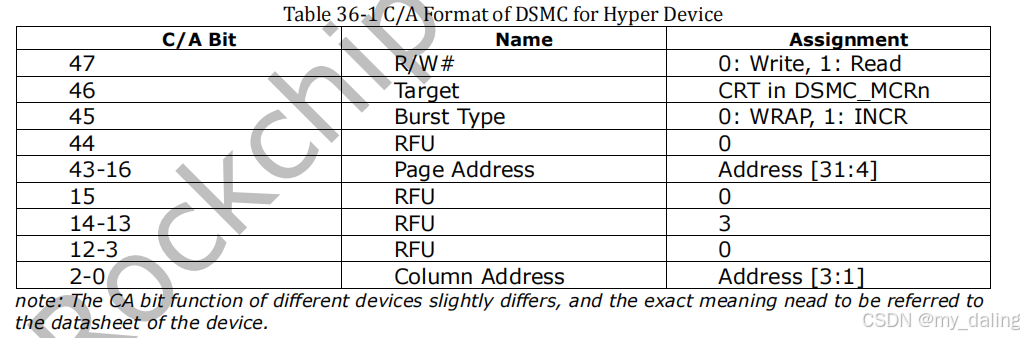

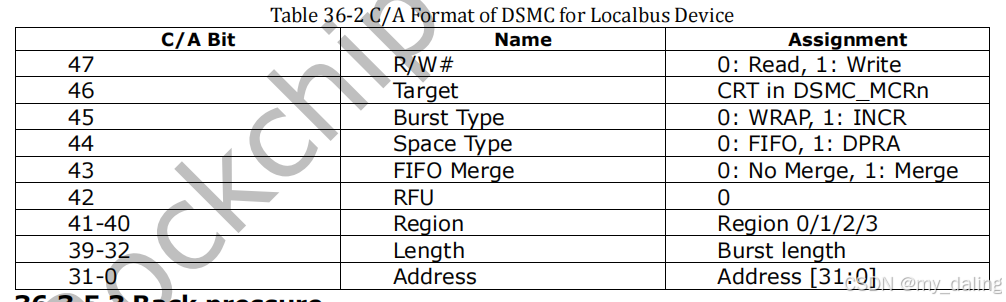

5.DSMC CA指令格式

5.1 HyperBus模式下的CA指令结构

5.2 LocalBus模式下的CA指令结构

主设备参数配置和寄存器表这里还没看懂暂时不写了(反正是RK封装好的驱动直接调用就可以......小声)