camera 和LCD的HSYNC,VSYNC的区别

这个问题问得很好,本质是同样叫 VSYNC / HSYNC,但"方向"和"语义"完全不同。你从嵌入式软件工程师角度理解,可以抓住一句话:

图像传感器:输出时序(生产数据)

LCD RGB屏:输入时序(消费数据)

下面给你做一个工程视角的宏观拆解。

一、核心对比(一句话抓本质)

| 模块 | 角色 | VSYNC/HSYNC本质 |

|---|---|---|

| 图像传感器(Camera) | 数据源 | 告诉MCU:"我正在输出哪一帧/哪一行" |

| LCD RGB屏 | 数据接收端 | 告诉MCU:"你该在什么时候给我哪一帧/哪一行" |

👉 一个是我发给你(带节奏)

👉 一个是你喂给我(按我节奏)

二、图像传感器(Camera)的 VSYNC / HSYNC

1️⃣ 信号方向

👉 传感器 → MCU / ISP

2️⃣ 信号作用

-

VSYNC(Frame Sync)

- 一帧开始 / 结束标志

- 表示新的一帧图像来了

-

HSYNC(Line Sync)

- 一行像素开始 / 结束

- 用于行对齐

-

PCLK(像素时钟)

- 每个像素什么时候采样

3️⃣ 软件工程视角

你在写驱动时,本质是在做:

c

while (VSYNC == 0); // 等待帧开始

for (每一行) {

while (HSYNC == 0); // 等待行开始

for (每个像素) {

pixel = read(PCLK);

}

}👉 关键词:

- 采集(Capture)

- 被动接收

- 跟随外设节奏

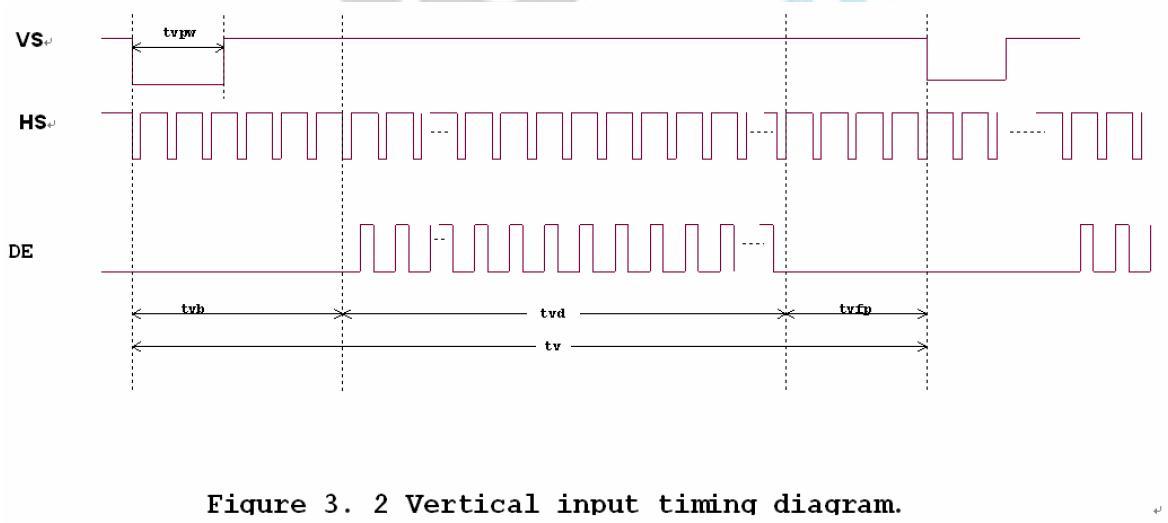

三、LCD RGB屏 的 VSYNC / HSYNC

1️⃣ 信号方向

👉 MCU / RGB控制器 → LCD

2️⃣ 信号作用

-

VSYNC

- 通知屏幕:新的一帧开始显示

-

HSYNC

- 通知屏幕:新的一行开始显示

-

PCLK

- 每个像素何时被锁存

-

DE(Data Enable)

- 哪些像素是有效数据

3️⃣ 软件工程视角

你在做的是:

c

while (1) {

// VSYNC周期

send_frame_start();

for (每一行) {

send_hsync();

send_pixels(line_data);

}

}👉 关键词:

- 驱动显示(Drive)

- 主动输出

- 你必须严格生成时序

四、本质区别(非常关键)

1️⃣ 控制权不同

| 项目 | Camera | LCD |

|---|---|---|

| 谁控制节奏 | 传感器 | MCU / LCD控制器 |

| MCU角色 | 被动采集 | 主动输出 |

2️⃣ 数据流方向

Camera:

像素 → MCU

LCD:

MCU → 像素👉 完全反过来

3️⃣ 时序容忍度

| 项目 | Camera | LCD |

|---|---|---|

| 时序错一点 | 丢帧/错行 | 直接花屏 |

| 是否可缓存 | 可以(FIFO/DMA) | 通常实时要求严格 |

4️⃣ 工程实现差异(重点)

Camera(输入接口)

- DVP / MIPI CSI

- DMA + 中断

- 行/帧同步捕获

👉 你关心:

- 数据有没有丢

- 帧有没有对齐

LCD(输出接口)

- RGB并口 / SPI / MIPI DSI

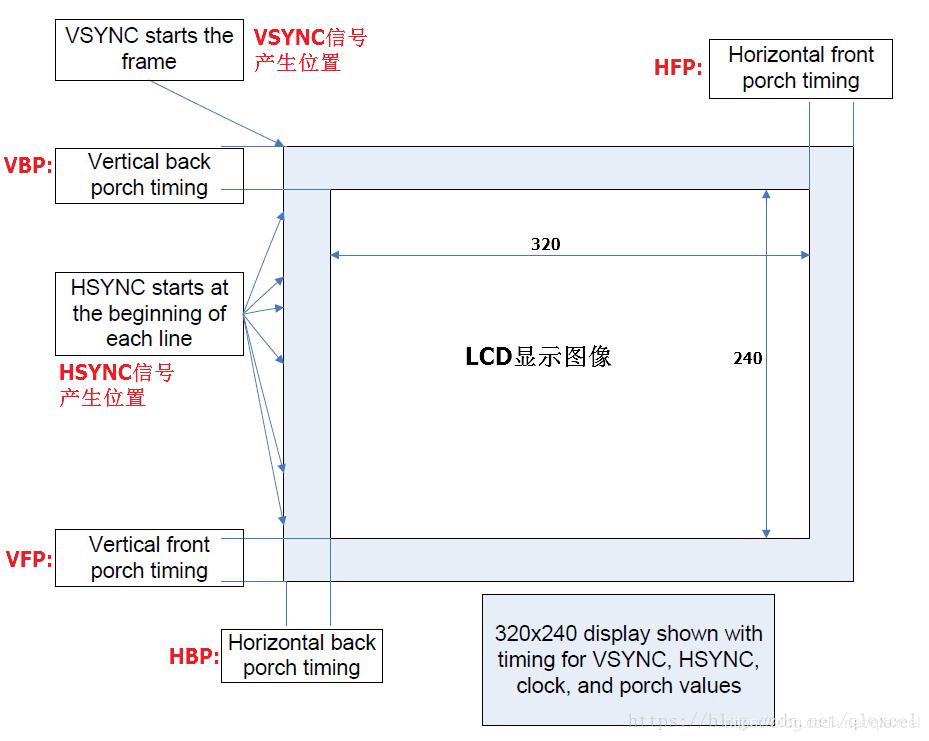

- 时序寄存器配置(porch、sync宽度)

- 刷新率(60Hz等)

👉 你关心:

- 时序参数是否匹配屏

- PCLK是否正确

- 是否花屏/撕裂

五、一个形象比喻(很好记)

📷 图像传感器(Camera)

像摄像头对你说:

"我现在开始拍一帧了(VSYNC)

现在是第一行(HSYNC)

像素来了你赶紧接!"

👉 你只能跟着它节奏走

📺 LCD屏

像屏幕对你说:

"现在该显示新一帧了(VSYNC)

现在给我第1行(HSYNC)

每个像素按时送过来!"

👉 你必须按它要求喂数据

六、嵌入式开发中的坑(你肯定会遇到)

1️⃣ Camera常见坑

- VSYNC极性搞反 → 帧错乱

- HSYNC错 → 行错位

- PCLK边沿错 → 数据错位

2️⃣ LCD常见坑

- porch参数错 → 图像偏移

- PCLK不匹配 → 花屏

- VSYNC/HSYNC极性错 → 不显示

七、总结(工程一句话版)

👉 Camera 的 VSYNC/HSYNC = "我在输出数据,请你按我节奏接"

👉 LCD 的 VSYNC/HSYNC = "我要显示数据,你必须按我节奏送"

如果你愿意,我可以帮你结合 ESP32-S3 RGB LCD + Camera(DVP) 给你画一个完整的数据链路(采集→缓存→显示),这个在你做电子相册/图像项目时会非常有用。

补充

你这个理解已经接近对了,但有一个关键点需要纠正 :

👉 Camera 和 LCD 的 VSYNC/HSYNC 都不是"你去检测然后决定干嘛"这么简单,而是"谁主导时序"的问题。

我帮你按工程逻辑给你"掰正一下",保证你以后写驱动不踩坑。

一、先直接给结论(纠正你的描述)

你说的是:

Camera 收到 VSYNC → 开始获取一帧

LCD 检测 HSYNC → 写一行 → 检测 VSYNC → 结束

👉 这里有两个误区:

❌ 误区1:Camera"收到"VSYNC

→ 实际是:Camera"产生"VSYNC

❌ 误区2:LCD"检测"VSYNC/HSYNC来决定写数据

→ 实际是:LCD不检测,是你(MCU)在产生这些信号

二、正确的工程模型(非常重要)

1️⃣ Camera(图像传感器)

👉 正确理解:

Camera输出 VSYNC/HSYNC,你去"捕获"

实际流程:

c

// 被动模式(典型DVP)

等待 VSYNC 上升沿 → 一帧开始

for (每一行) {

等待 HSYNC

按 PCLK 采样像素

}👉 重点:

- VSYNC/HSYNC 是 输入信号

- 你是 监听 + 采集

- 你不能控制它

2️⃣ LCD(RGB接口屏)

👉 正确理解:

不是你"检测",而是你在"生成"VSYNC/HSYNC去驱动LCD

实际流程(硬件自动做的):

c

LCD控制器(比如ESP32-S3 RGB外设):

自动循环:

拉VSYNC → 帧开始

for (每一行) {

拉HSYNC

输出一行像素数据

}👉 重点:

- VSYNC/HSYNC 是 输出信号

- 你是 配置时序参数

- 硬件帮你自动跑

三、把你的话"改成完全正确版本"

你原话改成工程正确版是:

✔ Camera:

当检测到 VSYNC(来自传感器)时,MCU开始采集一帧数据;

在每个 HSYNC 到来时,按 PCLK 采集一行像素数据

✔ LCD:

MCU(或LCD控制器)主动产生 VSYNC 表示一帧开始;

在每个 HSYNC 周期内,输出一行像素数据给LCD;

整个过程是持续循环的,而不是靠检测VSYNC结束

四、一个关键认知(很多人卡在这)

❗ LCD不是"写完一帧就停"

你说:

"检测 VSYNC set了就结束写入"

👉 这是不对的,LCD是:

c

while (1) {

一帧一帧不停刷新(60Hz)

}👉 否则会:

- 黑屏

- 闪屏

- 撕裂

五、再给你一个工程级对比(非常实用)

| 项目 | Camera | LCD |

|---|---|---|

| VSYNC/HSYNC | 输入 | 输出 |

| 你做什么 | 捕获 | 生成 |

| 控制权 | 外设 | MCU |

| 是否循环 | 外设决定 | 你必须持续输出 |

| 驱动方式 | 中断 / DMA | 时序配置 + DMA |

六、结合你ESP32-S3的实际情况(重点)

你现在这种项目(电子相册 / RGB屏):

LCD侧(ESP32-S3)

-

用

esp_lcd_rgb_panel -

配:

- hsync_back_porch

- hsync_front_porch

- vsync_pulse_width

- pclk

👉 然后:

👉 硬件自动生成 VSYNC/HSYNC,你不用管"检测"

Camera侧(如果你接DVP)

- 用 I2S camera模式

- DMA采集

- VSYNC/HSYNC作为同步信号

七、一句话帮你彻底记住

👉 Camera:我给你节奏,你来接数据

👉 LCD:我不给你节奏,你必须给我节奏

八、如果你想再深入(建议)

你下一步可以搞清楚这两个高级点(对你项目很关键):

- porch(前后肩)到底是啥

- DE模式 vs HSYNC/VSYNC模式

- 双缓冲(避免撕裂)

如果你愿意,我可以帮你画一张

👉 ESP32-S3:Camera → DMA → FrameBuffer → RGB LCD 的完整数据链路图

这个对你做电子相册/视频显示是"开窍级"的理解。

ESP32 RGB LCD外设工作原理介绍

好,这一块我给你从嵌入式工程实战视角 讲清楚,直接对标你现在做的 ESP32-S3 + RGB LCD(LVGL/电子相册)。

一、先给你一个整体工作模型(核心)

ESP32 RGB LCD 外设本质

👉 可以把它理解成一个:

"带时序发生器 + DMA 的持续视频输出引擎"

它做三件事:

- 生成时序(VSYNC / HSYNC / PCLK / DE)

- 从内存(FrameBuffer)读像素数据

- 按时序把像素送到LCD

二、完整数据流(你必须脑子里有这个图)

FrameBuffer(内存)

↓

DMA搬运

↓

ESP32 RGB LCD外设

↓

VSYNC / HSYNC / PCLK

↓

LCD屏👉 关键点:

- 数据源:内存

- 节奏:LCD外设控制

- 输出:持续不断(像视频流)

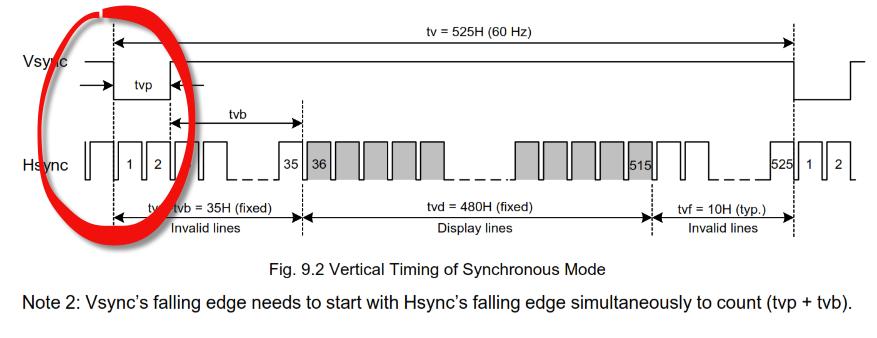

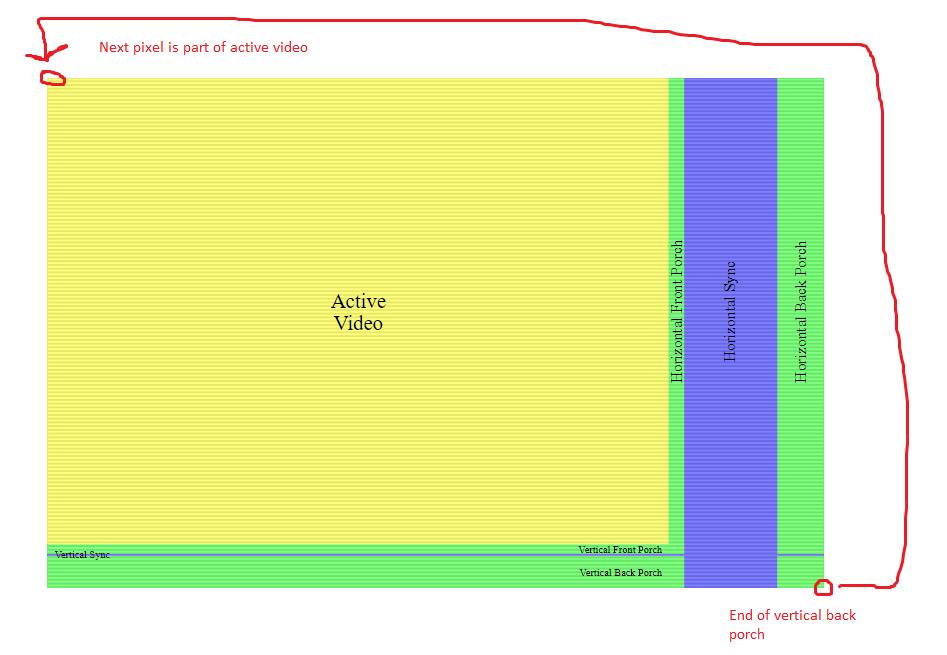

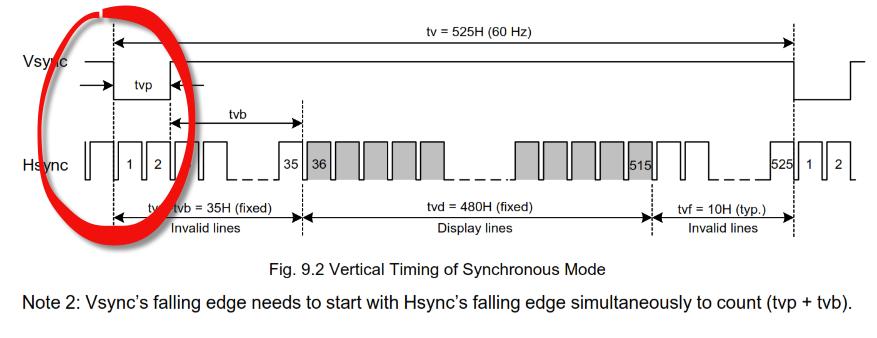

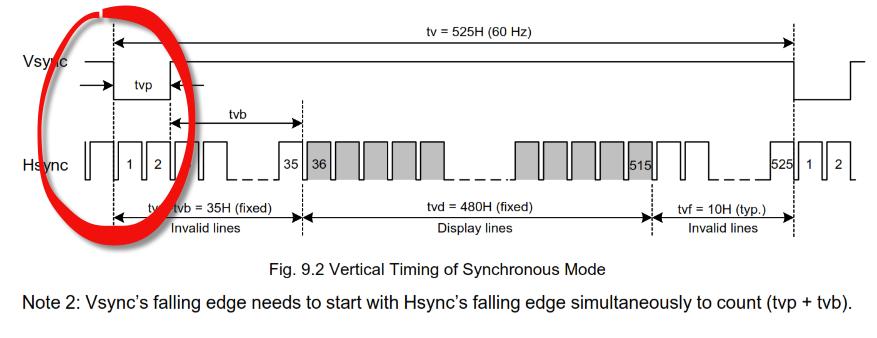

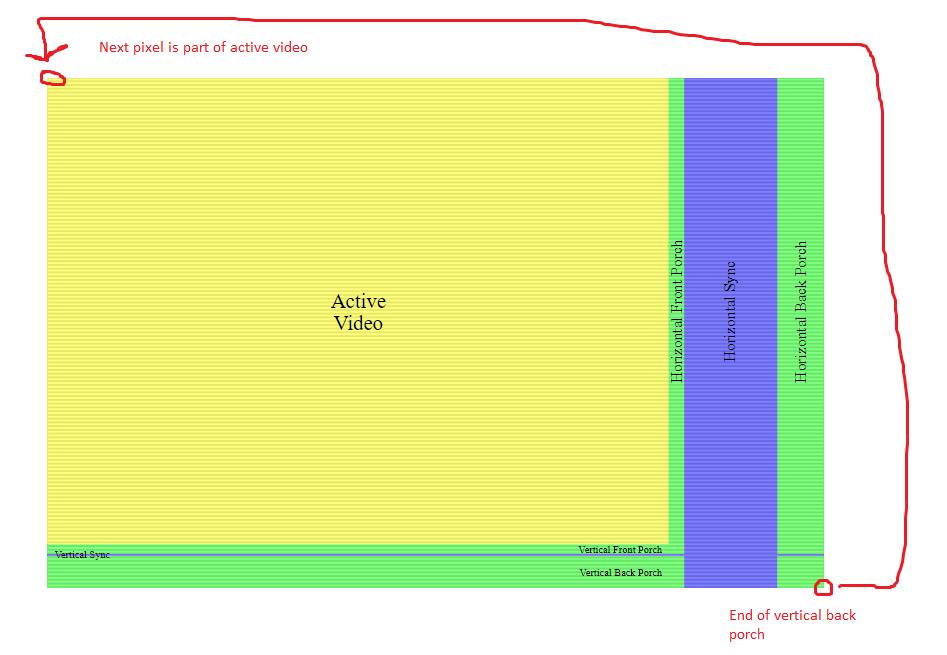

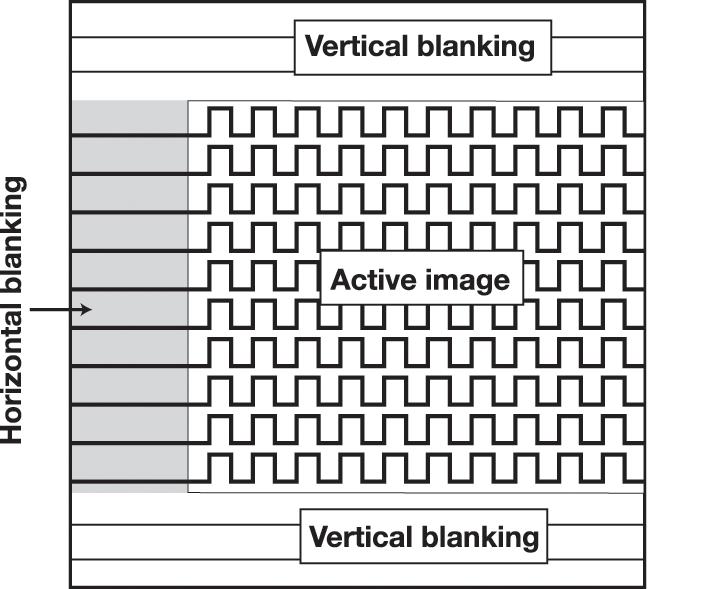

三、RGB LCD外设内部是怎么跑的

1️⃣ 时序发生器(核心中的核心)

它内部有一套"计数器":

水平方向(行)

|<-- back porch -->|<-- 有效像素 -->|<-- front porch -->|

↑ ↑ ↑

HSYNC 显示区 空白区垂直方向(帧)

VSYNC

↓

back porch

↓

有效行

↓

front porch👉 本质是:

c

for (每一帧) {

产生 VSYNC

for (每一行) {

产生 HSYNC

输出像素数据

}

}⚠️ 这些全部是 硬件自动跑的

2️⃣ DMA(持续喂数据)

RGB外设会:

c

while (1) {

从 framebuffer 读数据

按 PCLK 一像素一像素送出去

}👉 注意:

- 不走CPU(否则早炸了)

- 必须用 DMA

3️⃣ PCLK(像素节拍器)

👉 每一个 PCLK:

输出一个像素(RGB565 / RGB888)👉 所以:

带宽 = 分辨率 × 刷新率 × 像素位宽四、你必须理解的几个关键参数

1️⃣ 分辨率 ≠ 实际时序

比如:

480 × 272但真实输出是:

(480 + porch) × (272 + porch)👉 所以:

👉 PCLK要按"总像素"算,不是有效像素

2️⃣ porch(90%的人一开始都会踩坑)

水平:

- hsync_pulse_width

- hsync_back_porch

- hsync_front_porch

垂直:

- vsync_pulse_width

- vsync_back_porch

- vsync_front_porch

👉 作用:

给LCD内部扫描电路"缓冲时间"

👉 配错会:

- 图像偏移

- 不显示

- 抖动

3️⃣ DE(Data Enable)

两种模式:

✔ DE模式(推荐)

- DE=1 → 有效像素

- DE=0 → 空白

👉 LCD更容易驱动

✔ SYNC模式(VSYNC+HSYNC)

- 靠sync信号判断位置

👉 更底层

五、ESP32-S3实际工作方式(你会用到)

用 esp_lcd_rgb_panel 时:

你做的事情:

c

esp_lcd_rgb_panel_config_t config = {

.timings = {

.pclk_hz = 10MHz,

.h_res = 480,

.v_res = 272,

.hsync_back_porch = xx,

.hsync_front_porch = xx,

.vsync_back_porch = xx,

.vsync_front_porch = xx,

},

};👉 你只是在:

"告诉硬件:你按这个节奏跑"

然后发生的事情(自动)

- 硬件生成 VSYNC/HSYNC

- DMA搬 framebuffer

- LCD被持续刷新(60Hz)

六、工程中最容易炸的点(重点)

❗1️⃣ PCLK算错 → 直接花屏

计算方式:

PCLK ≈ (Htotal × Vtotal × FPS)👉 Htotal = 有效 + porch

👉 Vtotal = 有效 + porch

❗2️⃣ 带宽不够 → 撕裂 / 卡顿

举例:

480×272 × 2字节 × 60Hz ≈ 15MB/s👉 再加porch → 更高

⚠️ ESP32内存带宽有限!

❗3️⃣ FrameBuffer位置

必须注意:

- 放在 SRAM(内部RAM)优先

- PSRAM会慢(可能撕裂)

❗4️⃣ 单缓冲 vs 双缓冲

单缓冲

- 你在写,LCD在读

👉 会撕裂

双缓冲(推荐)

Buffer A → 显示

Buffer B → 渲染

交换👉 LVGL就是这么干的

❗5️⃣ VSYNC同步(防撕裂关键)

很多人忽略:

👉 应该在VSYNC时切buffer

否则:

- 半帧切换

- 画面断裂

七、把Camera + LCD串起来(你未来会用)

Camera → DMA → FrameBuffer → RGB LCD → 屏幕👉 难点:

- 分辨率对齐

- 格式转换(YUV → RGB)

- 帧率匹配

八、最后给你一个"工程级总结"

👉 ESP32 RGB LCD外设本质:

一个按固定时序,从内存读取像素并持续输出到LCD的硬件视频流引擎

👉 你要做的只有三件事:

- 配对时序(porch + 分辨率 + PCLK)

- 保证内存带宽够

- 处理好双缓冲避免撕裂

九、一句话帮你彻底吃透

👉 LCD不是"你想什么时候写就写"

👉 而是:硬件一直在读,你必须保证"随时有数据给它"

如果你下一步想深入,我可以帮你拆:

👉 ESP32-S3 RGB LCD + LVGL 的完整优化方案(避免卡顿/撕裂)

👉 或者 PCLK / 带宽怎么算才不会炸(结合你实际屏)

这个会直接影响你项目成败。

好,这个 porch(前后肩) 是很多人第一次做 RGB LCD 最容易懵的点,我给你用工程+直觉方式讲清楚,你一下就通了。

一、先一句话理解 porch

👉 porch = "无效显示时间(空白时间)"

也可以理解为:

LCD在每一行/每一帧之间的"休息时间"

二、先看一行数据是怎么传的(重点)

一行完整的时序其实是这样:

text

[HSYNC] → [Back Porch] → [有效像素] → [Front Porch]三、逐个给你讲清楚(非常关键)

1️⃣ HSYNC(行同步脉冲)

👉 类似:

"喂!LCD,现在新的一行要开始了!"

2️⃣ Back Porch(后沿/后肩)

👉 紧跟在 HSYNC 后面的一段空白时间

作用:

给LCD一点准备时间,从"同步状态"切换到"显示状态"

3️⃣ 有效像素区(你真正显示的内容)

text

比如 480 像素 → 这一段才是图像👉 只有这段数据会显示在屏幕上

4️⃣ Front Porch(前沿/前肩)

👉 一行结束后,再留一段空白时间

作用:

让LCD有时间"收尾",准备下一行

四、为什么必须要有 porch?(核心理解)

👉 LCD不是瞬间切换的,它是"扫描电路":

text

一行扫完 → 回到下一行👉 porch 就是:

- 电子电路稳定时间

- 扫描回扫时间(类似CRT历史遗留)

五、垂直方向也是一样(帧级别)

一帧结构:

text

VSYNC → Back Porch → 有效行 → Front Porch六、举个真实例子(你最容易理解)

假设你的屏:

text

分辨率:480 × 272但真实输出是:

text

水平:

HSYNC + BP(40) + 480 + FP(20)

垂直:

VSYNC + BP(8) + 272 + FP(4)👉 实际发送的像素数量:

text

总宽度 = 480 + 40 + 20 + sync

总高度 = 272 + 8 + 4 + sync👉 这就是为什么:

PCLK一定要按"总分辨率"算!

七、你可以这样形象理解(非常好记)

📺 LCD像一个人读书

text

HSYNC:翻到新一行

Back Porch:眼睛对焦

有效像素:认真读内容

Front Porch:读完缓一下八、工程上最重要的影响(你必须知道)

❗1️⃣ porch配错 → 图像偏移

- 左移 / 右移

- 上移 / 下移

❗2️⃣ porch太小 → 不稳定

- 抖动

- 花屏

- 不显示

❗3️⃣ porch太大 → 帧率下降

👉 因为总像素变多了

九、ESP32里你是怎么用的

c

.timings = {

.h_res = 480,

.v_res = 272,

.hsync_back_porch = 40,

.hsync_front_porch = 20,

.vsync_back_porch = 8,

.vsync_front_porch = 4,

}👉 本质:

告诉硬件:这些时间你不要显示,只是走时序

十、给你一个工程级总结(很关键)

👉 porch 本质就是:

"同步信号和有效数据之间的缓冲区"

十一、一句话彻底记住

👉 有效像素 = 你要显示的内容

👉 porch = LCD还没准备好 / 已经显示完的时间

十二、如果你要进阶(强烈建议)

下一步你可以搞:

- 如何根据屏规格书算 porch(超实用)

- PCLK怎么算才刚好60Hz

- 为什么有的屏必须DE模式

如果你把你现在用的那块屏型号发我,我可以帮你:

👉 把整套 porch + PCLK + 时序参数全部算好(直接能用)

👉 顺便帮你避免花屏/偏移问题