1. 概述

1.1 config_db的核心价值

UVM配置数据库(uvm_config_db)是UVM验证框架中至关重要的基础架构,它提供了全局的、类型安全的配置信息共享机制。通过config_db,验证组件可以在不直接引用彼此的情况下进行数据交换和参数配置。

1.2 config_db解决的问题

在复杂的验证环境中,config_db解决了以下关键问题:

systemverilog

// 问题示例:硬编码配置的局限性

class problematic_env extends uvm_env;

my_agent agent;

function void build_phase(uvm_phase phase);

agent = my_agent::type_id::create("agent", this);

// 硬编码配置,缺乏灵活性

agent.item_count = 100;

agent.error_rate = 5;

endfunction

endclass1.3 config_db的优势

- 解耦合:组件间无需直接引用

- 灵活性:运行时动态配置

- 类型安全:编译时类型检查

- 层次化:支持精确的作用域控制

- 可调试:完整的配置追踪能力

2. uvm_config_db的使用方法

在UVM验证入门(2)-uvm常用类的继承关系文中的第5章说明了uvm_config_db这个类的继承关系:uvm_resource_db->uvm_config_db。uvm_resource_db是一个单独的工具类,不是从uvm_object中继承来的,提供配置管理服务,不需要实例化。

2.1 uvm_config_db常用的方法

systemverilog

class uvm_config_db #(type T=int) extends uvm_resource_db #(T);

// 设置配置值

static function void set(uvm_component cntxt,

string inst_name,

string field_name,

T value);

// 获取配置值

static function bit get(uvm_component cntxt,

string inst_name,

string field_name,

inout T value);

endclassset方法参数说明

- cntxt (上下文): 一个 uvm_component 实例的指针,与 inst_name 共同构成目标路径。可为 this、null (等价于 uvm_root::get()) 或 uvm_root::get()。

- inst_name (实例名): 相对于 cntxt 的实例路径字符串。与 cntxt 一起组成完整路径。

- field_name (字段名): 配置项的标识符字符串。

- value (值): 要存储的配置值,类型由 uvm_config_db#() 指定。 get方法参数说明

- 前三个参数与set方法一致。第四个参数 value 是引用参数,用于接收获取到的值。

systemverilog

class config_checker extends uvm_component;

`uvm_component_utils(config_checker)

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

// 检查配置是否存在,避免不必要的get操作

if (uvm_config_db#(int)::exists(this, "", "debug_level")) begin

`uvm_info("CFG", "Debug level configuration found", UVM_MEDIUM)

// 只有确认存在时才进行获取

uvm_config_db#(int)::get(this, "", "debug_level", debug_level);

end else begin

`uvm_info("CFG", "Using default debug level", UVM_MEDIUM)

debug_level = 0; // 默认值

end

endfunction

endclassexists 方法用于检查配置数据库中是否存在指定的配置项。它可以在尝试获取配置之前先检查配置是否存在,避免不必要的错误报告或提供条件逻辑。 exists参数说明

- cntxt:上下文组件,通常为this或null。

- inst_name:实例名,相对路径。

- field_name:字段名。

systemverilog

class dynamic_component extends uvm_component;

`uvm_component_utils(dynamic_component)

virtual task run_phase(uvm_phase phase);

// 监控配置变化

forever begin

// 等待配置被修改

uvm_config_db#(int)::wait_modified(this, "", "operation_mode");

// 配置已更新,获取新值

int new_mode;

if (uvm_config_db#(int)::get(this, "", "operation_mode", new_mode)) begin

`uvm_info("CFG", $sformatf("Mode changed to: %0d", new_mode), UVM_MEDIUM)

handle_mode_change(new_mode);

end

end

endtask

endclasswait_modified() 方法会阻塞当前进程,直到指定的配置项被修改。这对于需要动态响应配置变化的组件特别有用,允许运行时重配置而无需重启仿真。 wait_modified参数说明

- cntxt:上下文组件。

- inst_name:实例名。

- field_name:字段名。

2.2 配置设置示例

在UVM验证环境中,配置设置通常在测试类的build_phase阶段完成。这是配置信息传递的起点,通过uvm_config_db::set方法将各种类型的配置信息存储到全局配置数据库中,供下层组件在构建时获取使用。

systemverilog

class test_base extends uvm_test;

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

// 设置虚拟接口:将总线接口实例传递给环境中所有以"agent"开头的组件

uvm_config_db#(virtual bus_if)::set(this, "env.agent*", "vif", bus_if_inst);

// 设置整型参数:配置agent组件的事务项数量参数

uvm_config_db#(int)::set(this, "env.agent", "item_count", 1000);

// 设置配置对象:传递复杂的配置对象,包含多个相关配置参数

uvm_config_db#(agent_config)::set(this, "env.agent", "config", agent_cfg);

// 设置字符串:全局配置测试名称,所有组件都可以访问

uvm_config_db#(string)::set(this, "*", "test_name", "reset_test");

endfunction

endclass2.3 配置获取示例

组件在build_phase阶段通过uvm_config_db::get方法从配置数据库中检索配置信息。这是配置信息传递的终点,组件根据获取的配置来初始化自身状态和行为。良好的错误处理机制确保配置缺失时能够及时发现和处理。

systemverilog

class my_driver extends uvm_driver;

`uvm_component_utils(my_driver)

virtual bus_if vif;

int item_count;

agent_config cfg;

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

// 获取虚拟接口:关键硬件接口,获取失败通常需要致命错误

if (!uvm_config_db#(virtual bus_if)::get(this, "", "vif", vif))

`uvm_fatal("NOVIF", "Virtual interface not found")

// 获取整型参数:可配置参数,提供默认值确保组件正常运作

if (!uvm_config_db#(int)::get(this, "", "item_count", item_count))

item_count = 100; // 默认值

// 获取配置对象:复杂配置对象,缺失时通常需要致命错误

if (!uvm_config_db#(agent_config)::get(this, "", "config", cfg))

`uvm_fatal("NOCFG", "Agent configuration not found")

endfunction

endclass2.4 通配符使用

UVM配置系统支持通配符路径匹配,提供了灵活的配置作用域控制。通过精确路径和通配符的组合使用,可以实现从精确控制到批量配置的不同粒度,满足复杂验证环境的层次化配置需求。 通配符的使用遵循特定的匹配规则:*匹配零个或多个字符,?匹配单个字符。这种灵活的路径匹配机制使得配置管理更加高效和可维护,特别是在包含多个相似组件的复杂验证环境中。

systemverilog

class hierarchical_config extends uvm_test;

virtual function void build_phase(uvm_phase phase);

// 精确路径配置

uvm_config_db#(int)::set(this, "env.agent0.driver", "delay", 1);

// 通配符配置 - 影响所有agent

uvm_config_db#(int)::set(this, "env.agent*", "item_count", 500);

// 全局配置

uvm_config_db#(bit)::set(this, "*", "coverage_enable", 1);

endfunction

endclass3. uvm_config_db的工作原理

3.1 配置数据库的内部结构

UVM配置数据库本质上是一个层次化的资源存储系统,采用基于作用域和名称的键值对机制来管理配置信息。这种结构设计使得配置信息能够按照验证环境的层次结构进行组织和管理,确保配置的精确传递和高效检索。 配置数据库的核心结构可以看作是一个三维的查找表:

| 作用域 | 实例名 | 字段名 | 值 |

|---|---|---|---|

| uvm_test_top | env.agent | "vif" | ● |

| uvm_test_top.env | agent | "config" | ● |

| uvm_test_top.env | * | "delay" | ● |

3.2 配置查找算法

当组件调用get()方法检索配置时,配置数据库执行一个精心设计的查找算法,按照特定的优先级顺序在层次结构中搜索匹配的配置项。这个算法确保了配置解析的一致性和可预测性。

systemverilog

// 伪代码:配置查找算法

function bit find_config(context, inst_name, field_name, output value);

// 1. 精确匹配:context + inst_name + field_name

if (find_exact_match(context, inst_name, field_name, value))

return 1;

// 2. 通配符匹配:context + wildcard_inst + field_name

if (find_wildcard_match(context, inst_name, field_name, value))

return 1;

// 3. 向上遍历父作用域

uvm_component parent = context.get_parent();

if (parent != null)

return find_config(parent, inst_name, field_name, value);

return 0;

endfunction3.3 配置的作用域规则

UVM配置系统遵循严格的作用域规则,这些规则决定了配置项的可见性和优先级。理解这些规则对于设计可预测的配置策略至关重要,特别是在复杂的层次化验证环境中。

systemverilog

class scope_demo extends uvm_test;

virtual function void build_phase(uvm_phase phase);

// 不同作用域的配置示例

// 全局作用域(最低优先级)

uvm_config_db#(int)::set(null, "*", "global_param", 999);

// 测试作用域

uvm_config_db#(int)::set(this, "*", "test_param", 100);

// 环境作用域

uvm_config_db#(int)::set(this, "env", "env_param", 200);

// 组件作用域(最高优先级)

uvm_config_db#(int)::set(this, "env.agent.driver", "driver_param", 300);

endfunction

endclass4. 高级用法

4.1 配置对象模式

配置对象模式是UVM中管理复杂配置参数的首选方法。通过将相关的配置参数封装在一个继承自uvm_object的配置类中,可以大大提高代码的可维护性和可重用性。这种方法特别适用于需要传递大量相关配置参数的场景,避免了频繁调用uvm_config_db的繁琐。

systemverilog

// 配置对象定义

class agent_config extends uvm_object;

`uvm_object_utils(agent_config)

int item_count = 100;

bit error_injection = 0;

int error_rate = 1;

string protocol = "BASIC";

function new(string name = "agent_config");

super.new(name);

endfunction

endclass

systemverilog

// 配置对象的使用

class config_based_test extends uvm_test;

agent_config agt_cfg;

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

// 创建并配置对象

agt_cfg = agent_config::type_id::create("agt_cfg");

agt_cfg.item_count = 2000;

agt_cfg.error_injection = 1;

agt_cfg.protocol = "ADVANCED";

// 设置配置对象

uvm_config_db#(agent_config)::set(this, "env.agent*", "config", agt_cfg);

endfunction

endclass4.2 运行时配置更新

UVM支持在仿真运行期间动态更新配置,这为实现复杂的测试场景和动态调整验证环境行为提供了可能。运行时配置更新通常发生在run_phase或其主要子阶段中,允许测试根据仿真进度或特定条件调整组件行为。

systemverilog

class dynamic_config extends uvm_test;

virtual task run_phase(uvm_phase phase);

phase.raise_objection(this);

// 初始配置

uvm_config_db#(int)::set(this, "env.agent", "speed_mode", 1);

#100ns;

// 运行时更新配置

uvm_config_db#(int)::set(this, "env.agent", "speed_mode", 2);

`uvm_info("CFG", "Configuration updated at runtime", UVM_MEDIUM)

phase.drop_objection(this);

endtask

endclass4.3 配置调试和诊断

配置调试是验证环境开发中的重要环节,特别是在配置复杂或层次较深的环境中。UVM提供了多种技术来诊断配置问题,包括配置存在性检查、配置值验证和配置跟踪等功能。

systemverilog

class debug_config extends uvm_test;

virtual function void build_phase(uvm_phase phase);

super.build_phase(phase);

// 设置配置前检查

int existing_value;

if (uvm_config_db#(int)::get(this, "env.agent", "item_count", existing_value))

`uvm_warning("CFG", $sformatf("Overwriting existing config: %0d", existing_value))

uvm_config_db#(int)::set(this, "env.agent", "item_count", 500);

// 验证配置设置

int verify_value;

if (!uvm_config_db#(int)::get(this, "env.agent", "item_count", verify_value))

`uvm_error("CFG", "Configuration set failed")

else

`uvm_info("CFG", $sformatf("Configuration verified: %0d", verify_value), UVM_HIGH)

endfunction

endclass4.4 推荐的配置步骤

遵循配置管理的最佳实践可以显著提高验证代码的质量和可维护性。这些实践涵盖了配置命名、设置时机、错误处理和设计模式等方面,是构建健壮验证环境的重要指导原则。

systemverilog

//推荐做法

class good_config_practices;

// 1. 在build_phase早期设置配置

// 2. 使用有意义的配置字段名

// 3. 为关键配置提供默认值

// 4. 使用配置对象封装相关参数

// 5. 在get()后检查返回值

endclass

systemverilog

// 避免的做法

class bad_config_practices;

// 1. 在run_phase中设置关键配置(可能太晚)

// 2. 使用模糊的字段名如"cfg1", "param2"

// 3. 忽略get()的返回值检查

// 4. 过度使用全局通配符

// 5. 在组件内部修改配置对象

endclass4.5 配置优先级管理

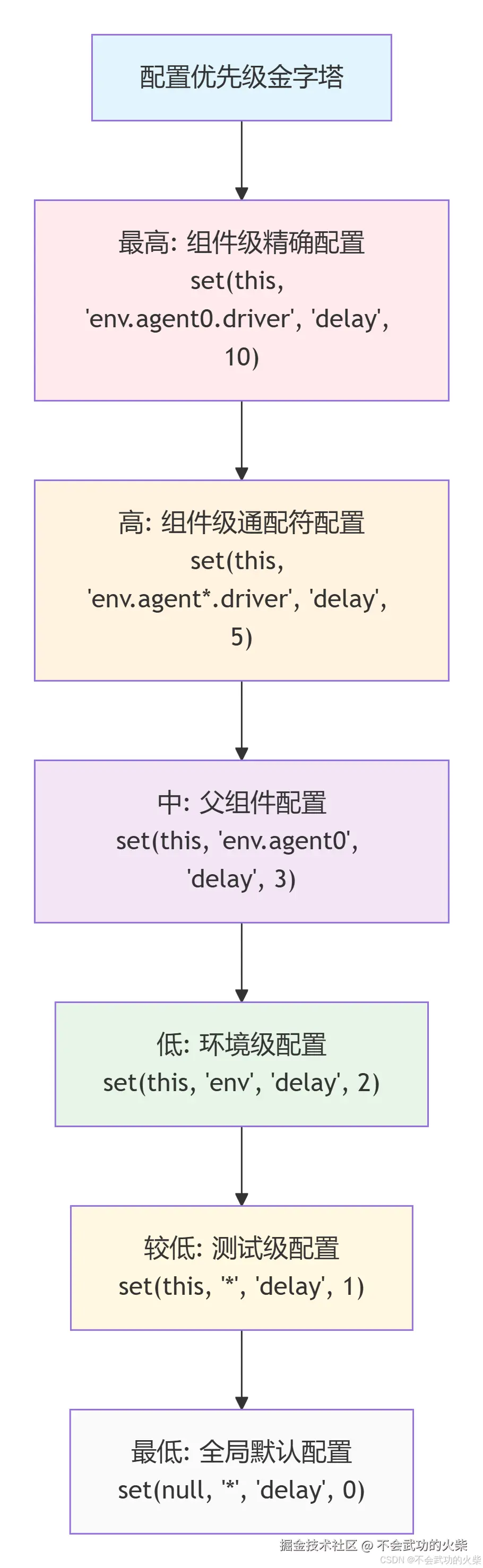

在复杂的验证环境中,合理的配置优先级管理是确保配置行为可预测的关键。通过建立清晰的优先级规则,可以避免配置冲突,确保在多层配置的情况下,系统能够按照预期的方式工作。

systemverilog

class priority_management extends uvm_test;

virtual function void build_phase(uvm_phase phase);

// 基础配置(低优先级)

uvm_config_db#(int)::set(this, "*", "base_timeout", 1000);

// 特定测试配置(高优先级)

if (test_type == "STRESS") begin

uvm_config_db#(int)::set(this, "env.agent", "timeout", 5000);

end

else if (test_type == "QUICK") begin

uvm_config_db#(int)::set(this, "env.agent", "timeout", 100);

end

super.build_phase(phase);

endfunction

endclass5. 总结

5.1 config_db的核心价值总结

uvm_config_db 机制是UVM验证方法学的基石之一,它提供了:

- 灵活的配置管理 - 支持各种数据类型的存储和检索

- 层次化作用域 - 精确控制配置的影响范围

- 类型安全 - 编译时确保数据类型正确性

- 运行时动态性 - 支持配置的动态更新

- 组件解耦合 - 消除组件间的直接依赖

5.2 在实际项目中的应用价值

基于大量实际项目经验,config_db的正确使用带来显著提升:

systemverilog

// 项目成功要素

class project_success_factors;

// 统一的配置接口标准

// 可重用的配置对象设计

// 清晰的配置作用域策略

// 完善的配置调试支持

// 团队一致的配置使用规范

endclassUVM配置数据库是验证平台中实现组件间松耦合通信的核心机制,它通过基于字符串路径的全局资源池管理配置信息,支持多种数据类型和运行时动态更新,采用层次化作用域规则和优先级查找算法,极大提升了验证环境的可重用性和可维护性。