第一部分:CPU 的内部"物流"体系

CPU 不只是一个算数器,它是一个高度自动化的指令加工厂。

1. 控制器:工厂的调度中心

- 程序计数器 (PC) :下一站预报员。存放下一条待执行指令的地址。具有自动加 1 功能。

- 指令寄存器 (IR) :正在加工的图纸。保存当前正在执行的指令内容(操作码+地址码)。

- 指令译码器 (ID) :翻译官。分析 IR 中的操作码,转化为控制各部件的电信号。

- 地址寄存器 (AR) :地址中转站。保存 CPU 当前访问的内存单元地址。

2. 运算器:工厂的加工车间

- 算术逻辑单元 (ALU) :核心工人。负责所有的算术运算和逻辑运算。

- 累加寄存器 (AC) :临时置物架。暂存运算结果,为下一次运算做准备。

- 状态条件寄存器 (PSW) :报警记录仪。记录进位、溢出、正负等状态信息。

第二部分:数据安全之"校验码"

为了防止数据在传输(物流)中变质,我们需要校验机制。

1. 奇偶校验码 (Parity Check)

- 原理:加 1 位校验位,使 1 的个数为奇数或偶数。

- 局限 :只能检错,不能纠错。只能发现奇数个比特位的翻转。

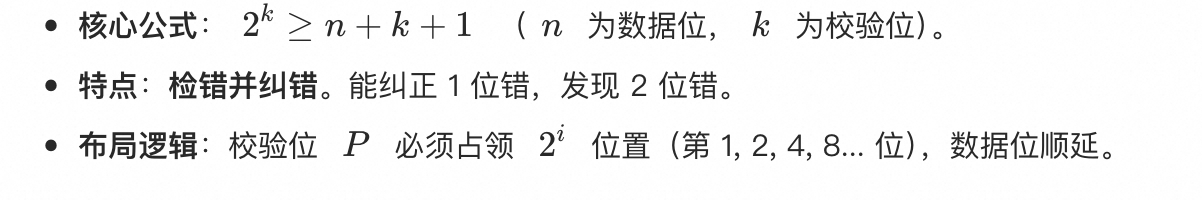

2. 海明校验码 (Hamming Code) ------ 精准定位

3. CRC 循环冗余校验码 ------ 工业级防伪

- 原理 :基于多项式除法(模 2 除法)。

- 步骤 :

- a:根据多项式最高幂次在数据后补 0。

- b:做模 2 除法(异或运算,不借位)。

- c:余数即为校验码。

- 判定:余数位数必须比生成多项式少一位。

第三部分:层次化存储体系

解决"CPU 极速"与"硬盘龟速"矛盾的权衡金字塔。

1. 存储层级与实物对应

|-------|------------------|------------------|------------------|

| 现实组件 | 考试术语 | 存储技术 | 关键特征 |

| CPU内部 | Cache (高速缓存) | SRAM (静态RAM) | 极快、不需刷新、贵 |

| 内存条 | 主存 | DRAM (动态RAM) | 较快、必须刷新、容量中等 |

| 硬盘 | 外存 | 磁性存储 / Flash | 慢、大、断电数据不丢失 |

2. 局部性原理

- 时间局部性:刚访问过的,过一会还要访问(如循环)。

- 空间局部性:刚访问过的隔壁,过一会也要访问(如数组顺序读)。

- 意义:Cache 就是基于此原理,提前把数据预加载到 CPU 身边。

第四部分:磁盘工作原理与优化计算

磁盘是唯一的机械组件,它是考场上的"时间计算"大户。

1. 物理结构

- 扇区:磁盘读写的最小单位。

- 磁道:盘片上的同心圆。

- 寻道时间:磁头前后摆动找磁道的时间(最慢)。

- 等待时间 :盘片旋转让扇区转到磁头下方的时间(平均按转半圈计)。

2. 磁盘读取的"错过"逻辑(难点)

-

现象:读完一块数据后,CPU 处理需要时间。在这段时间里,由于磁盘一直在转,紧挨着的下一块数据会滑过磁头。

-

非优化分布 :因为错过,读每一块都要多等一圈。

- 计算公式:10*(读取时间+等待一圈时间)。

-

优化分布 :将数据交错排列(如 R1 在 1 号位,R2 在 3 号位)。

- 计算公式:10*(读取时间+处理时间),完全消除旋转等待。

第五部分:核心计算题型"必杀技"

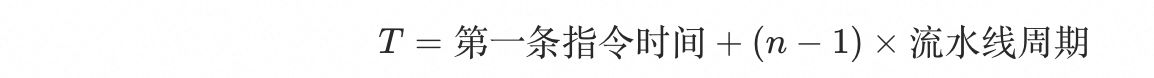

- 流水线时间 :

- 注:流水线周期 = 各阶段中最长的时间。

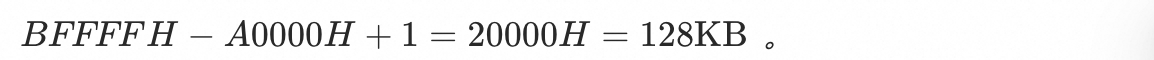

- 存储容量计算:

- 常考十六进制减法,如 :

- 海明码位数计算 :

快速记忆 序列:2, 4, 8, 16, 32... 找第一个大于等于数据位+校验位+1 的数字。

总结 :

理解计算机组成的关键在于看清**"数据流"。数据从 外存(磁盘)起跑,经由 主存(内存条/DRAM)**中转,在 **Cache(SRAM)**加速,最后进入 CPU 寄存器 被 ALU 处理。而在这个过程中,校验码 负责安全,控制器负责指挥。