**目前,DC-DC电源芯片由于小型化、高效率等要求,频率越来越高。在这种情况下,PCB布局设计的合理性将直接影响芯片性能表现,同时也会对其他信号质量产生重要影响。**不合理的PCB布板会造成芯片性能变差如线性度下降(包括输入线性度以及输出线性度)、带载能力下降、工作不稳定、EMI辐射增加、输出噪声增加等,更严重的可能会直接造成芯片损坏。

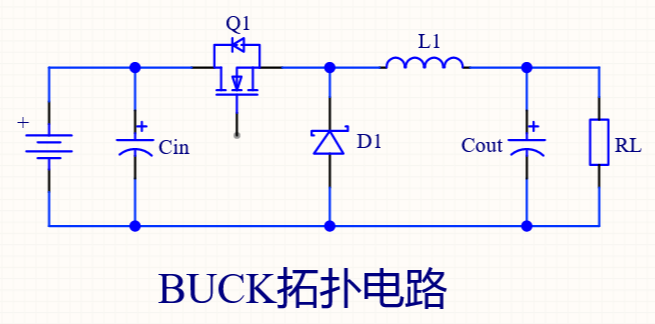

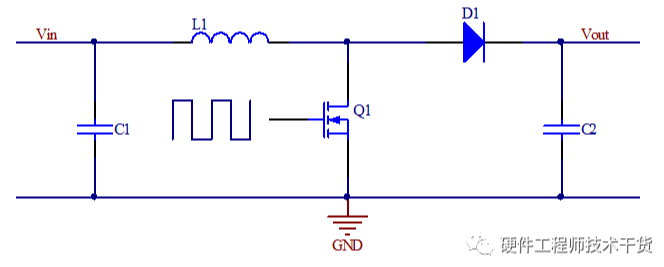

一、拓扑说明

1. 电流的环路面积尽可能小:

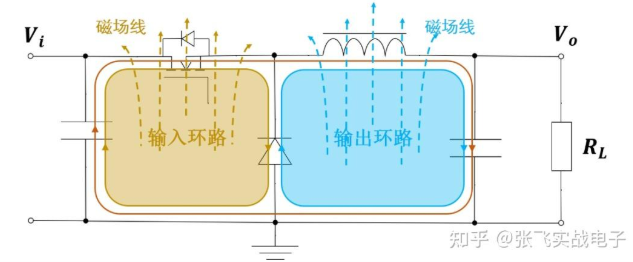

电流的环路可以看作一个环路天线,会对外辐射能量(参考无线充电线圈)。在PCB布线时,应让电流的环路尽可能小。当芯片的引脚设置不足与同时兼顾输入和输出环路最小时,应考虑以下两种情况。

- 对于DC-DC降压电路 (BUCK电路),输入环路不停的开关导致较大的di,因此di/dt较大,会产生较大的电磁波;而输出环路因为有电感存在,电流无法突变。此时应让输入环路尽可能小。

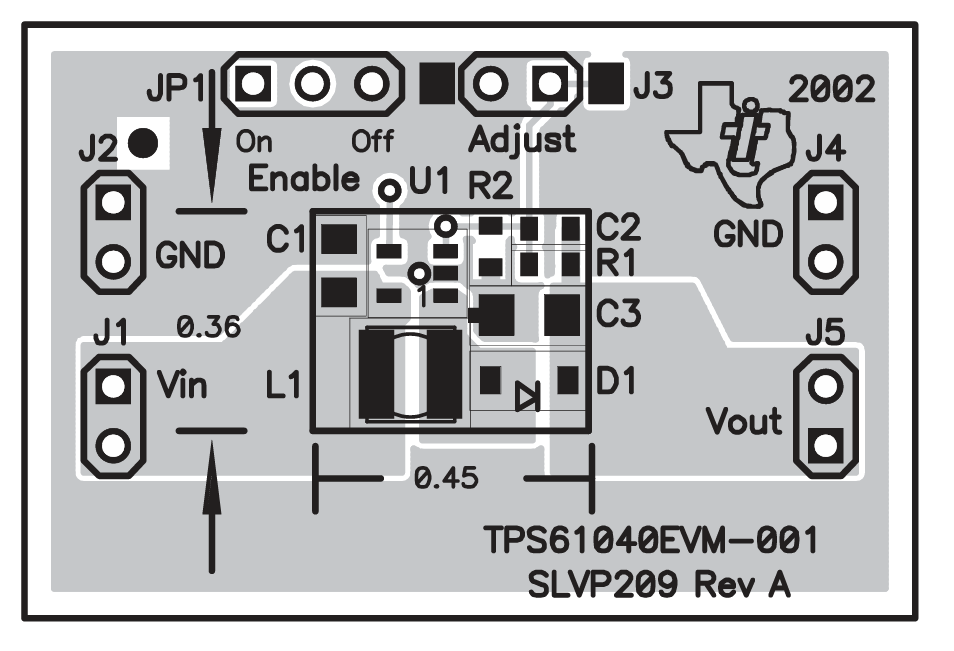

- 对于DC-DC升压斩波电路 (BOOST电路),输出环路不停的开关导致较大的di,因此di/dt较大,会产生较大的电磁波;而输入环路因为有电感存在,电流无法突变。此时应让输出环路尽可能小 。

2. 输入输出电容紧贴输入输出端:

输入端的电容紧贴芯片和电感的供电引脚。输出端的电容紧贴二极管的输出脚。如果是大电容和小电容的并联,电流先流过大电容,再流过小电容。

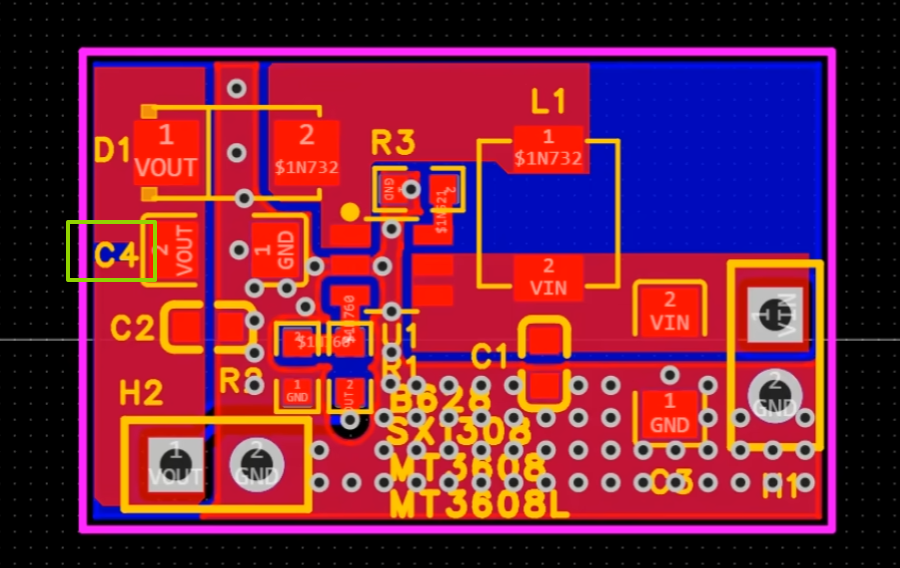

下图C4位置铺铜做了一个豁口,为的就是让电流流过大电容后,再流出,限制电流流向。

3. 电感紧贴芯片SW引脚:

由于电感处于输入输出环路中,因此,尽可能减少电感与SW引脚的距离就可以减小输入输出环路的面积,紧贴芯片的SW引脚能减少电磁波泄露。

二、走线说明

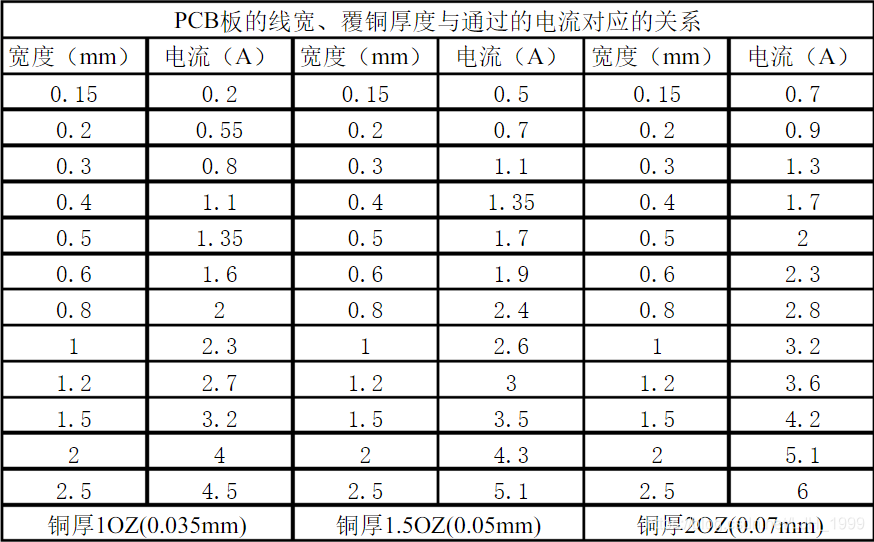

1. 铜箔线宽厚度应合适:

走线线宽不够,对于芯片的性能同样至关重要。

要按照需要设置走线宽度,在输入输出端走线时铜箔要足够宽 ,以供大电流经过;在反馈电阻走线时,要窄一些,与大电流的功率地单点相连,不要让大电流的功率地干扰小信号的信号地。

2. SW引脚避免铜箔过宽:

SW节点的高频电压跳变会形成有效的电场天线。大面积铺铜相当于扩大了天线面积,增强了向周围环境的放射状射频干扰。过多的铜箔可能导致邻近电路拾取噪声,影响信号完整性。

3. 高频路径和器件下方不走线:

高频路径及器件在工作时产生强大的变化磁场,任何在其正下方的信号线都会成为"接收天线",引入严重的开关噪声,干扰信号质量。

三、选型说明

1. 芯片选型:

芯片有三种类型,PSM脉冲跳跃模式;PFM脉冲频率调制;PWM脉冲宽度调制。

- PSM脉冲跳跃模式:通过工作--休眠--工作的方式,跳过部分脉冲,实现轻载下的效率提升。一般芯片会在负载电流低于设定的阈值时,自动进入PSM模式。

- PFM脉冲频率调制:开关脉冲宽度一定,通过改变脉冲输出的频率,使输出电压达到稳定。PFM控制型即使长时间使用,尤其小负载时具有耗电小的优点。

- PWM脉冲宽度调制:开关脉冲的频率一定,通过改变脉冲输出宽度,使输出电压达到稳定。PWM控制型效率高并具有良好的输出电压纹波和噪声。

多数芯片会采用PWM+PSM的方式,但PSM模式会导致电源纹波增大并不适合某些情况。

2. 电容选型:

电容的选型主要是满足耐压和降低纹波,选用上使用低纹波的电容,同时耐压值一般为输入输出电压的1.5~2倍。

3. 二极管选型:

4. 电感选型:

电感的饱和电流应在电路最大电流的1.2倍以上。同时对于电路频率>500KHz的电路,尽量使用屏蔽电感,减小漏磁,同时提高转换效率。

屏蔽电感与非屏蔽电感的选择上,大电流时,使用屏蔽电感会降低涡流从而提升转换效率;电流较小时(<100mA),可选用半屏蔽电感拥有较高性价比;非屏蔽电感视情况使用。

5. 反馈电阻选型:

通常FB反馈网络处的分压电阻都采用K级,10K级或上百K的阻值,阻值越大,越容易受干扰。

四、铺铜说明

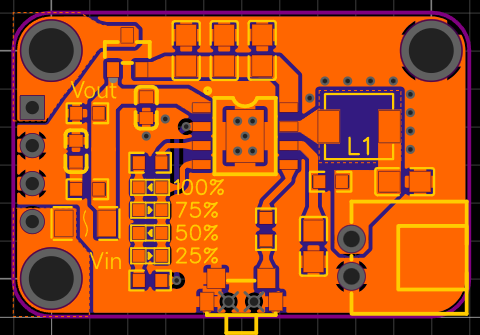

1. 顶层铺铜说明:

- 芯片底下散热铜,芯片散热不好会导致效率低下,影响正常工作。因此芯片下面要进行铺铜,同时通过过孔连接底层或其他层的公共地层,增加散热。如果芯片有散热引脚,可以使用十字连接,同时打满过孔,方便焊接和散热。

- 电容接地引脚铺铜时要选用直连的方式,进一步减小纹波。

- 电感正下方顶层外扩1~2mm区域禁止铺铜,涡流对电感的影响。同时底面接地铺铜或中间接地层不进行挖空,进行电磁屏蔽。电感顶层禁止铺铜的挖空区域在周围打上接地过孔,降低干扰。

- 如果对于干扰不敏感,追求高效率,可以选择顶层和底层都进行挖空,这样没有涡流干扰,转换效率更高。

2. 底层铺铜说明:

底层铺铜要尽量保证连续性,可以减小回路面积,降低干扰

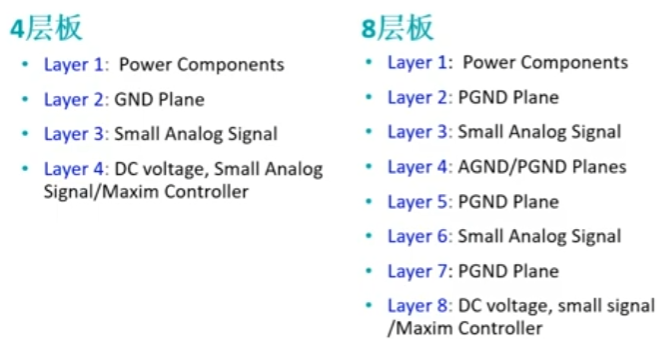

四、多层板板层分配说明

4层和8层板典型设计: