本篇 PLL 锁相环实验和 MIO 应用 ,选自ALINX 黑金云课堂 FPGA 免费直播课。该课程由 ALINX 资深工程师团队倾力打造,从 0 到 1 系统化教学,帮助每位工程师跨过 FPGA 开发门槛。

🔍 ALINX :关注 ALINX,进入视频号即可查看完整黑金云课堂 FPGA 视频教程。配合笔记学习效果更佳。

PLL 锁相环实验

实验目的

- 理解 PLL 在 FPGA 中的作用

- 掌握 Clocking Wizard 的基本使用方法

- 学会判断 PLL 是否锁定

- 建立"系统逻辑必须依赖稳定时钟"的工程意识

PLL 基本概念

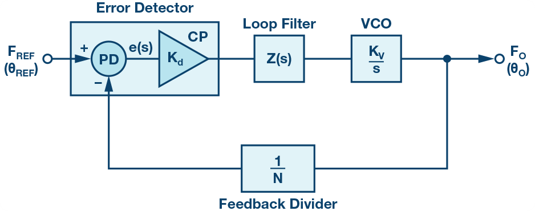

- PLL 锁相环是一种反馈控制系统,通过比较输入参考时钟与反馈时钟的相位差,调整压控振荡器(VCO)的输出频率,使输出时钟与输入时钟保持相位锁定关系。

(PLL 基本框图:鉴相器 → 环路滤波器 → VCO → 分频器 )

- 作用

- 生成多频率时钟

- 列表项消除时钟抖动

- 调整时钟相位

- 保证时序收敛

- 关键特性

- 频率合成: 可从单一参考时钟生成多种频率

- 相位同步: 输出时钟与参考时钟保持固定相位关系

- 快速锁定: 现代 FPGA PLL 可在微秒级完成锁定

PLL与MMCM对比

| 维度 | MMCM | PLL |

|---|---|---|

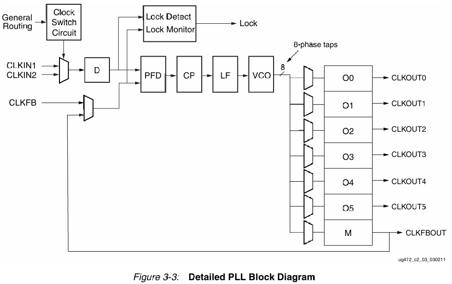

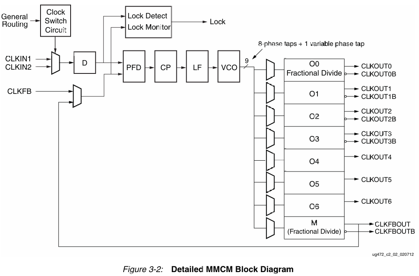

| 相位输出 | 9 路相位(8固定+1可变),支持精细动态相位调整 | 8 路固定相位,相位调整步长较大 |

| 分频能力 | 支持分数分频,可实现非整数倍频率转换,精度极高 | 仅支持整数分频,仅能实现整数倍频率转换 |

| 输出通道 | 7 组输出(O0~O6),O0~O3 及反馈端支持差分输出 | 6 组输出(O0~O5),仅支持单端输出,无差分端 |

| 适用场景 | 高速接口(SerDes/PCIe)、非整数倍时钟、差分时钟、高精度相位需求 | 通用逻辑时钟、整数倍频率转换、低功耗、资源紧张场景 |

| 性能功耗 | 抖动抑制更强,时钟更纯净;硬件资源 / 功耗略高 | 结构精简,功耗更低;性能满足基础需求 |

PLL 主要功能

- 时钟倍频

PLL 可以将输入的低频时钟倍频为高频时钟输出。例如,将 50MHz 的输入时钟倍频为 100MHz、200MHz 甚至更高频率,满足高速逻辑电路的时钟需求。

- 时钟分频

PLL 同样可以将高频时钟分频为低频时钟。这在需要为不同模块提供不同时钟频率的系统中非常有用,如为低速外设提供合适的时钟频率。

- 相位调整

PLL 可以精确调整输出时钟的相位,实现时钟相位的超前或滞后。这在需要精确控制数据采样时刻的高速接口设计中至关重要,如 DDR 内存控制器。

- 抖动抑制

PLL 具有良好的低通滤波特性,可以有效抑制输入时钟的高频抖动,输出更加稳定纯净的时钟信号。这对于保证高速数字系统的可靠性至关重要。

PLL 工程搭建

- Clocking Wizard IP

Vivado 提供的 Clocking Wizard 是一个强大的 IP 核,可简化 PLL 配置流程。通过图形化界面,用户无需手动编写复杂约束,即可快速生成满足需求的时钟管理模块。

*工具优势:时序自动优化、稳定性保证、易于维护

- 配置流程

配置输入时钟频率→配置输出时钟→生成 PLL 逻辑

接口信号说明

- clk_in

PLL 的输入参考时钟,通常来自板载晶振或外部时钟源。这是 PLL 产生输出时钟的基准信号。

*典型频率:50MHz, 100MHz, 200MHz

- clk_out

PLL 产生的输出时钟,其频率、相位由配置参数决定。这是系统逻辑实际使用的时钟信号。

- locked

PLL 锁定指示信号,高电平表示 PLL 已完成锁定,输出时钟稳定可用。

locked = 1 PLL已锁定,输出时钟稳定可用 locked = 0 PLL未锁定,输出时钟不稳定

*在工程中,通常使用 locked 信号控制系统复位。只有在 locked 为高电平时,才释放系统复位,确保所有逻辑在稳定时钟下运行。

Verilog 核心代码

-

PLL 复位控制

// PLL 复位控制逻辑// 确保系统逻辑在 PLL 锁定后才运行always @(posedge pll_clk or negedge pll_locked) begin

if (!pll_locked)

sys_rst <= 1'b1; // PLL 未锁定,系统保持复位

else

sys_rst <= 1'b0; // PLL 已锁定,释放系统复位

end

作用:避免不稳定时钟导致亚稳态、时序错误

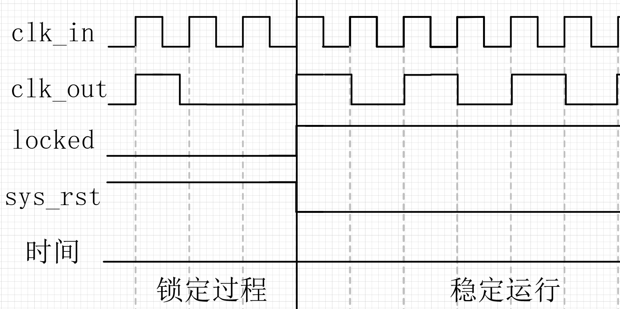

仿真与波形分析

- 仿真波形图

- 波形特征

上电初期 locked 为低,时钟不稳定;锁定后 locked 拉高,时钟稳定

MIO 应用

- 核心概念

GPIO:通用输入输出,是软件可调用的 I/O 信号集合,包含 78 路 MIO 与 288 路 EMIO(96 入 + 192 出)。

MIO:PS 端引脚复用控制器,用于信号路由、分时复用,解决 PS 引脚数量有限问题。

MIO 与 GPIO 关系:78 路 MIO 引脚同时属于 GPIO;GPIO 是软件控制接口,MIO 负责将信号路由到物理引脚。

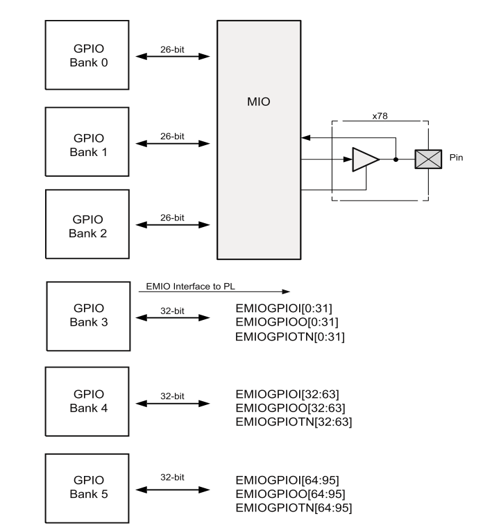

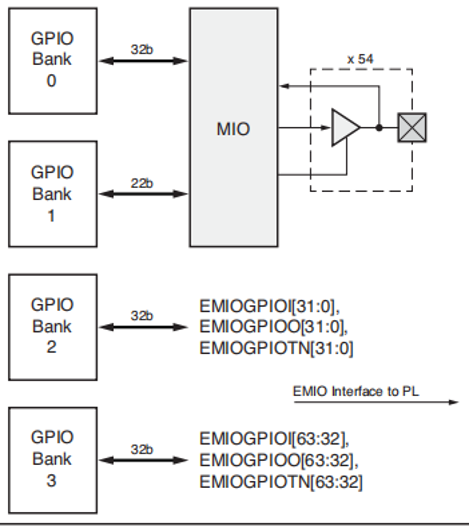

- 引脚分布

MIO 分为 3 个 Bank:Bank0 (26bit)、Bank1 (26bit)、Bank2 (26bit),合计 78 路。

EMIO 分为 Bank3/4/5,各 32bit,用于 PS 与 PL 端交互。

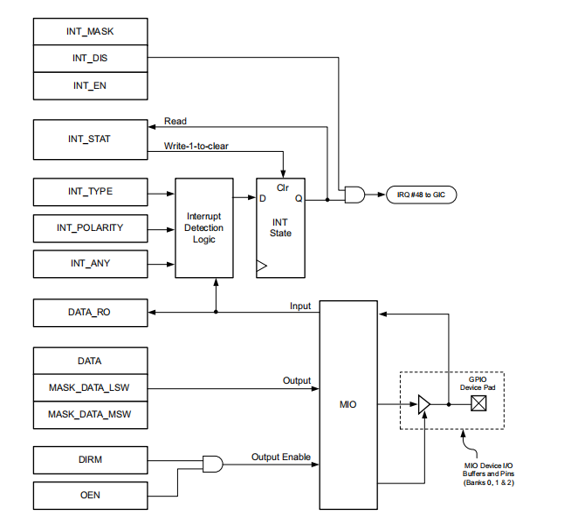

- GPIO 寄存器框架

分为中断检测 与数据读写两部分。

支持上升沿 / 下降沿 / 双边沿 / 高电平 / 低电平五种中断触发方式。

包含方向控制 (DIRM)、输出使能 (OEN)、数据输入 / 输出、中断使能 / 屏蔽 / 状态等关键寄存器。

(GPIO 框架)

更多细节欢迎关注我们黑金云课堂全年免费直播课, 黑金云课堂四月直播日历 我们将在每周二、三、四,同步推进 Verilog开发、Vitis开发、Linux开发三大系列,带你从零开始,稳扎稳打掌握 FPGA 开发全流程!

| 系列 | 内容定位 |

|---|---|

| Verilog开发 | 硬件描述语言基础、逻辑设计、仿真调试 |

| Vitis开发 | Zynq软硬件协同、外设驱动、网络协议栈 |

| Linux开发 | 嵌入式Linux系统移植、驱动编写、应用开发 |