目录

[CAPL 编程语言](#CAPL 编程语言)

[ZCANPRO 的软件架构](#ZCANPRO 的软件架构)

[基于 FPGA 的通讯控制器设计](#基于 FPGA 的通讯控制器设计)

[MCU 架构与工业级稳定性](#MCU 架构与工业级稳定性)

[DBC 与交互层(IL)开发](#DBC 与交互层(IL)开发)

[UDS 诊断协议栈与 ISO-TP](#UDS 诊断协议栈与 ISO-TP)

[ODX 与诊断数据库的继承机制](#ODX 与诊断数据库的继承机制)

[Vector XL Driver Library (vxlapi.dll)](#Vector XL Driver Library (vxlapi.dll))

[ZLG ControlCAN API](#ZLG ControlCAN API)

[第五部分:HIL 系统集成与 FPGA 自定义逻辑开发](#第五部分:HIL 系统集成与 FPGA 自定义逻辑开发)

[VT 系统:模块化 HIL 硬件开发](#VT 系统:模块化 HIL 硬件开发)

[用户可编程 FPGA (User FPGA)](#用户可编程 FPGA (User FPGA))

[Trace 窗口的渲染工程](#Trace 窗口的渲染工程)

[日志文件系统:BLF 格式与高效读写](#日志文件系统:BLF 格式与高效读写)

[第七部分:现代开发工作流与 DevOps 集成](#第七部分:现代开发工作流与 DevOps 集成)

[Headless 执行与容器化部署](#Headless 执行与容器化部署)

第一部分:软件架构设计与仿真引擎开发

事件驱动型仿真引擎与实时调度

Vector CANoe 的软件架构基于高度模块化的事件驱动模型。与传统的循环轮询机制不同,CANoe 的核心引擎由总线事件触发,包括报文接收、信号变更、系统变量修改或定时器到期。这种设计确保了在处理 CAN FD(数据段最高 8 Mbps)时 CPU 资源的高效利用。

剩余总线仿真(Remaining Bus Simulation) 是核心功能。通过导入 DBC 或 LDF 网络描述文件,仿真引擎自动生成虚拟节点,模拟缺失 ECU 的行为。这需要软件层具备一个高度优化的交互层(Interaction Layer),负责管理报文发送周期、计数器更新和校验和计算。

CAPL 编程语言

CAPL(Communication Access Programming Language)是 Vector 工具链的核心------一种类 C 的专用领域语言(DSL),针对汽车总线操作深度优化。

CAPL 的执行机制介于编译器与解释器之间。源代码首先在 CAPL 浏览器中编译,转化为高效的 P-code,在测量开始时加载到运行环境执行。这种预编译机制保证了高总线负载下的实时响应能力。

CAPL 设计上刻意省略了指针操作,代之以系统变量和关联数组,从根本上消除了内存越界导致的仿真系统崩溃风险。运行环境支持多线程并行处理,能同时运行多个仿真节点和分析模块而互不干扰。

ZCANPRO 的软件架构

ZLG 的 ZCANPRO 侧重于工业 兼容性 与二次开发的便捷性 。核心 API 库 ControlCAN.dll(或新版 ZCAN API)是国内行业标准。

ZCANPRO 开发重点在于强大的插件系统 和协议解析能力,支持 CANopen、DeviceNet、J1939、iCAN 等多种高级协议。通过虚拟滚动(Virtual Scrolling)和多级缓存机制,Trace 窗口能流畅显示每秒数万帧报文而不产生 GUI 延迟。

| 软件特性 | Vector CANoe (Professional) | ZLG ZCANPRO (Analyst) |

|---|---|---|

| 核心执行环境 | 事件驱动型预编译环境 | 过程化解析与实时分析环境 |

| 脚本支持 | CAPL, .NET, C#, Python | Python, C++, LabVIEW |

| 仿真能力 | 全系统剩余总线仿真 (SIL/HIL) | 基本节点仿真与协议分析 |

| 诊断集成 | 深度集成 ODX, CDD, UDS | 侧重协议层解析与简单诊断 |

| 云端支持 | 支持 Docker 容器化与 CI/CT | 侧重本地 workstation 性能 |

第二部分:硬件架构与高精度总线接口开发

基于 FPGA 的通讯控制器设计

高端网络接口(如 Vector VN1640A)的开发核心在于 FPGA。不同于依赖通用 MCU 内置 CAN 控制器的低端适配器,高端工具在 FPGA 内部实现 CAN/LIN 的底层逻辑。

FPGA 化设计的三大核心优势:

-

100% 总线负载支持:硬件自主处理每一帧报文的仲裁、校验和应答,不占用主控处理器带宽,确保高负载下不丢帧

-

高精度硬件时间戳:FPGA 内部纳秒级时钟在检测到 SOF(起始位)时立即记录,消除了 USB 传输延迟和操作系统中断延迟带来的抖动(Jitter)

-

协议扩展性:通过更新 FPGA 固件,可从经典 CAN 升级支持 CAN FD,甚至最新的 CAN XL

MCU 架构与工业级稳定性

ZLG USBCAN 系列更多利用高性能 MCU(如 NXP LPC54000 系列)的潜力。芯片内置双高速 USB 接口和多个 CAN 控制器,可通过片上物理层直接与总线收发器连接。

硬件开发关键:隔离耐压与电磁兼容性(EMC)。为防止车辆高压系统电压浪涌损坏 PC,硬件通道采用磁耦/光耦隔离,隔离电压可达 2500V DC。总线收发器(如 TJA1051)必须符合车规级标准,工作温度范围 -40°C 至 +85°C。

硬件同步与时间基准

多通道分析中同步精度是衡量工具质量的关键指标:

-

Vector 方案:专用同步电缆(SYNC)将多台 VN 接口时钟串联,由一台设备作为时钟源,通过差分信号分发同步脉冲,使整个测试系统时钟偏差控制在微秒以内

-

ZLG 方案:利用总线本身的事件或特定的硬件时钟管理逻辑实现多通道协同测量

| 硬件参数 | Vector VN1640A | ZLG USBCAN-II C+ | CandleLight (开源) |

|---|---|---|---|

| 主控架构 | 高性能 FPGA | 工业级 32-bit NXP MCU | STM32F0/F1 MCU |

| 总线通道 | 4 通道(支持可换模块) | 2 通道(固定) | 1 通道 |

| 时间戳精度 | 纳秒级(FPGA 锁存) | 微秒级(MCU 响应) | 软件中断级(有抖动) |

| 数据吞吐量 | 极高(支持 CAN XL) | 约 14,000 帧/秒 | 约 10,000 帧/秒 |

| 隔离技术 | 5 kV 高级隔离 | 2.5 kV 磁耦隔离 | 视 PCB 设计而定 |

第三部分:数据库解析与通讯协议栈开发

DBC 与交互层(IL)开发

DBC 文件解析是汽车工具开发的第一步。DBC 定义了矩阵式网络通讯的所有细节,包括信号位起始位置、位长度、偏移量(Offset)和缩放系数(Factor)。

物理值计算公式:

物理值 = (原始采样值 \\times 缩放系数) + 偏移

开发难点:每一帧进入系统的报文都要实时解析并映射到 GUI 信号树,大端(Motorola)和小端(Intel)字节序的处理需要极高的代码效率。

UDS 诊断协议栈与 ISO-TP

ISO-TP(ISO 15765-2)协议栈处理长报文是关键。由于 CAN 帧限制为 8 字节,长达几百字节的诊断请求必须进行拆分:

| 帧类型 | 缩写 | 说明 |

|---|---|---|

| 单帧 | SF (Single Frame) | 数据长度 ≤ 7 字节,一次性发送 |

| 首帧 | FF (First Frame) | 包含长报文的总长度信息 |

| 流控制帧 | FC (Flow Control) | 接收端告知发送端块大小(Block Size)和最小间隔时间(STmin) |

| 连续帧 | CF (Consecutive Frame) | 携带剩余的载荷数据 |

UDS(ISO 14229)应用层需实现各种服务 ID(SID):0x10(诊断会话控制)、0x27(安全访问,涉及 Seed-Key 算法)、0x22(通过 ID 读取数据)等。

ODX 与诊断数据库的继承机制

ODX(Open Diagnostic data eXchange)是基于 XML 的 ASAM 标准,采用面向对象的设计思想,支持"继承"和"引用"机制:

-

Base Variant (BV):定义基础诊断能力

-

ECU Variant (EV) :通过

<PARENT-REF>继承 BV,可重写特定参数 -

继承链解析:软件必须实时递归解析 XML 树,确定当前 ECU 变体所支持的最终服务集

ODX 解析引擎的开发要求团队具备极强的 XML 建模能力,并能将 UML 类图准确映射到软件的内存对象模型中。

第四部分:驱动程序与二次开发接口(API)设计

Vector XL Driver Library (vxlapi.dll)

Vector 的 XL Driver Library 是通用编程接口,支持从物理通道配置到报文收发的全流程控制。

核心设计精髓:"逻辑通道"与"物理通道"解耦 。开发人员只需面向"CAN 1"、"LIN 1"等逻辑端口编程,通过 Vector Hardware Config 灵活映射到具体 VN 系列硬件。API 引入了回调函数机制 和事件通知句柄(Event Handle),当硬件 FIFO 存入新数据时,驱动程序立即通过操作系统信号通知上层应用,实现极低响应延迟。

ZLG ControlCAN API

ZLG 的 ControlCAN.dll 在国内开发者群体中具有极高市场占有率,API 设计追求简洁直观。

核心函数:

-

VCI_OpenDevice:打开 USB 设备通道 -

VCI_InitCAN:设置波特率和验收滤波器 -

VCI_Transmit:将VCI_CAN_OBJ结构体阵列推送到硬件发送队列 -

VCI_Receive:从硬件缓冲区读取接收到的报文数据

驱动开发最大技术难点:如何管理硬件内部的 FIFO 缓冲区以防止高频率发送时的溢出,以及如何在 Windows 非实时环境下实现精确的定时发送。

第五部分:HIL 系统集成与 FPGA 自定义逻辑开发

VT 系统:模块化 HIL 硬件开发

Vector VT 系统(如 VT1004A / VT2004A)代表测试工具向物理层延伸的极致。每个 VT 模块不仅具有总线通讯能力,还集成了电子负载、电阻级联和信号发生器。

核心开发逻辑在于"信号调理(Signal Conditioning)":能模拟各种传感器故障(对地短路、对电源短路、引脚开路)。这种硬件级开发需要深厚的模拟电路设计功底,确保波形在电压和电流动态范围上完全符合汽车电气环境要求。

用户可编程 FPGA (User FPGA)

为应对 PSI5、SENT 或专有 PWM 编码等挑战性协议,VT 模块引入了用户可编程 FPGA。

开发流程:

暂时无法在飞书文档外展示此内容

通过将 FPGA 内部寄存器映射为 CANoe 系统变量,用户可在 CAPL 脚本中实现软件指令对硬件逻辑的毫秒级控制,无需更换物理硬件即可应对新型协议挑战。

第六部分:高性能可视化渲染与大数据处理

Trace 窗口的渲染工程

开发 Trace 窗口是复杂的高性能数据可视化工程。为处理百万级报文,开发人员使用"虚拟窗口技术":

-

GUI 层不维护所有报文的 UI 对象

-

根据滚动条位置动态提取内存索引中的数据

-

仅渲染屏幕可见的几十行

为实现高效数据过滤,软件底层构建多级索引树 。用户输入 ID 过滤条件时,系统通过位掩码(Bitmask)索引快速定位目标帧,过程必须在毫秒内完成。

日志文件系统:BLF 格式与高效读写

Vector 开发的 BLF(Binary Logging Format)是一种高度压缩的流式文件格式。

| 特性 | 说明 |

|---|---|

| 分块压缩 | 数据分为若干 Log Container,每个独立使用 ZLib 压缩。读取大文件时无需解压全部,通过偏移量表快速定位并解压指定时间段数据 |

| 多样化对象存储 | 一个 BLF 文件不仅存储 CAN 报文,还能同步存储系统变量、以太网包、外部音频/视频流的同步信息 |

| 多编译器兼容 | BLF 读写库需适配 MSVC、GCC 到嵌入式编译器的各种平台,支持在离线分析工具和车载数据记录仪(Data Logger)上的一致性表现 |

第七部分:现代开发工作流与 DevOps 集成

Headless 执行与容器化部署

现代 CANoe 开发重点之一是 "Headless" 运行能力。在无图形界面的 Linux 服务器或 Docker 容器中,CANoe 能以 API 形式被 CI 工具(Jenkins)调用。

开发人员将仿真配置、测试节点和 CAPL 代码打包,可在云端服务器上快速启动数千个仿真实例进行回归测试。软件架构需具备极强的进程隔离和资源管理能力,生成标准化的 JUnit 或 HTML 格式测试报告,实现从需求到测试结果的完整闭环(Traceability)。

软硬件重用策略 (SIL to HIL)

测试资产的跨平台重用是高级目标:在 SIL(软件在环)环境下开发的 CAPL 测试用例,无需修改即可直接运行在包含真实 VN 硬件和 VT 系统的 HIL(硬件在环)环境中。

软件层开发了一套抽象的**"通道管理层(Channel Mapping Layer)"**:

-

SIL 模式:通道映射到虚拟总线驱动程序

-

HIL 模式:通道映射到真实物理 FPGA 端口

这种一致性开发体验极大缩短了 ECU 验证周期。

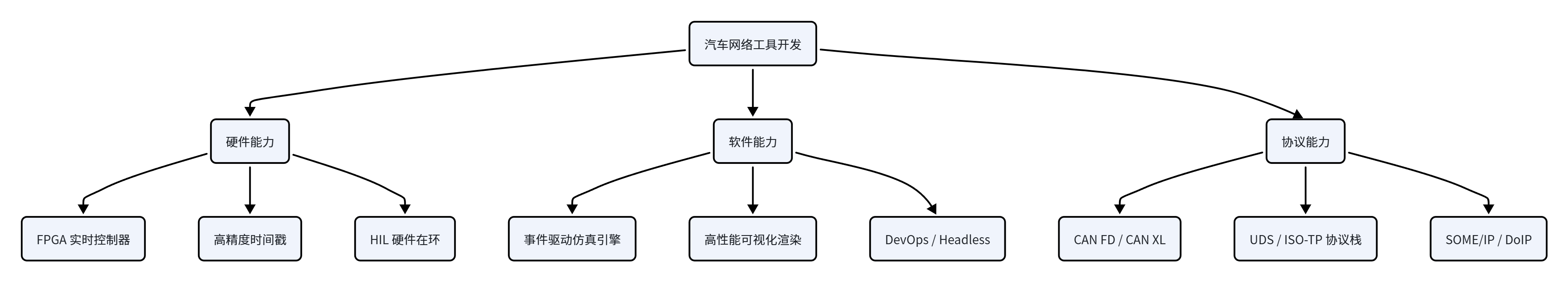

结论:汽车网络工具开发的演进路径

开发 CANoe 或 ZCANPRO 这类工具,是一项涉及底层硬件实时性与上层软件工程化的复杂系统任务。

硬件层面演进方向

-

处理 Automotive Ethernet(车载以太网) 带来的千兆级带宽挑战

-

通过 PTP(IEEE 1588) 协议在分布式系统中实现亚微秒级时间同步

-

架构进一步向 "高性能 SoC + 高端 FPGA" 方向演进,以处理 SOME/IP、DoIP 等复杂动态协议

软件层面演进方向

-

智能化:CAPL 的 AI 助手化

-

云化:基于云端的协同仿真

-

深度 SOA 解析:对面向服务架构的深度支持

核心能力矩阵