在语音唤醒、全双工对讲、便携录音等应用中,音频Codec的选型与外围设计直接影响系统的拾音质量、功耗及可靠性。本文基于一款典型高性能Codec(TP9311)的技术参数,梳理实际工程中易被忽视的关键点,并提供分析与设计建议。

一、电源架构与模拟性能

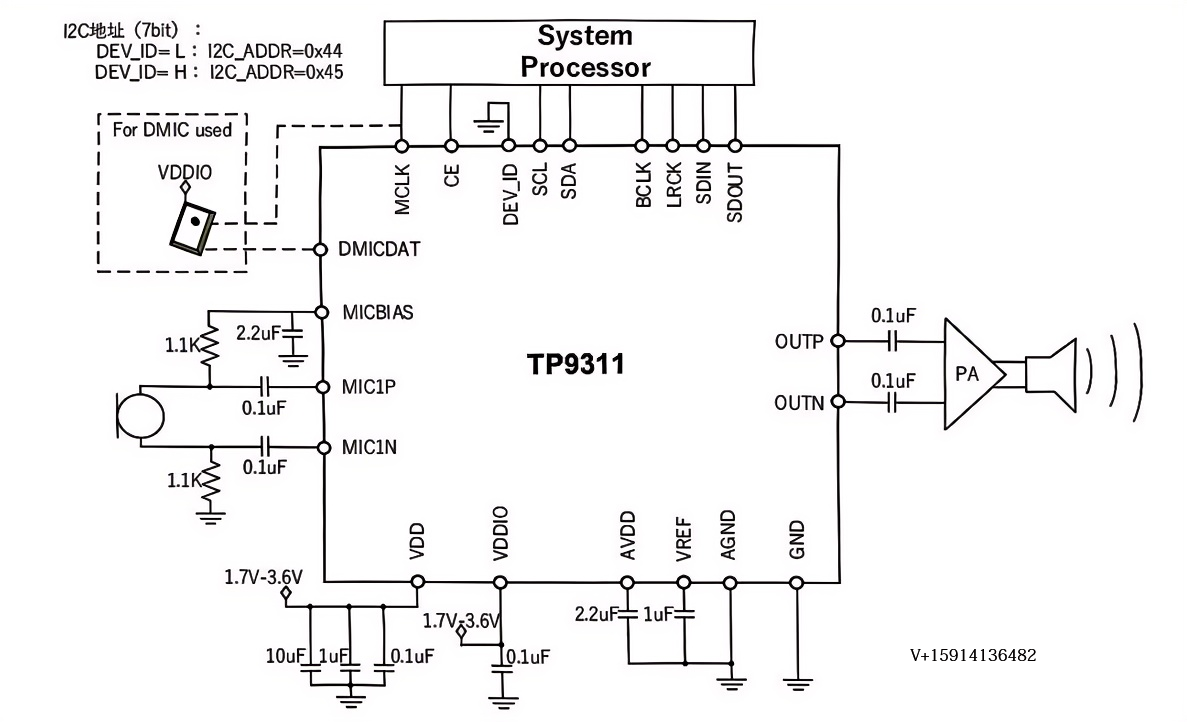

1. 内部LDO的使用条件

TP9311内部集成了两个独立LDO(ALDO、DLDO),用于为模拟和数字核心供电。手册中有一项关键约束:

当VDD电压低于1.7V时,须在PCB上将VDD与AVDD短接。

这意味着在电池供电设备中,若电源可能跌落至1.7V以下(如电机堵转、射频发射瞬间),内部LDO将失去调整能力。此时若仍将AVDD视为独立稳压输出,会导致模拟电路工作点偏移,表现为ADC底噪上升、增益异常。

设计建议:

-

评估系统最恶劣供电电压,若低于1.7V,应在原理图中预留VDD-AVDD短接电阻位置。

-

若长期工作于1.8V以上,可利用AVDD为外部模拟电路提供低噪声电源,但需注意其最大输出电流能力(手册未明确给出,建议实测)。

2. MICBIAS噪声与滤波

手册标称MICBIAS在20Hz-20kHz带宽内积分噪声为3.3μVrms(A计权),属于极低水平。但实际产品中,若PCB布局不当,MICBIAS走线可能耦合开关电源纹波或数字时钟串扰,导致实测噪声远超手册值。

常见故障:安静环境下录音有明显"嘶嘶"声或周期性"嗡嗡"声。

排查与对策:

-

MICBIAS输出引脚(Pin15)对地应放置10μF+0.1μF并联电容,且电容靠近芯片引脚。

-

走线远离DC-DC电感、数字总线(如I²S、I²C),必要时包地处理。

-

若使用驻极体麦克风,偏置电阻应靠近麦克风端,避免长线拾取干扰。

二、时钟架构与PLL配置

1. 非标准时钟输入的处理

TP9311内置可编程PLL,支持输入频率范围0.512MHz至20MHz。当系统主控提供的MCLK为非音频标准频率(如24MHz、26MHz)时,PLL需配置小数分频以生成目标采样率(如16kHz、48kHz)。

潜在问题:

-

PLL锁定范围与精度:若寄存器配置不当,实际输出采样率与标称值存在ppm级偏差,长期运行时I²S接口会因时钟累积误差导致左右声道错位或数据丢失。

-

功耗增加:手册电气参数表注:非标准时钟输入时PLL附加功耗约0.5mA。

设计建议:

-

优先选用音频标准晶振(12.288MHz、6.144MHz等),以简化PLL配置并避免小数分频引入的微相位噪声。

-

若无法更换主控晶振,需严格按照手册中PLL分频系数计算公式配置寄存器,并在量产前进行至少24小时连续音频流压力测试,验证I²S同步稳定性。

2. 数字麦克风时钟复用冲突

Pin2为MCLK/DMICCLK复用脚。当使用数字麦克风时,该引脚输出DMIC时钟;若系统同时存在外部有源晶振驱动MCLK,可能造成电平竞争或时序冲突。

故障现象:数字麦克风输出数据随机丢位、底噪突增,或主控无法识别PDM流。

解决方案:

-

使用数字麦克风时,MCLK应由芯片内部PLL产生并从Pin2输出,不可同时连接外部晶振输出。

-

若需外部高精度时钟源,应将外部时钟直接供给数字麦克风,同时将TP9311配置为使用内部PLL作为音频主时钟,并禁用Pin2的时钟输出功能。

三、输出级设计与POP噪声抑制

1. 单端耳机驱动时的偏置建立

TP9311的DAC输出为差分结构(OUTP/OUTN),支持单端模式驱动耳机。手册声明"无爆音",但实际工程中仍可能因上电时序或VREF电容选择不当产生POP声。

机理分析:

- 芯片上电后,内部VREF(Pin16)需要一定时间充电至稳定值(通常为AVDD/2)。若VREF外接电容过大,建立时间延长,DAC输出级在VREF未稳定前便偏置到工作点,造成输出端直流跳变,经隔直电容耦合至耳机产生冲击。

设计规范:

-

VREF引脚外接电容不宜超过手册推荐值(典型1μF-2.2μF)。增大电容虽可降低噪声,但会延长启动时间,需折中。

-

软件初始化时,在设置DAC通路之前,应先等待VREF稳定(可通过延时或查询内部状态位),再使能DAC输出。

2. 软件辅助静音策略

TP9311提供平滑音量调节和自动静音功能。即使硬件设计合理,仍建议在软件层面增加防护:

-

上电初始化时,将DAC数字音量设置为最低,待VREF稳定后渐进恢复目标音量。

-

进入低功耗休眠前,先执行音量淡出并静音DAC,再关闭模拟模块电源。

四、ESD与系统级防护

1. 芯片级ESD等级与实际系统防护

手册标注HBM模型±8000V,CDM模型±500V。该数值表征芯片本体在标准测试条件下的耐受能力,不等于产品整机可承受同等静电冲击。

实际风险点:

- 麦克风输入端(MIC_P/MIC_N)通常通过接插件或金属网罩与外界接触,静电放电可能直接注入芯片引脚,且放电波形前沿极陡(ns级),可能超过芯片内部保护结构的响应速度。

推荐防护网络:

-

在MIC_P、MIC_N靠近输入连接器处,串联10Ω-33Ω电阻,对地并联低结电容TVS管(结电容<10pF,避免影响音频频响)。

-

PCB布局应保证TVS管到连接器的走线尽可能短,以减小寄生电感。

2. I²C引脚的开漏特性

SCL/SDA引脚为开漏结构,须外接上拉电阻至VDDIO。上拉电阻阻值应根据总线电容和通信速率选择(400kHz时通常为2.2kΩ-4.7kΩ)。若遗漏上拉电阻,总线将无法产生高电平,导致通信失败。

五、功能模块的合理利用

1. PGA增益分配与噪声优化

ADC前端PGA提供0-42dB增益范围,步进3dB。增益分配需权衡信号摆幅与噪声:

-

PGA增益设置过低,后续数字域需软件增益补偿,导致量化噪声放大。

-

PGA增益设置过高,强信号可能削顶失真。

建议:根据典型使用场景声压级(如近讲、远场)确定合适PGA值,将ADC输入电平控制在-6dBFS至-3dBFS区间,兼顾动态范围与THD+N。

2. 片上DSP功能的应用边界

TP9311内置HPF、EQ、DRC等处理单元,可分担主控DSP负载。需注意:

-

HPF截止频率固定(手册未明确具体值,需实测或查阅寄存器说明),适用于滤除次声频段的风噪和直流偏移,但对人声频段内干扰无效。

-

DRC可防止ADC过载,但压缩参数(阈值、比率、起控时间)需根据实际语音动态调整,否则可能引起呼吸效应。

3. I²S接口时序约束

手册给出了详细的I²S主/从模式时序参数,其中:

-

从模式下,LRCK建立时间和保持时间最小为10ns。

-

SDOUT到BCLK的延迟最大为20ns。

在高速PCB设计中,若I²S走线过长或串入较大容性负载,可能导致时序违例。建议:

-

串联22Ω-33Ω阻尼电阻以抑制反射。

-

确保I²S总线对地电容不超过10pF。

六、常见故障排查速查表

| 故障现象 | 首要排查点 | 与TP9311相关的可能原因 |

|---|---|---|

| 上电后I²C无应答 | 检查DEV_ID引脚电平 | DEV_ID悬空导致地址不确定,须上拉或下拉。 |

| 录音底噪大 | 测量MICBIAS纹波 | MICBIAS滤波电容位置不当或容值不足。 |

| 数字麦输出异常 | 检查Pin2时钟波形 | MCLK与DMICCLK冲突,或PLL未正确配置输出。 |

| 耳机间歇性POP声 | 观察VREF上电波形 | VREF电容过大,建立时间过长。 |

| 长时间运行后音频卡顿 | 监测I²S帧同步 | PLL小数分频累积误差,建议改用标准晶振。 |

| MIC引脚易损坏 | 检查ESD保护电路 | 未加外部TVS/限流电阻,仅依赖芯片内部保护。 |

结语

音频Codec在语音交互产品中的角色常被低估。本文以TP9311的技术规格为基准,梳理了电源、时钟、模拟前端、输出驱动及ESD防护等环节的工程设计要点。所述问题及对策亦适用于其他同类Codec的评估与调试。实际设计时,请务必以芯片最新版数据手册及参考电路为准,并结合具体产品的机械结构、声学特性进行综合验证。

(本文基于TP9311数据手册V1.01参数及行业应用经验撰写,具体设计请以最新规格书为准。)