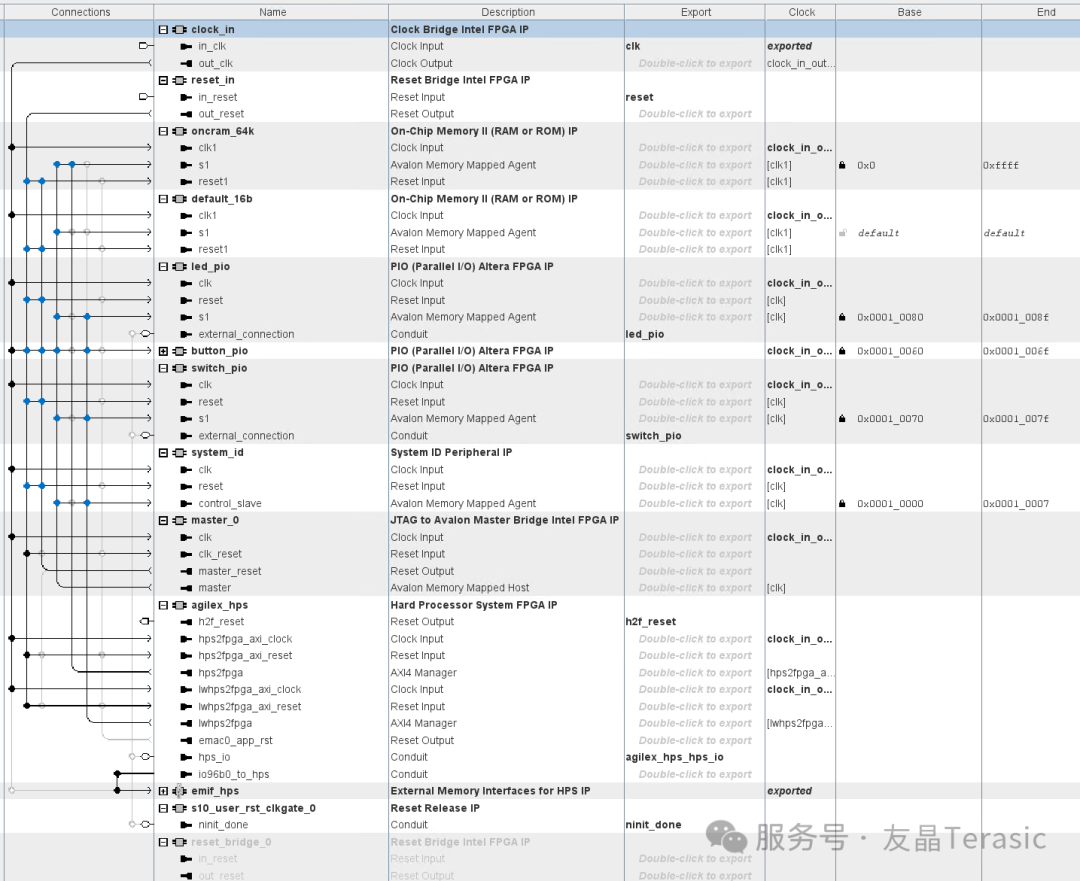

参考友晶官方的GHRD工程(下载地址:https://www.terasic.com.cn/cgi-bin/page/archive.pl?Language=China&CategoryNo=69&No=1392&PartNo=4#contents)做一个更小的SOC FPGA系统,其中IP架构如下:

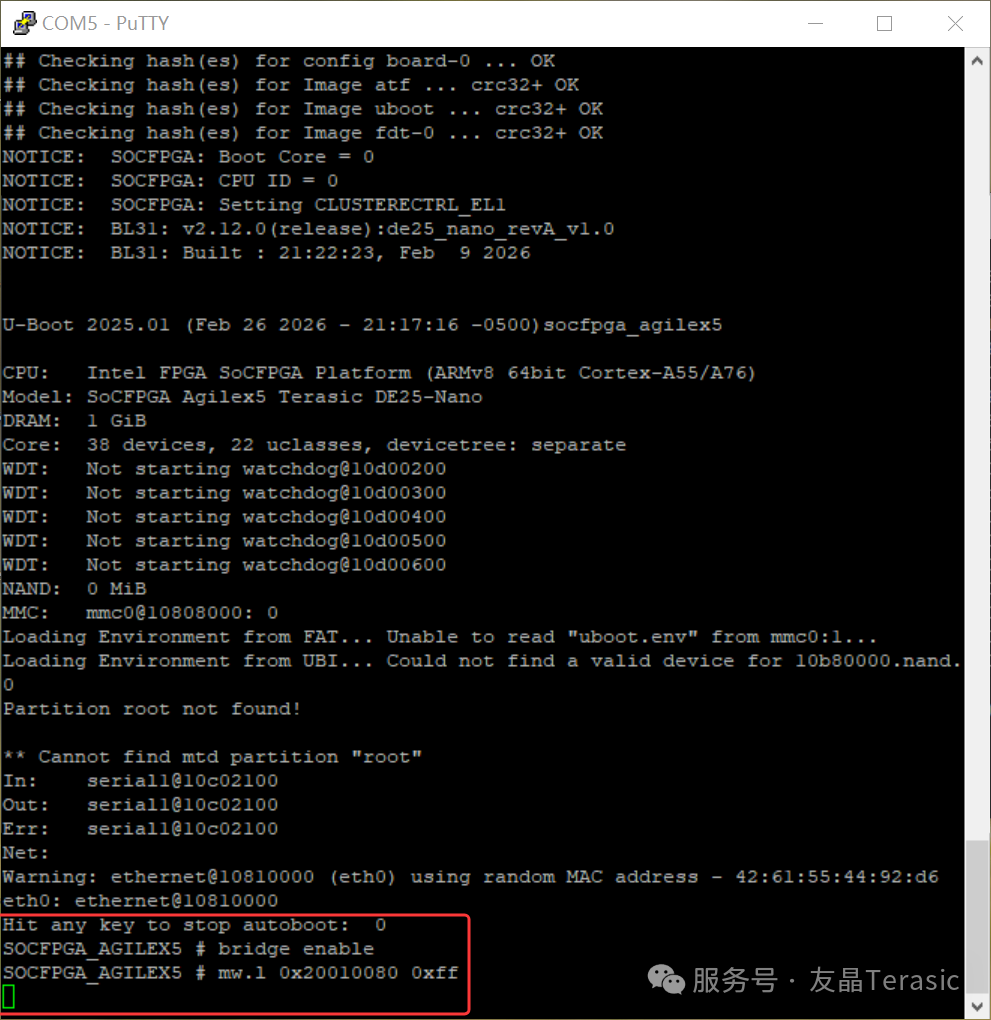

参考友晶官方提供的SD卡image制作教程https://github.com/johnnyfan1979/public_doc/blob/main/documentation/DE25_Nano/DE25%20Nano%20Build%20Linux%20image%20from%20scratch.md制作该更小系统对应的image,然后在DE25-Nano开发板上启动该镜像,在Uboot阶段按键盘任意键进入Uboot命令行输入环境,此时发现串口在下发mw.l命令后卡死了,如下图:

(1)首先检查hps bridge 和 pio 之间是怎么连接的

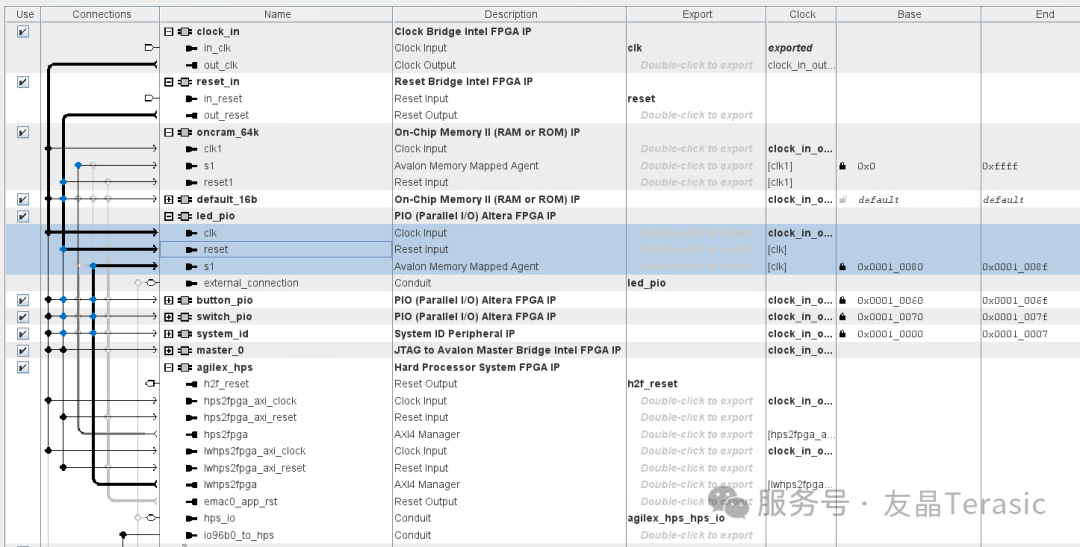

如下图led_pio的时钟和复位都已经连接到系统的时钟和复位了,led_pio的slave接口也和Agilex HPS IP 的lwhps2fpga相连,看起来没有什么问题。

(2)其次检查时钟和复位信号有没有什么问题

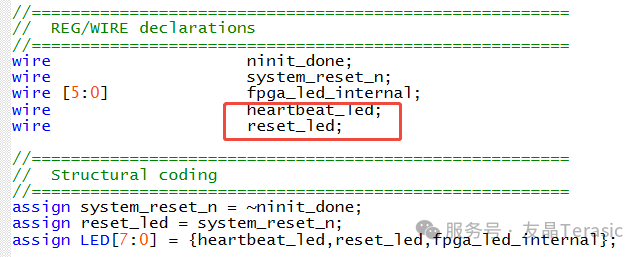

在工程top文件中增加heartbeat_led(对应时钟)和reset_led(对应复位)两个输出信号到LED进行信号指示的显示。

经测试发现heartbeat_led对应的LED闪烁,reset_led对应的LED熄灭。查看DE25-Nano的manual或者schematic file可以知道其LED是低电平点亮,高电平熄灭。看起来这两个信号是没有什么问题的。

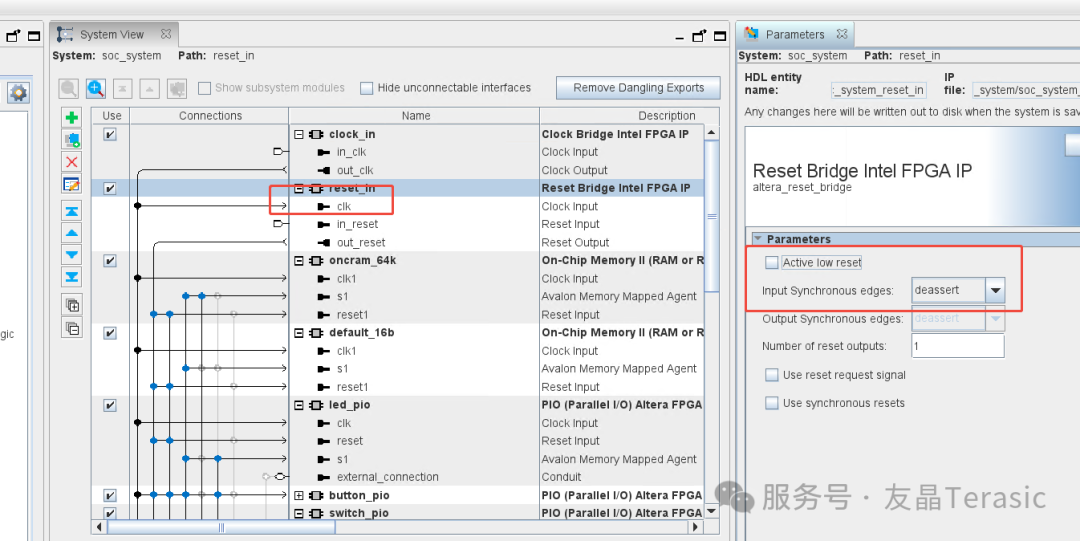

再仔细对比GHRD工程和当前更小系统工程发现GHRD的reset IP 设置的是active low, 而我的工程保持了默认值没有修改,是avtive high:

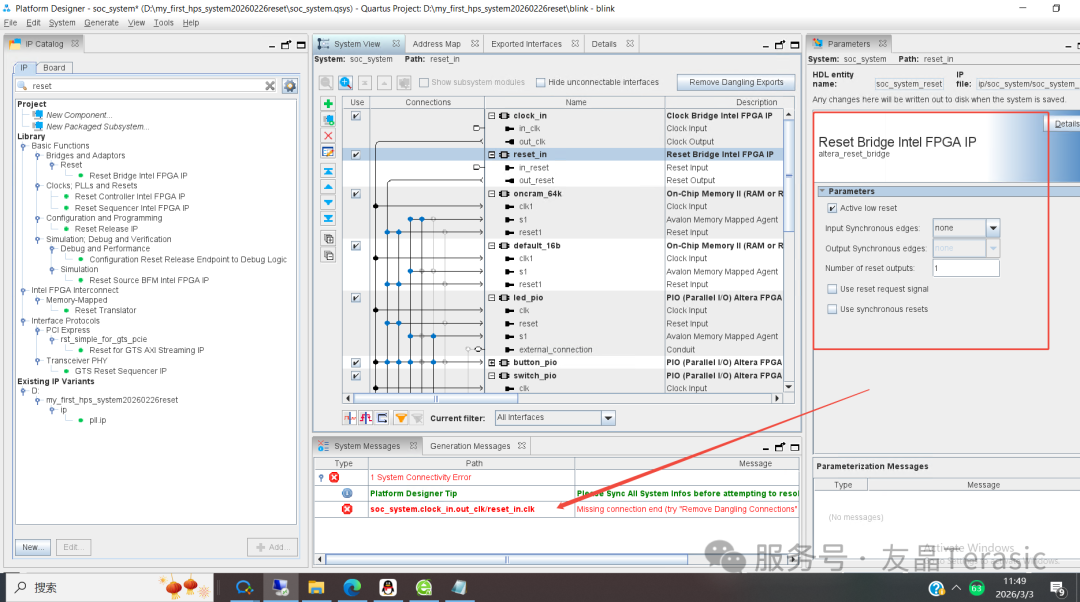

现在改成这样:

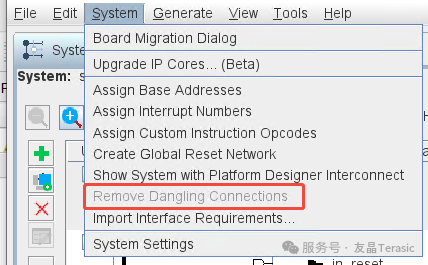

但是有报错,提示 soc_system.clock in.out clk/reset in.clk Missing connection end (try "Remove Dangling Connections。在Platform Designer 菜单选择System------Remove Dangling Connection, 这样操作以后就没有报错了。

重新生成Qsys文件,重新编译Quartus工程,重新烧写QSPI Flash,再次启动image进入Uboot阶段,再次发送mw.l 0x20010080 0x00 LED灯亮了,发送 mw.l 0x20010080 0xff LED灯灭了。问题就解决了!

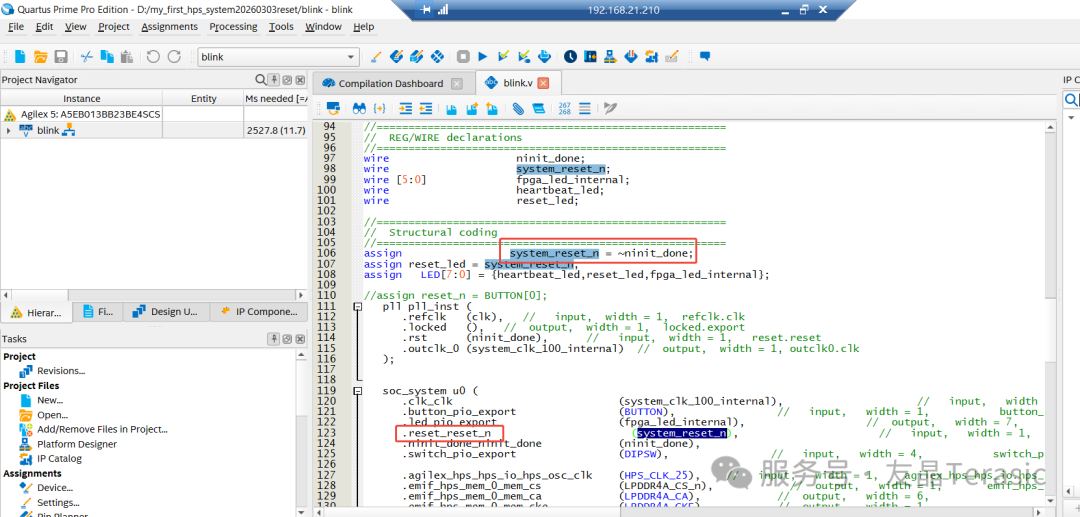

所以串口卡死的原因是:Reset Release Intel FPGA IP,其输出的 ninit_done 信号在 FPGA 配置完成后,从高电平跳变为低电平,而系统复位信号system_reset_n来自Reset Release Intel FPGA IP输出的 ninit_done 信号再取反:

当Reset Bridge Intel FPGA IP设置active high, 意味着你从外部接入的复位信号是reset(高有效), 系统配置完以后, system_reset_n是高电平,系统就会一直处于复位状态。

而当Reset Bridge Intel FPGA IP 设置active low, 意味着你从外部接入的复位信号是reset_n(低有效), 系统配置完以后, system_reset_n是高电平,系统已经离开复位状态。

往期阅读:

答疑解惑 | DE25-Nano开发板Uboot阶段与FPGA外设交互失败

DE25-Nano开发板在Programmer的 Auto Detect 下检测出来的器件和友晶官方提供的工程里器件不一样有没有关系?