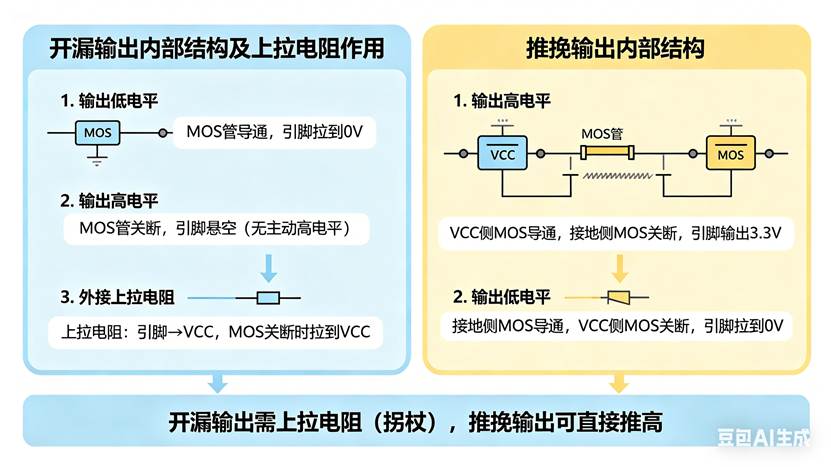

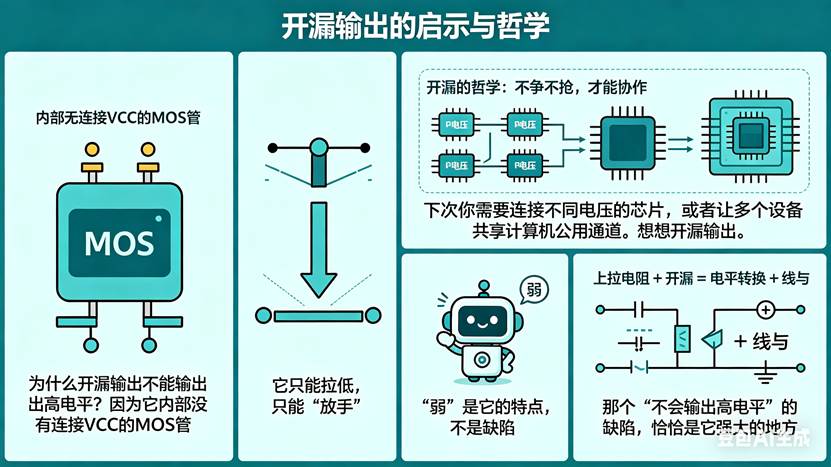

你有没有想过一个问题:GPIO输出高电平,不就是引脚输出3.3V吗?**开漏输出做不到。**它内部只有一个接地的MOS管。

- 输出低电平:MOS管导通,引脚拉到地(0V)

- 输出高电平 :MOS管关断,引脚什么都不接------悬空

它不会主动输出高电平,只会"放手"。 要让引脚变成高电平,必须在外面接一个上拉电阻。

那个"内部结构"的真相(对应教程3.4节), 推挽输出内部有两个MOS管:一个接VCC,一个接地。开漏输出内部只有一个接地的MOS管。输出高电平时,MOS管关断,引脚与内部电路断开 。引脚上的电压完全由外部电路 决定。它只能拉低,不能推高。

**那个"上拉电阻"的作用(对应教程3.6节),**接一个电阻从引脚到VCC(上拉电阻)。

- 输出低电平:MOS管导通,引脚0V(电阻电流流过MOS管)

- 输出高电平:MOS管关断,引脚被电阻拉到VCC

上拉电阻,是开漏输出的"拐杖"。 没有它,引脚浮空------电平不确定。

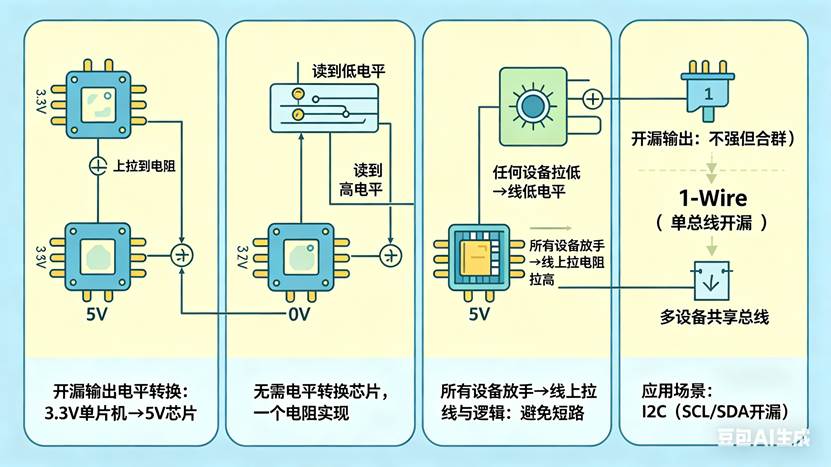

那个"电平转换"的妙用(对应教程3.4节), 3.3V的单片机和5V的芯片通信:开漏引脚接上拉电阻到5V。

- 单片机输出低电平 → 引脚0V → 5V芯片读到低电平

- 单片机输出高电平 → 引脚被电阻拉到5V → 5V芯片读到高电平

**3.3V单片机,直接驱动5V芯片。**不需要电平转换芯片,一个电阻就够了。

那个"线与"的逻辑(对应教程3.6节), 多个开漏输出可以接在同一条线上。任何一个设备输出低电平(拉低),整条线就是低电平。所有设备都"放手",线才被上拉电阻拉高。谁都能拉低,谁都不推高------避免短路。 这就是I2C总线使用开漏输出的原因。那个"应用"的场景

- I2C:SCL和SDA都是开漏

- 1-Wire:单总线,开漏

- 电平转换:3.3V ↔ 5V

- 多设备共享总线:多个输出接一起

开漏输出不强,但"合群"。

这个故事的启示, 为什么开漏输出不能输出高电平?因为它内部没有连接VCC的MOS管 。它只能拉低,只能"放手"。"弱"是它的特点,不是缺陷。 开漏的哲学:不争不抢,才能协作。

写在最后, 下次你需要连接不同电压的芯片,或者让多个设备共享总线。想想开漏输出。上拉电阻 + 开漏 = 电平转换 + 线与。那个"不会输出高电平"的缺陷,恰恰是它强大的地方。

(本文灵感源于于振南《新概念ARM32单片机》教程第3.4节"GPIO开漏模式与电平匹配",感谢作者将开漏输出的物理本质讲得如此通透。)

如果您觉得这个故事对您有启发,欢迎点赞、转发,让更多工程师看到这个藏在"只能拉低"背后的开漏智慧。