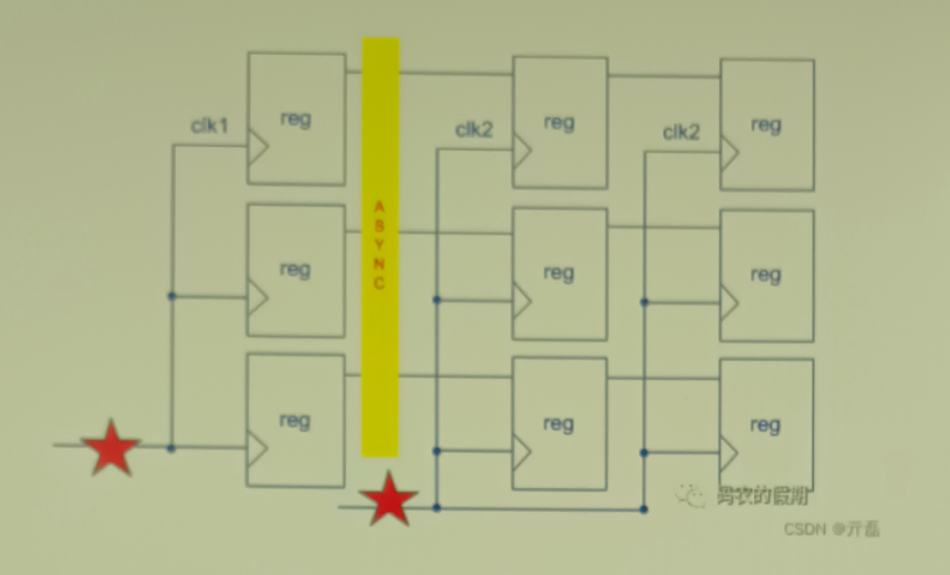

1.多 bit 数据在跨时钟域处理时一般都需要用到格雷码转换处理。单 bit 数据跨时钟域时一般直接打拍。多 bit 数据跨时钟域时如果也是直接打拍,不同 bit 达到被同步时钟域时的延时不一致导致功能错误问题。

异步 fifo 完成跨时钟域转换时,写数据和读数据分别位于读写不同时钟域。读写地址分别进行格雷码转换。因为读写地址是递增的方式,转换为格雷码后每次递增都只有 1bit 数据跳变,所以转换完后可以跟单 bit 同步方式一样打拍到对应的读写时钟域上(读地址格雷码转换后的地址打拍写时钟域,反之一样),完成空满状态判断。

2、set_max_delay 约束虽然读写地址转换为格雷码后每次地址递增只有 1bit 跳变,满足可以直接打拍的特性。但是格雷码总线信号还是多 bit 信号,每个 bit 信号延迟不一致,导致在目的时钟域采样的时候,有可能存在多 bit 同时翻转的问题现象。导致读写指针,空满标志判断出错,功能出错。

最大延迟约束(set_max_delay)将分析最大延迟路径上的建立时间分。保证多 bit 信号打拍时每个 bit 的最大延时是固定的,从而保证被同步时钟域采样正确。

3、格雷码转换

格雷码格雷码 (又称循环码),它具有以下两个特点:

- 相邻的两个编码之间只有一位是不一样的。

- 当第 N 位从 0 变到 1 时,之后的数的 N-1 位会关于前半段对称,而比 N 位高的是相同的。

**英文解释:**A Gray code is an encoding of numbers so that adjacent numbers have a single digit differing by 1

下图是格雷码和二进制码的一个对比:

表格

| Decimal | Binary | Gray Code |

|---|---|---|

| 0 | 000 | 000 |

| 1 | 001 | 001 |

| 2 | 010 | 011 |

| 3 | 011 | 010 |

| 4 | 100 | 110 |

| 5 | 101 | 111 |

| 6 | 110 | 101 |

| 7 | 111 | 100 |

由于格雷码相邻数据只有一个 bit 不同,因此,在进行跨时钟域传输时,只有发生变化的那个 bit 有可能处于亚稳态,而其余 bit 由于保持不变,因此是稳定的,故多比特格雷码的跨时钟域传输相当于单比特信号的跨时钟域传输,我们采用打两拍的方法即可处理。

格雷码和二进制码的转换

二进制转格雷码格雷码的产生是对二进制按位异或生成的,其 RTL 描述如下:

verilog

assign gray_code = (binary >> 1) ^ binary;格雷码转二进制码格雷码转换成二进制则需要对每位进行单独异或 (以 4bit 为例):Gray to Binary

verilog

b(3) = g(3)

b(2) = g(3) ^ g(2)

b(1) = g(3) ^ g(2) ^ g(1)

// 完整4bit转换还包含:b(0) = g(3) ^ g(2) ^ g(1) ^ g(0)4、异步 fifo 实现地址的格雷码与二进制转换及读写线转换实现:

verilog

always @ (posedge rd_clk )// or posedge rd_rst )

begin

if( rd_rst )

rd_ptr_gray <= {(AWIDTH){1'b0}};

else

rd_ptr_gray <= rd_ptr ^ (rd_ptr >> 1);

end

always @ ( posedge wr_clk )// or posedge wr_rst )

begin

if( wr_rst )

wr_ptr_gray <= {(AWIDTH){1'b0}};

else

wr_ptr_gray <= wr_ptr ^ (wr_ptr >> 1);

end

always @ ( posedge wr_clk )// or posedge wr_rst )

begin

if( wr_rst )

wr_full_pkt_num_gray <= {(AWIDTH){1'b0}};

else

wr_full_pkt_num_gray <= wr_full_pkt_num_d1 ^ (wr_full_pkt_num_d1 >> 1);

end

always @ ( posedge rd_clk )// or posedge rd_rst )

begin

if( rd_rst )

wr_ptr_gray_sync <= {(AWIDTH){1'b0}};

else

wr_ptr_gray_sync <= wr_ptr_gray;

end

always @ ( posedge wr_clk )// or posedge wr_rst )

begin

if( wr_rst )

rd_ptr_gray_sync <= {(AWIDTH){1'b0}};

else

rd_ptr_gray_sync <= rd_ptr_gray;

end

always @ ( posedge rd_clk )// or posedge rd_rst )

begin

if( rd_rst )

wr_full_pkt_num_gray_sync <= {(AWIDTH){1'b0}};

else

wr_full_pkt_num_gray_sync <= wr_full_pkt_num_gray;

end

// Gray to Binary conversion

always @ ( * )

for(i=0; i<AWIDTH-1; i=i+1)

begin

wck_rd_ptr[AWIDTH-i-2] = wck_rd_ptr[AWIDTH-i-1] ^ rd_ptr_gray_sync[AWIDTH-i-2];

end

always @(*)

begin

rck_wr_full_pkt_num[AWIDTH-1] = wr_full_pkt_num_gray_sync[AWIDTH-1];

for(i=0; i<AWIDTH-1; i=i+1)

begin

rck_wr_full_pkt_num[AWIDTH-i-2] = rck_wr_full_pkt_num[AWIDTH-i-1] ^ wr_full_pkt_num_gray_sync[AWIDTH-i-2];

end

end

always @(posedge wr_clk) // or posedge wr_rst)

begin

if(wr_rst)

wck_rd_ptr_sync <= {AWIDTH{1'b0}};

else

wck_rd_ptr_sync <= wck_rd_ptr;

end

always @(posedge rd_clk) // or posedge rd_rst)

begin

if(rd_rst)

rck_wr_ptr_sync <= {AWIDTH{1'b0}};

else

end

for(i=0; i<AWIDTH-1; i=i+1)

begin

wck_rd_ptr[AWIDTH-i-2] = wck_rd_ptr[AWIDTH-i-1] ^ rd_ptr_gray_sync[AWIDTH-i-2];

end

always @(*)

begin

rck_wr_full_pkt_num[AWIDTH-1] = wr_full_pkt_num_gray_sync[AWIDTH-1];

for(i=0; i<AWIDTH-1; i=i+1)

begin

rck_wr_full_pkt_num[AWIDTH-i-2] = rck_wr_full_pkt_num[AWIDTH-i-1] ^ wr_full_pkt_num_gray_sync[AWIDTH-i-2];

end

end

always @(posedge wr_clk) // or posedge wr_rst)

begin

if(wr_rst)

wck_rd_ptr_sync <= {AWIDTH{1'b0}};

else

wck_rd_ptr_sync <= wck_rd_ptr;

end

always @(posedge rd_clk) // or posedge rd_rst)

begin

if(rd_rst)

rck_wr_ptr_sync <= {AWIDTH{1'b0}};

else

end