5.5 LOGIC BIST ARCHITECTURES

将offline BIST技术融入设计的几种架构已经被提出,他们最终都会被归为四大类:

- 假设被测试电路没有特殊结构

- CUT电路用了scan chains技术

- 配置了scan chains用于pattern generation和output response analysis

- 用到了concurrent checking (implicit test) 的电路

这里只讨论每种类型的代表性BIST架构,要看更多的研究就建议参考文献了。

5.5.1 BIST Architectures for Circuits without Scan Chains

第一个BIST架构就是包括pseudo-random pattern generator、a single-input signature register或者multiple-input signature register,能测组合逻辑和时序逻辑电路,并且没有任何特殊的结构。这种架构经常用于board or system level

5.5.1.1 A Centralized and Separate Board-Level BIST Architecture

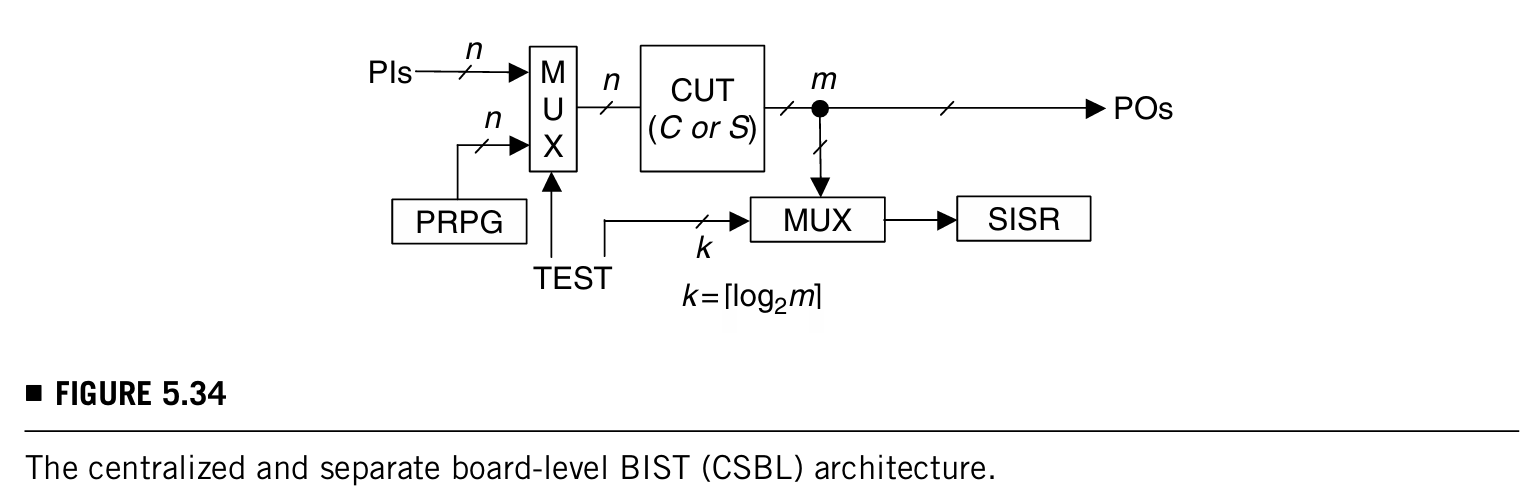

下图展示的就是一个centralized and separate board-level BIST architecture (CSBL)的架构图,可从文献中参考:

5.5.1.2 Built-In Evaluation and Self-Test (BEST)

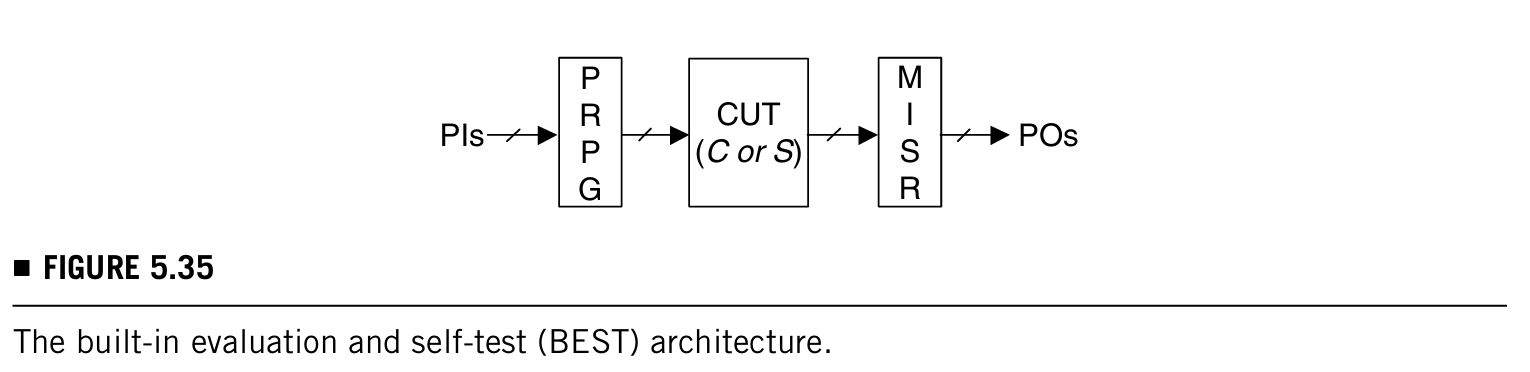

这个方法的架构图如下图,也可以从文献中参考到:

5.5.2 BIST Architectures for Circuits with Scan Chains

对于包含scan chains的设计,可以利用这个scan结果形成BIST电路,这种架构通常被叫做test-per-scan BIST system。

5.5.2.1 LSSD On-Chip Self-Test

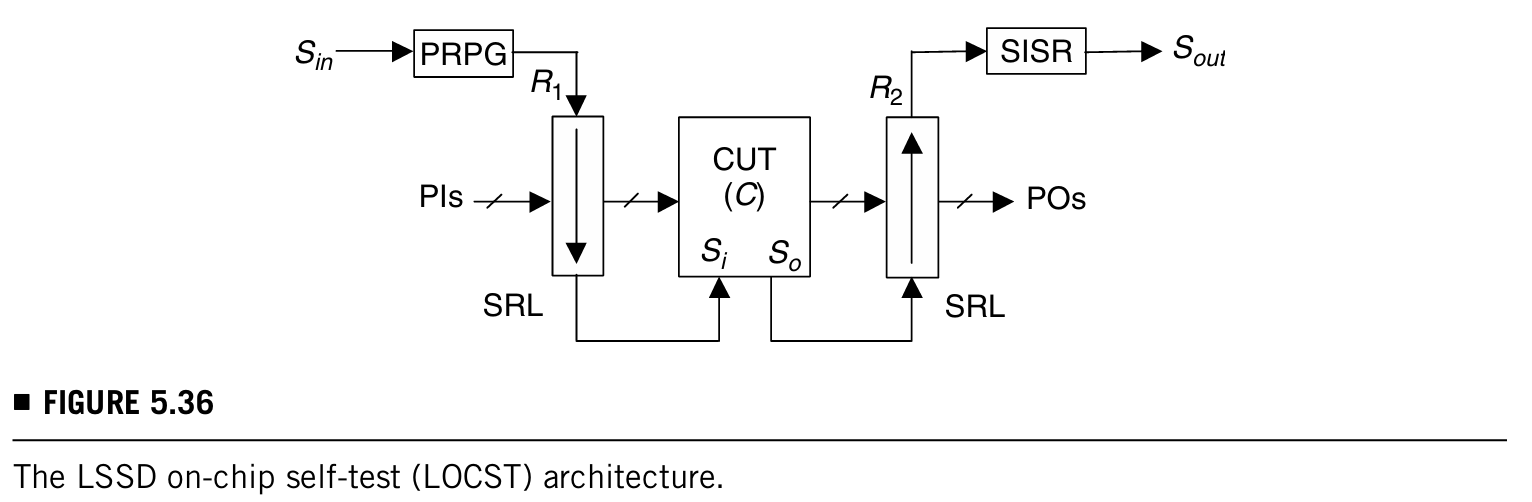

用scan chains做的BIST电路见下图架构图,也可参考到文献:

这个叫做LSSD on-chip self-test (LOCST)架构,除了内部有个scan chain是由LSSD shift register latches (SRLs)组成,还有一个外部的all primary inputs and primary outputs都包括在内的scan chain,外部scan chain的输入接到内部scan chain的输出上。

5.5.2.2 Self-Testing Using MISR and Parallel SRSG

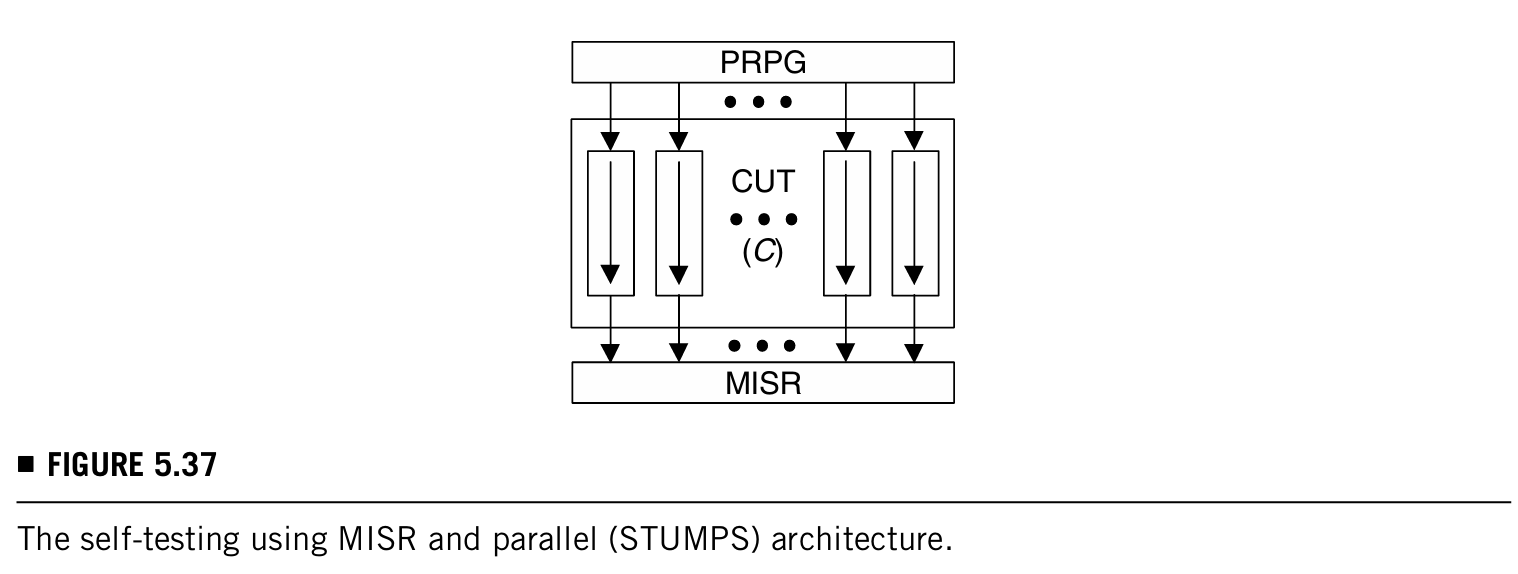

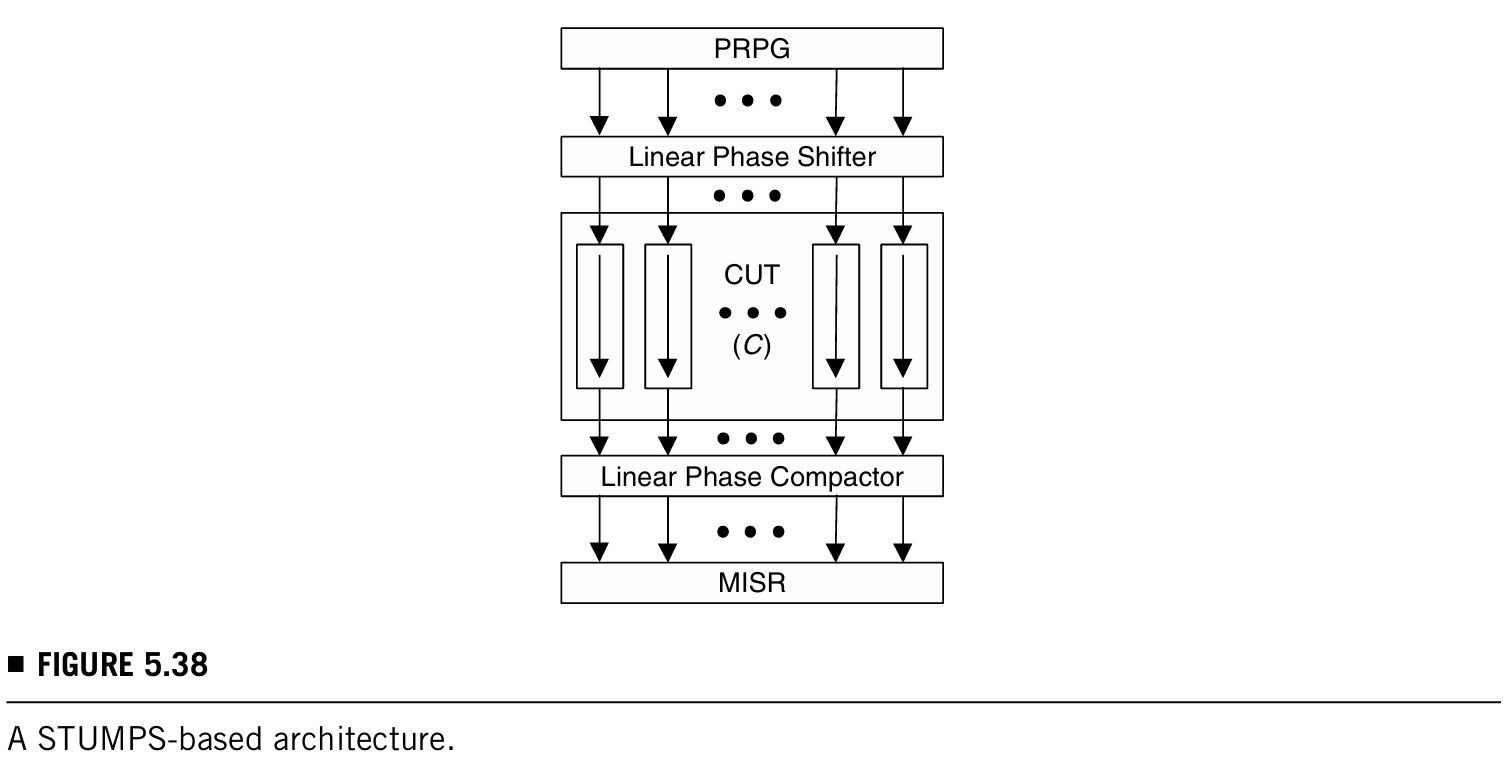

还有和上面相似的一个架构如下图,这个架构叫做self-testing using MISR and parallel SRSG (STUMPS):

这个架构知道现在都在工业领域被广泛应用。

这个架构还可以被继续优化,加入an optional linear phase shifter和an optional linear phase compactor,也是在工业界被广泛应用到的,可以降低PRPG和MISR的长度并且增加PRPG的随机性。见下图架构:

5.5.3 BIST Architectures Using Register Reconfiguration

BIST的设计还要考虑的一个因素就是测试时间,利用设计中已有的存储单元做test generation和response analysis的技术就可以减少测试时间,这些存储单元为了测试的目的被重新设计同时满足上面两种需求,这种BIST架构通常被称为test-per-clock BIST system。

5.5.3.1 Built-In Logic Block Observer

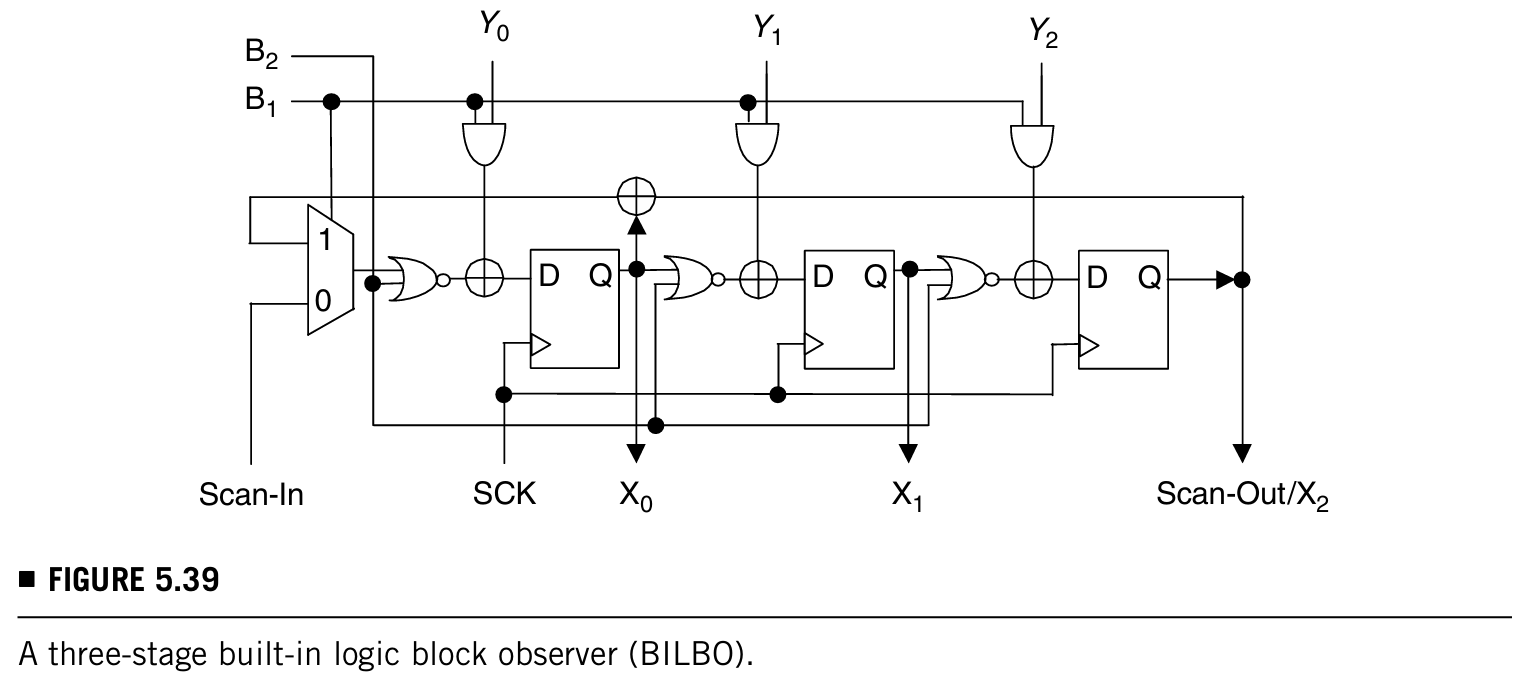

这个架构中,电路被分割成几个独立的部分(logic blocks),每个模块有它自己的输入和输出寄存器registers (storage elements),这个寄存器被重新设计为PRPGs或者MISRs,这个被重新设计的寄存器就叫做built-in logic block observer (BILBO)。

BILBO可以操作在四种不同的模式:

- normal mode

- scan mode

- test generation or signature analysis mode

- reset mode

一个典型的three-stage BILBO在自测试中被重构为TPG或者MISR的图示如下:

四种模式的操作分别具体为:

- normal mode:B1和B2都是1的时候,Yi的值直接进入D flip-flops

- scan mode:B1和B2都是0的时候,BILBO是一个移位寄存器,数据从scan-in进入,从scan-out出去

- test generation or signature analysis mode:B1是1和B2是0的时候,BILBO是一个MISR,也可以在这个配置下让所有的Yi都是1使它成为一个TPG

- reset mode:B1是0和B2是1的时候,时钟触发后电路复位

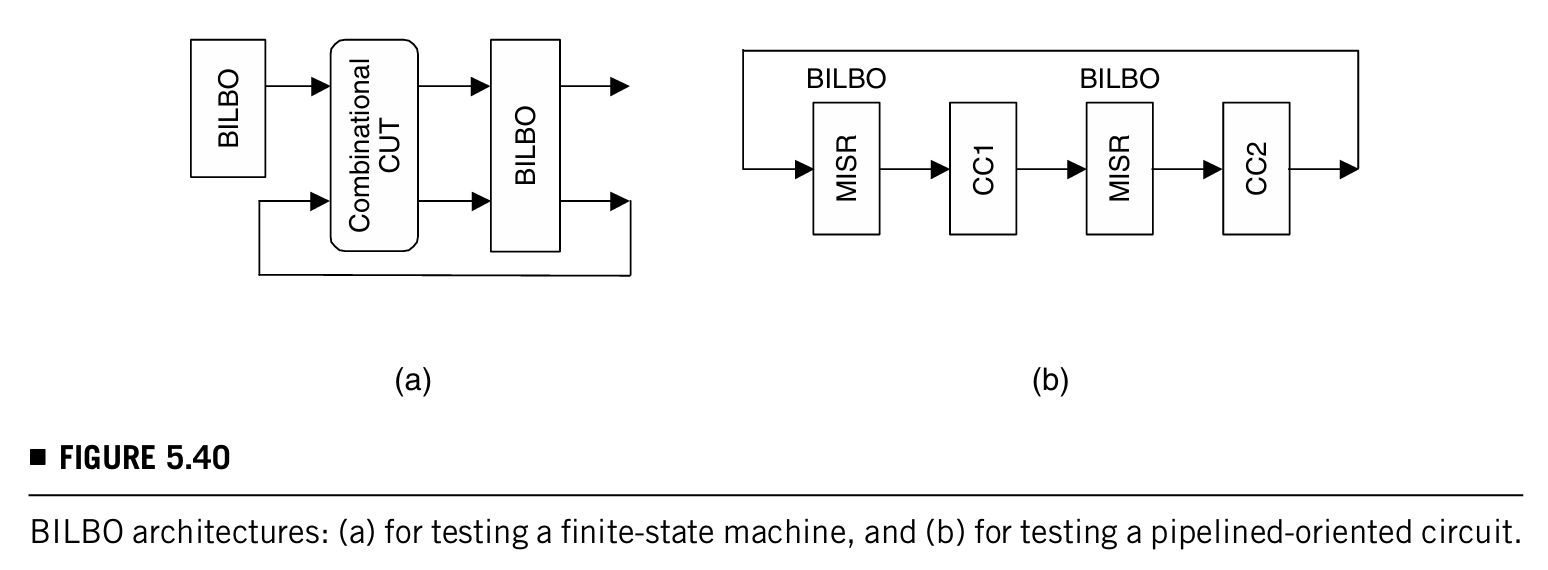

这项技术非常适用于某些电路比如RAMs, ROMs, or bus-oriented circuits,这里每一个划分开的模块的输入和输出都可以被独立地重新配置,

下图是测试finite-state machines和pipelined-oriented circuits的图示:

前一模块的signature data必须作为下一模块的test patterns,因为test generation和signature analysis modes两种模式是不能分开的,这种情况下,需要一个具体的故障仿真来达到100%的single-stuck fault coverage。