Nios II 实现流水灯实验

- 一.硬件设计

- 1.新建Quartus项目

-

- [2. 设计Nios ii](#2. 设计Nios ii)

- 二.软件设计

前言

实验目标:

学习 Quartus 、Platform Designer、Nios-II SBT 的基本操作;初步了解 SOPC 的开发流程,基本掌握 Nios-II 软核的定制方法;掌握 Nios-II 软件的开发流程,软件的基本调试方法。

主要内容:

在DE2-115开发板上用Nios软件编程方式完成LED流水灯显示

用Nios软件编程通过DE2-115开发板串口输出"Hello Nios-II"字符到笔记本电脑串口助手

实验原理:

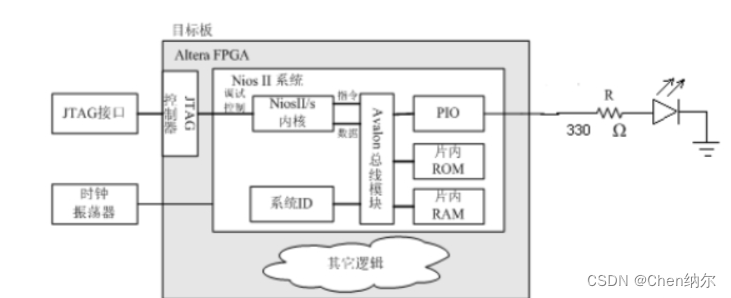

控制 LED 灯闪烁的用户程序代码很小,可将其固化在片内 ROM 来执行。变量、堆栈等空间使用片内 RAM,不使用任何片外存储器。整个系统的框图如下图所示。

从图 1.1 控制 LED 闪烁的系统框图可知,其它逻辑与 Nios II 系统一样可存在于 FPGA中。Nios II 系统可与其它片内逻辑相互作用,取决于整个系统的需要。为了简单起见,本实验在 FPGA 内不包括其它逻辑。

一.硬件设计

1.新建Quartus项目

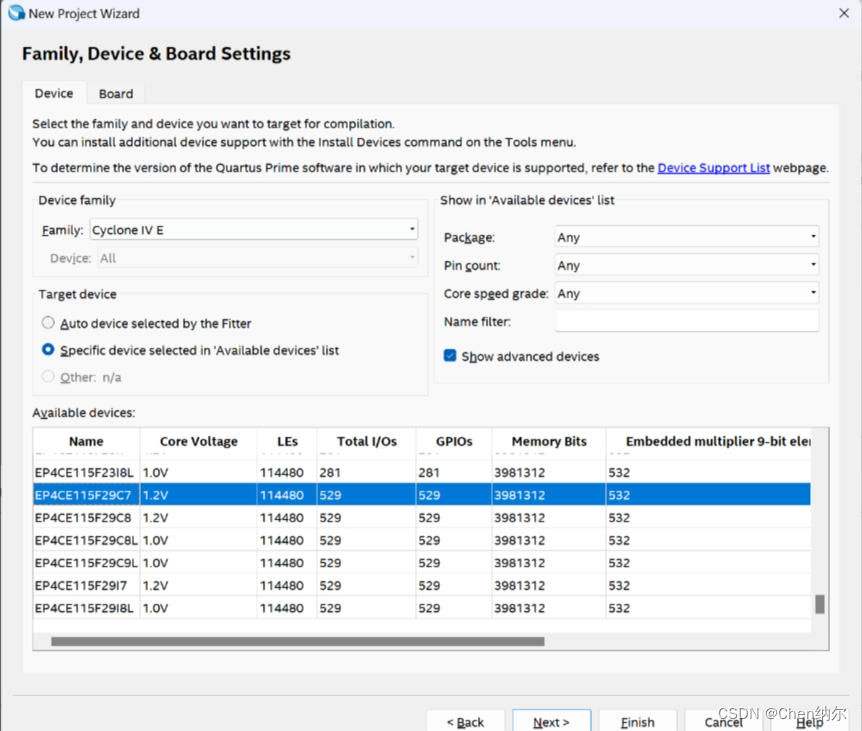

这里我选择的芯片类型为EP4CE115F29C7,你也可以根据自己需要,选择其他芯片

2. 设计Nios ii

- 设计时钟

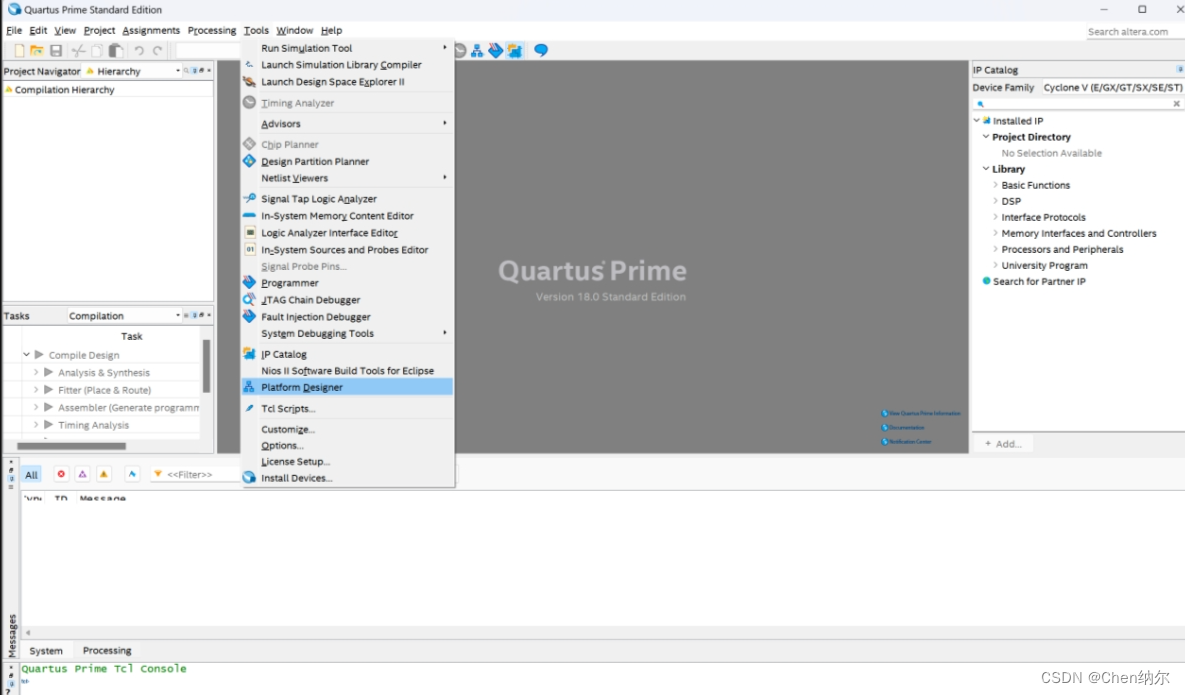

点击Tools 进入Platform Designer

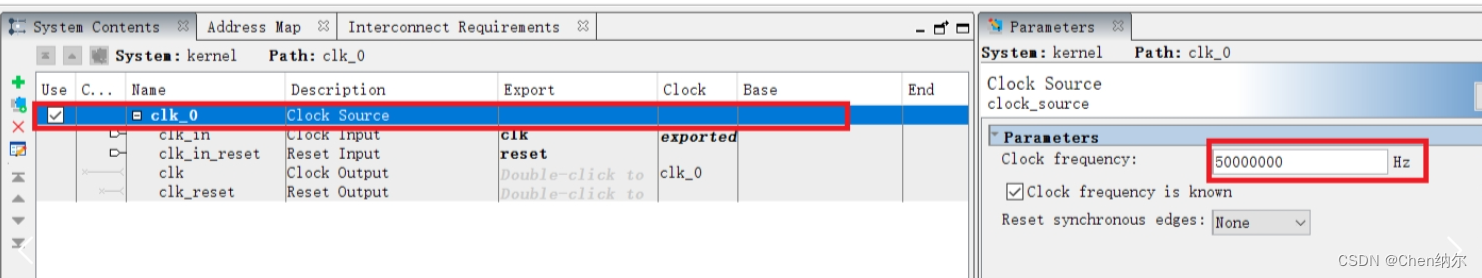

鼠标放在 clk_0 处点击右键 Edit 或是双击 clk_0 元件,对 Clock 进行时钟设置,设为 50M

- 添加部件

添加 CPU 和外围器件。从 PD 的元件池中选择以下元件加入到当前设计的系统中:Nios II 32-bit CPU、jtag uart、片上存储器、PIO、system ID。

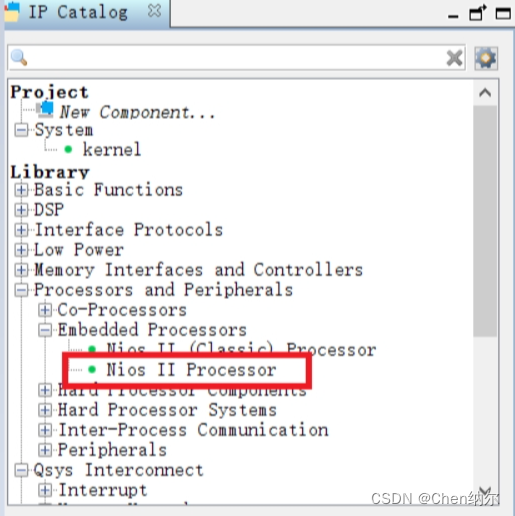

① 添加 Nios II 32-bit CPU

a. 在"component library"标签栏中找到"Nios II Processor"后点击 Add(在查找窗口输出 nios 即可)

② 添加 jtag uart 接口。jtag uart 接口是 Nios II 嵌入式处理器新添加的接口元件,通过内嵌在 Intel FPGA 内部的 JTAG 电路,可以实现在 PC 主机与 Qsys 系统之间进行串行字符流通信。

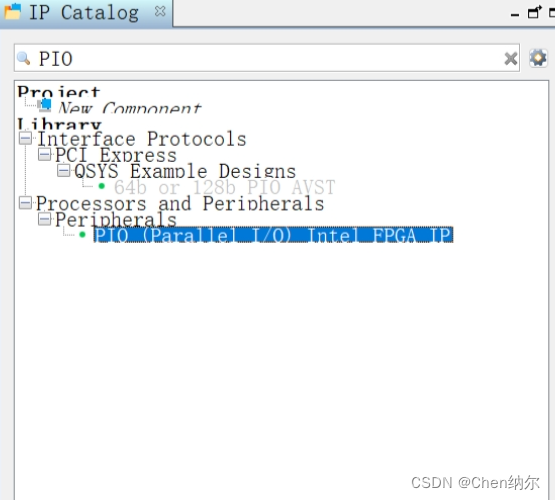

③添加 PIO 接口

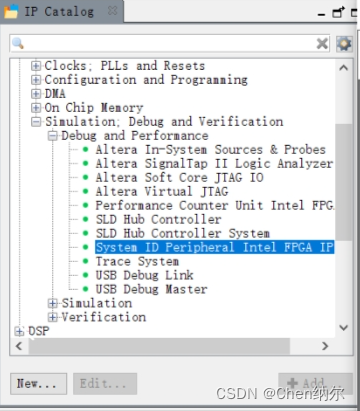

⑤ 添加片 System ID Peripheral 核

a. 从下图左侧"Component Library"标签栏中的查找窗口输入 sys 找到" System ID Peripheral"后点击 Add。

b. 保持默认选项,单击 Finish。如下图所示:

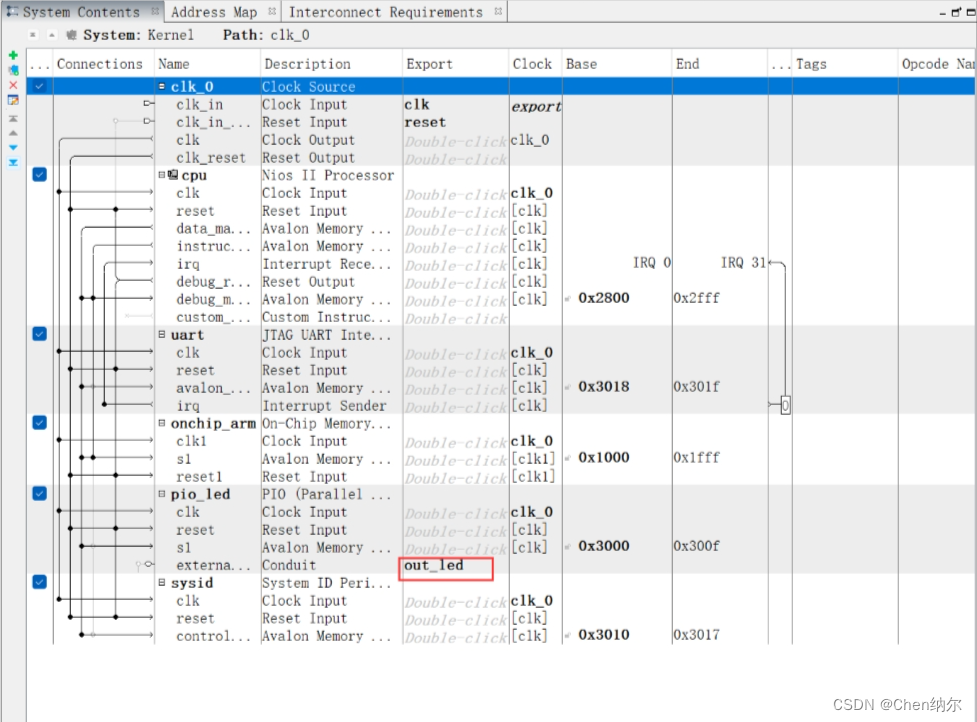

依照下图进行连线

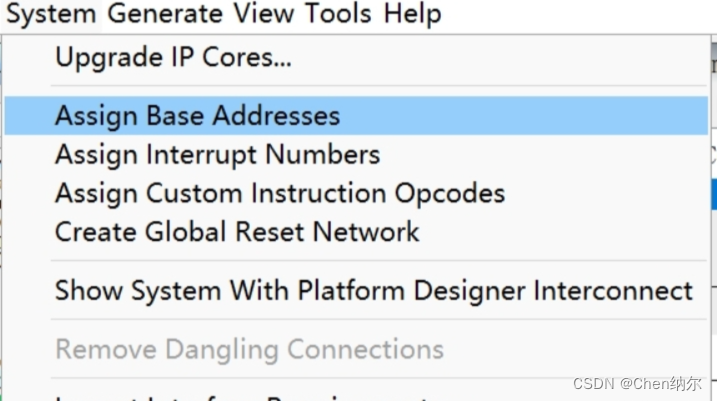

分配基址

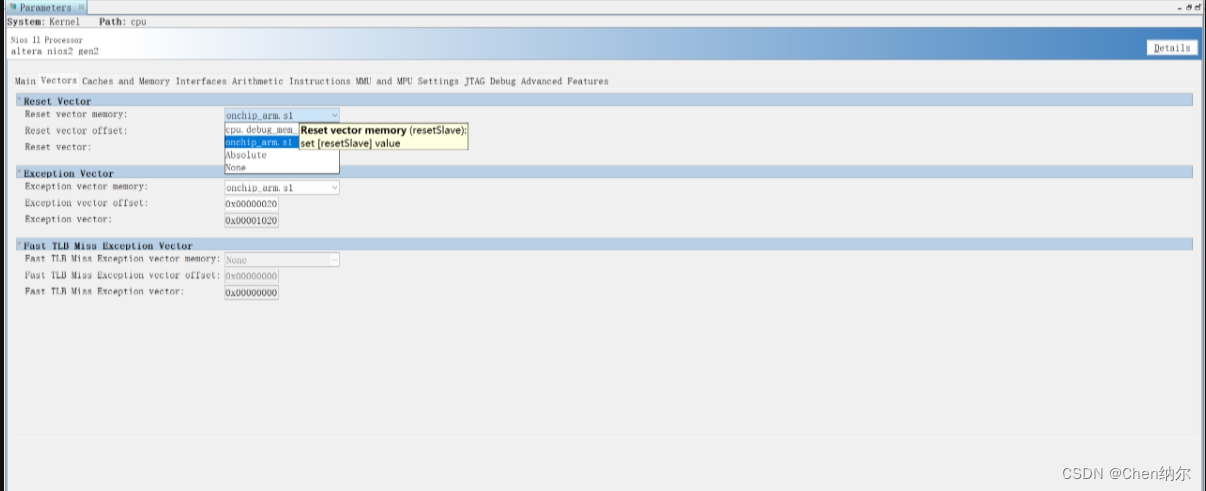

双击CPU进入以下界面更改重置容器

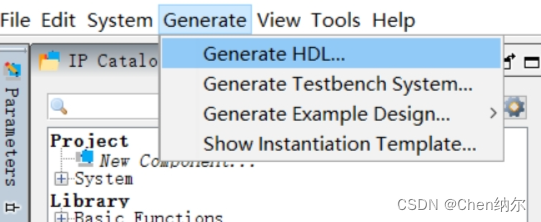

生成 Qsys 系统:点选"Generation HDL"标签栏中 Generate 按钮生成 Qsys 系统。

硬件设计完成

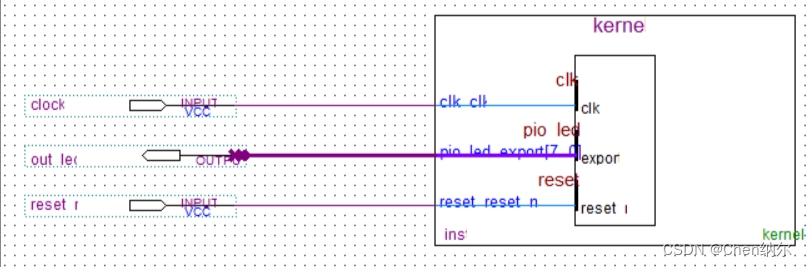

进行逻辑连接和生成管脚

(1)逻辑连接。开发板晶振为 50M,与系统默认一致,因此,这里我们不需要修改。

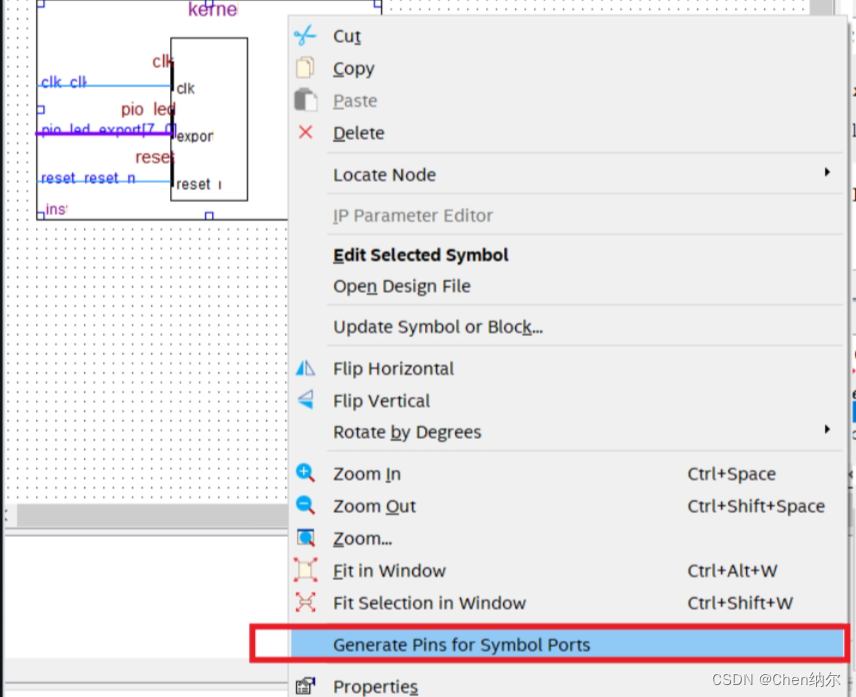

(2)点击鼠标右键选取 Generate Pin for Symbol Ports 生成管脚。如下图所示

将管脚"inclk0"改名为 clock,管脚"reset_reset_n"改名为 reset_n,管脚 out_led_export[7...0]改为 out_led[7...0]。如下图所示

二.软件设计

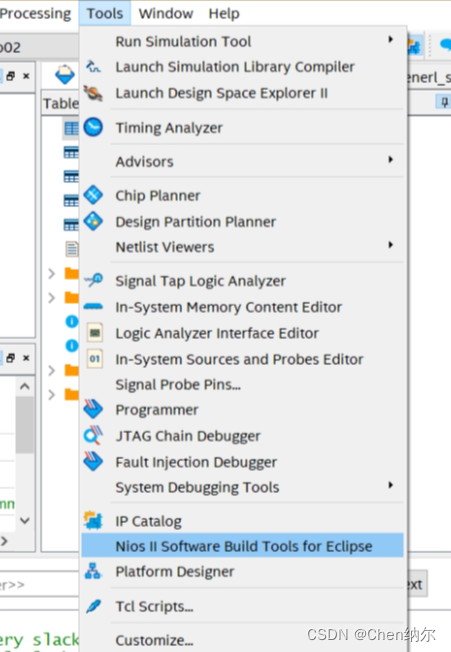

进入eclipse

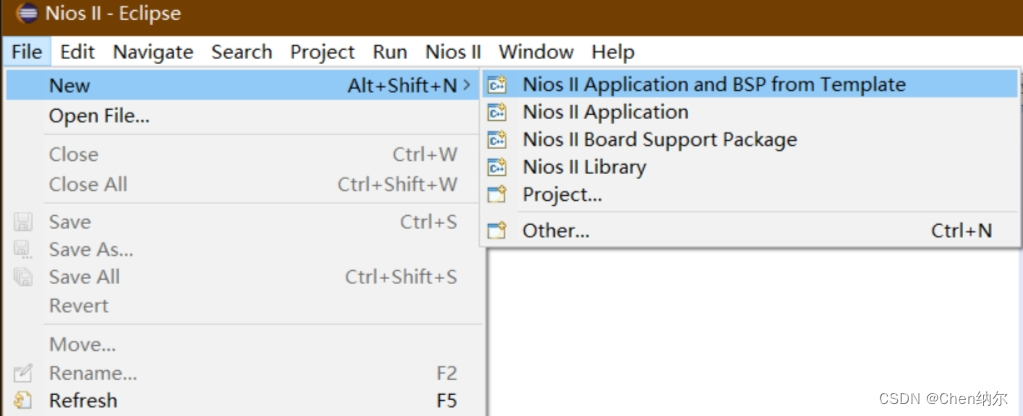

新建项目

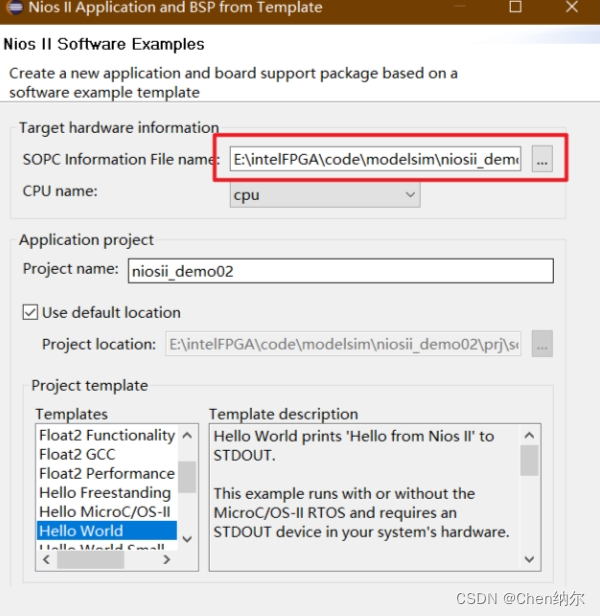

选择导入sopcinfo文件,Hello world 模板

将hello world 代码替换成以下代码

c

#include "system.h"

#include "altera_avalon_pio_regs.h"

#include "alt_types.h"

#include "stdio.h"

const alt_u8

led_data[8]={0x01,0x02,0x04,0x08,0x10,0x20,0x40,0x80};

int main (void)

{

int count=0;

alt_u8 led;

volatile int i;

while (1)

{ if (count==7)

{count=0;}

else

{count++;}

led=led_data[count];

IOWR_ALTERA_AVALON_PIO_DATA(PIO_LED_BASE, led);

i = 0;

printf("Hello Nios-II\n");

while (i<500000)

i++;

}

return 0;

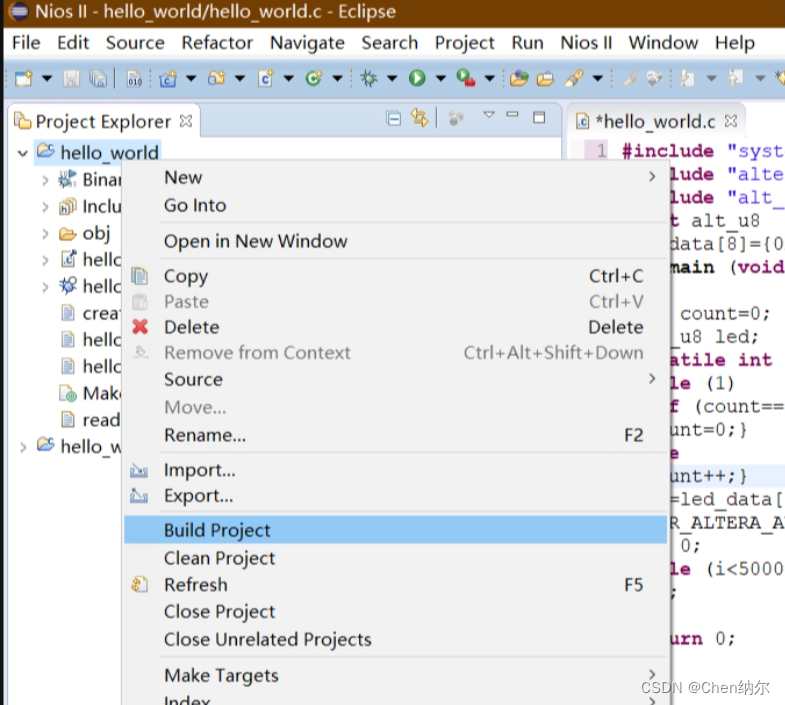

}右键项目文件夹,点击Build Project

编译完成后,连接好开发板,点击Run As Nios II Hardware,即可看到流水灯现象。

效果展示