本博文主要交流设计思路,在本博客已给出相关博文约180篇,希望对初学者有用。 注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。

前面分享如何进行仿真,下面介绍硬件平台上验证其功能及性能。

RoCE v2 高速数据传输系统基于Xilinx integrated 100G Ethernet Subsystem 进行搭建,其常用版本为 UltraScale+ CMAC集成块,考虑低成本方案,这里使用基于 XCZU47DR FPGA 的开发板进行硬件平台搭建及测试。远程主机端则使用 迈洛斯(现英伟达) CX455-A 网卡,其支持 100Gbps IB/ETH 网络数据传输。

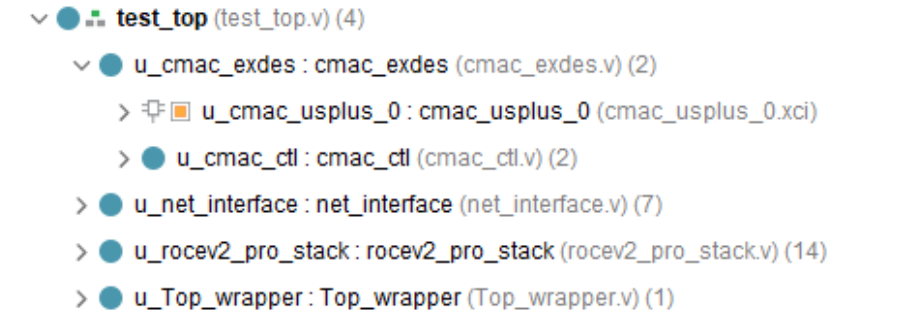

工程共分为 HDL 工程和 Block Design 工程两部分。HDL 工程如图 1 所示,由于 CMAC 集成块外部接口较为繁杂,

出于精简接口的考虑,并没有将 RoCE v2 高速数据传输系统打包为 IP 后再与 CMAC集成块进行连接,而是直接将 CMAC 包含进 HDL 工程内。 HDL 工程从上至下依次为: CMAC 集成块封装、以太网协议栈、融合以太网协议栈及 Block Design 工程。

图1 测试环境硬件平台 HDL 工程图

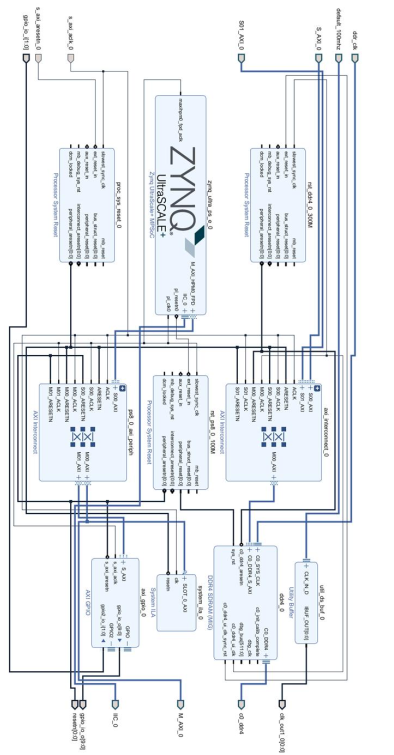

基于 XCZU47DR FPGA 的 Block Design 工程如图 2 所示, Block Design 中包含了 CPU 模块、 DDR 接口模块和外设控制模块。其中 CPU 模块包含 Xilinx ZYNQ 硬核及一些外置的时钟控制和复位模块; DDR 接口模块中使用 MIG 控制器将 DDR 地

址及数据接口转换为 AXI4 总线形式;外设控制模块则负责控制 QSFP 接口信号及板上 PLL 时钟源。 System_ila 负责抓取总线波形,方便测试过程中的观察及调试。

图2 测试环境硬件平台 Block Design 图

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望