作者:Hello,Panda

大家晚上好,很久没有分享设计案例了,实在是太忙了,精力十分有限,今天分享一个CrosslinkNX系列器件用作USB3.0相机的案例。其实就是分享一下使用CrosslinkNX器件设计USB3.0相机主要有两种方案:

(1)传统方案:使用LCFCL通用器件(LIFCL-40或LIFCL-17)+USB桥接芯片(如5Gbps USB桥芯片Cyusb3014,10Gbps USB桥芯片CYUSB4013等);

(2)新方案:使用LIFCL-33U实现小封装低功耗USB3.2 5Gbps USB通信。

方案一:使用LIFCL通用器件+USB桥接芯片

LIFCL-40 FPGA有两组2.5Gbps 4-Lane MIPI硬核,也可接入多Lane的LVDS、SubLVDS、SLVS接口的Sensor,经过简单的流水线处理,比如彩色相机的ISP,黑白相机的非均匀性校正、降噪等处理后经USB桥接芯片送到PC机显示和保存和进一步二次开发。因此,就存在两种情况:

(1)接入Sensor的数据量比输出USB3.0有效数据带宽大很多,这种情况就需要添加DDR缓存(必须是LIFCL-40 BGA256及以上封装才支持DDR3-1066 16bit)来进行丢帧处理来适配带宽,这种情况只能使用LIFCL-40 FPGA芯片。

(2)带宽小于USB3.0有效数据带宽,这种情况只需要使用内部的Large RAM缓存数行来缓冲PC端读取USB3.0接口不稳定带来的些许数据阻塞即可,这种情况可以使用LIFCL-40或LIFCL-17,且LIFCL-17因有更大的内部Large RAM而更佳。这两种情况的,实现这两种情况的结构见下图1所示。

图1 使用LIFCL通用器件+USB桥接芯片方案图

该案例实现Lattice官方有评估板,USB桥接芯片使用CYUSB3014 8-bit总线模式,外挂RAM缓存芯片采用2片8bit HyperRAM芯片,板载配备的CMOS图像sensor为IMX224。

方案二:LIFCL-33U器件

这是Lattice新推出的器件,具有33K的逻辑资源和USB3.2/5Gbps物理层,实际上就是把原来MIPI硬核的资源用到USB上来了,阉割掉了MIPI硬核。因此,接入MIPI接口的Sensor时只能用到最高1.25Gbps的Lane速率,接入LVDS、SubLVDS、SLVS接口的Sensor时最高1.2Gbps,均要求在硬件信号完整性设计得极为理想的情况。该器件84 WLCSP(3.1×7.4mm)和104fcCSP(5.5×8.5mm)两种封装,第一种封装可用IO仅44个,可用作差分对输入的只有13对,104引脚封装的52个IO,稍富余一些。

根据Lattice提供的USB23 IPCore的资源利用情况,Registers使用了5064,LUTs使用了7392,EBRs使用了26个(共64个),因此还有一定的资源剩余来做一些Pipeline的计算,但也仅此而已。根据资源的情况来看,使用LIFCL-33U器件一般限制到了1080P的图像或其他的数据采集业务(如LVDS接口的ADC数据采集)。但是,它们有及其优秀的功耗和面积,特别适合在有低功耗和小体积硬性要求的设备上使用。

下图2是USB23 IP的应用框图,它例化实现了一个USB3.0物理层、Endpoint逻辑和一个RISC-V的CPU软核。

图2 LIFCL-33U实现USB3.0框图

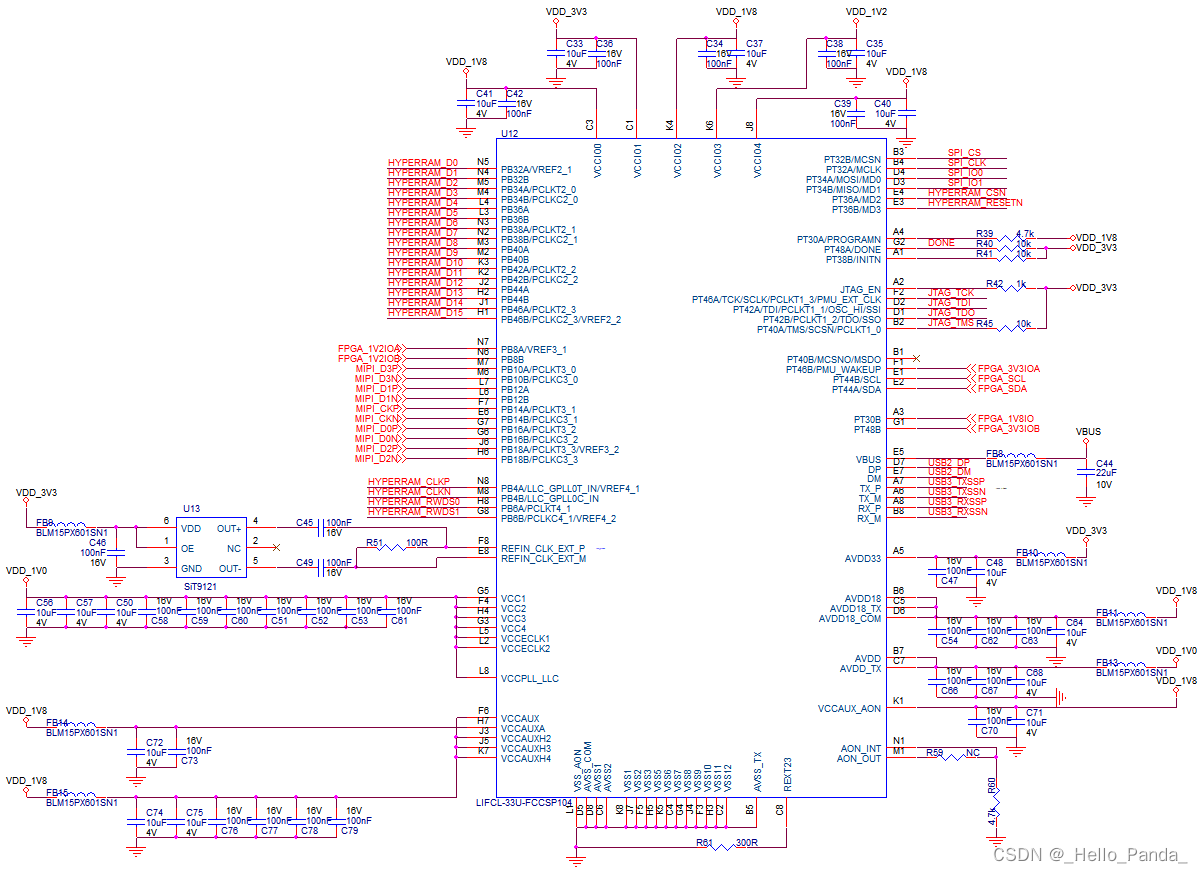

熊猫君也自制硬件对此方案进行了尝试,下图3是熊猫君LIFCL-33U USB Camera的硬件原理图。

图3 LIFCL-33U的硬件原理图

好了,夜深了。各位技术大神们早点安歇。下次分享再见,希望能给大家的研发工作带来帮助。