文章目录

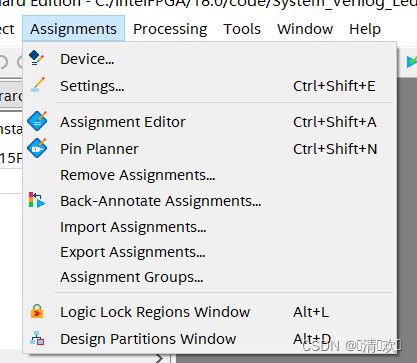

一新建一个工程

1打开quartus建立一个项目

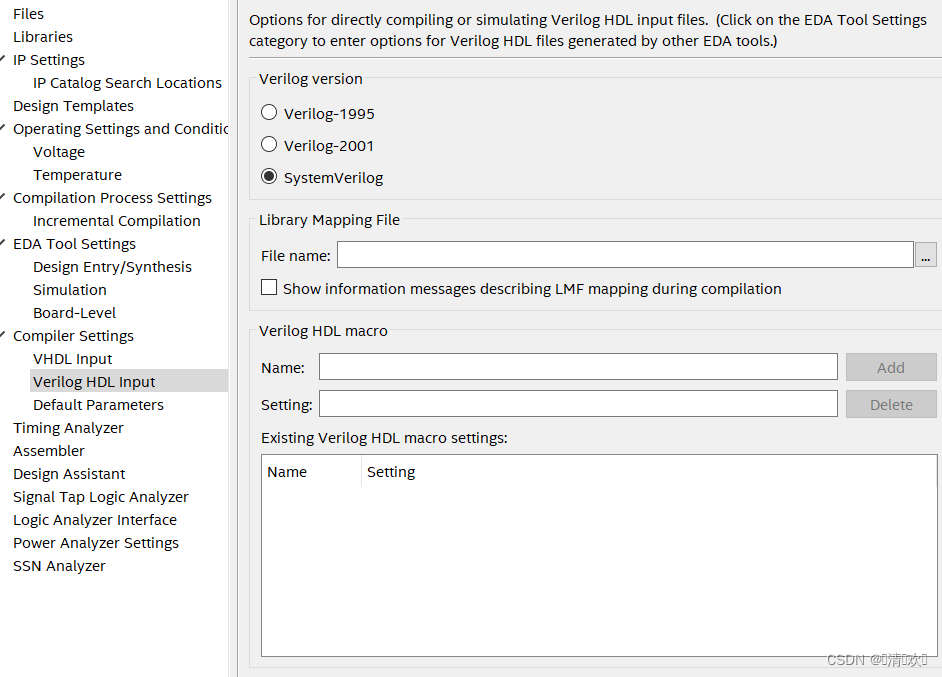

注意打开settings在里面的Verilog HDL input选择System Verilog

二代码

1流水灯代码

c

module led (

input clk, // 时钟信号

input rst_n, // 复位信号

output reg [7:0] led // 输出信号

);

reg [3:0] cnt; // 计数器

// 时钟计数

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin // 复位信号为低电平时清零计数器

cnt <= 4'b0000;

end else begin

cnt <= cnt + 1; // 每个时钟周期计数器加一

end

end

// 流水灯输出

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin // 复位信号为低电平时清零输出

led <= 8'b00000001;

end else begin

case (cnt)

4'b0000: led <= 8'b00000001; // 第一位亮

4'b0001: led <= 8'b00000010; // 第二位亮

4'b0010: led <= 8'b00000100; // 第三位亮

4'b0011: led <= 8'b00001000; // 第四位亮

4'b0100: led <= 8'b00010000; // 第五位亮

4'b0101: led <= 8'b00100000; // 第六位亮

4'b0110: led <= 8'b01000000; // 第七位亮

4'b0111: led <= 8'b10000000; // 第八位亮

default: led <= 8'b00000001; // 默认第一位亮

endcase

end

end

endmoduleTestbench

c

module tb_led;

logic clk;

logic rst;

logic [7:0] leds;

led_chaser uut (

.clk(clk),

.rst(rst),

.leds(leds)

);

initial begin

clk = 0;

forever #5 clk = ~clk;

end

initial begin

rst = 1;

#10;

rst = 0;

#100;

$stop;

end

endmodule三效果

1效果图