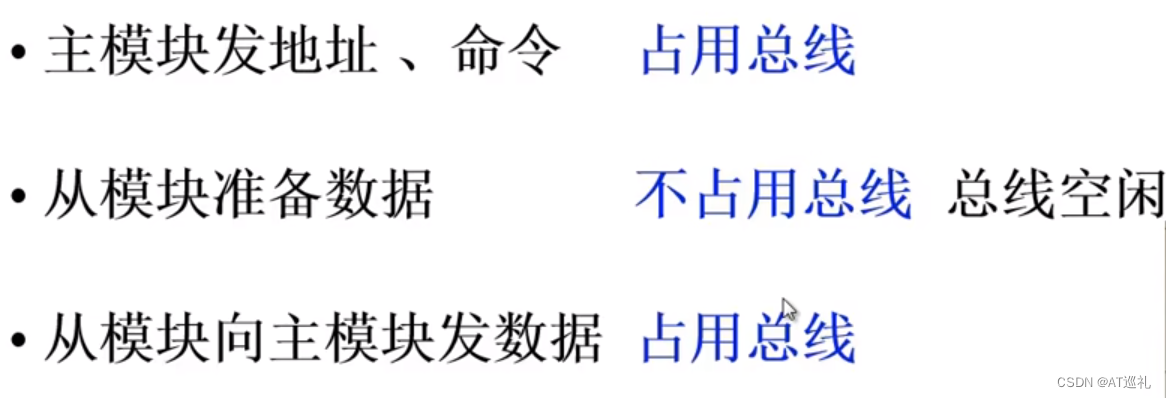

一、链式查询方式

接口的优先级固定不变

在链式查询的情况下,设备的优先级通常与其在链中的位置有关。具体来说,越靠近查询链的起始位置的设备通常具有较高的优先级,而越靠近链的末尾位置的设备优先级较低。

优点:

- 简单实现:链式查询可以通过简单的硬件逻辑或软件控制实现,无需复杂的总线仲裁机制。

- 低成本:相比于其他总线访问方式,链式查询的硬件成本较低,适用于成本敏感型应用。

- 适用于少量设备:对于少量设备的系统,链式查询是一种有效的管理方式,可以简化系统设计和管理。

缺点:

-

响应时间不稳定:由于设备的查询顺序是固定的,靠近链起始位置的设备响应时间较短,而靠近链末尾位置的设备响应时间较长,导致整体响应时间不稳定。

-

单点故障影响大:如果链中的某个设备发生故障,可能会影响整个链式查询系统的正常工作。

-

不适用于大规模系统:对于大规模设备的系统,链式查询可能会导致查询时间过长,降低系统性能。

适用场景:

- 小型系统:链式查询适用于设备数量较少的小型系统,例如家庭电器控制系统、嵌入式系统等。

- 低成本应用:由于链式查询的硬件成本低,适用于成本敏感型应用,例如消费类电子产品、嵌入式控制器等。

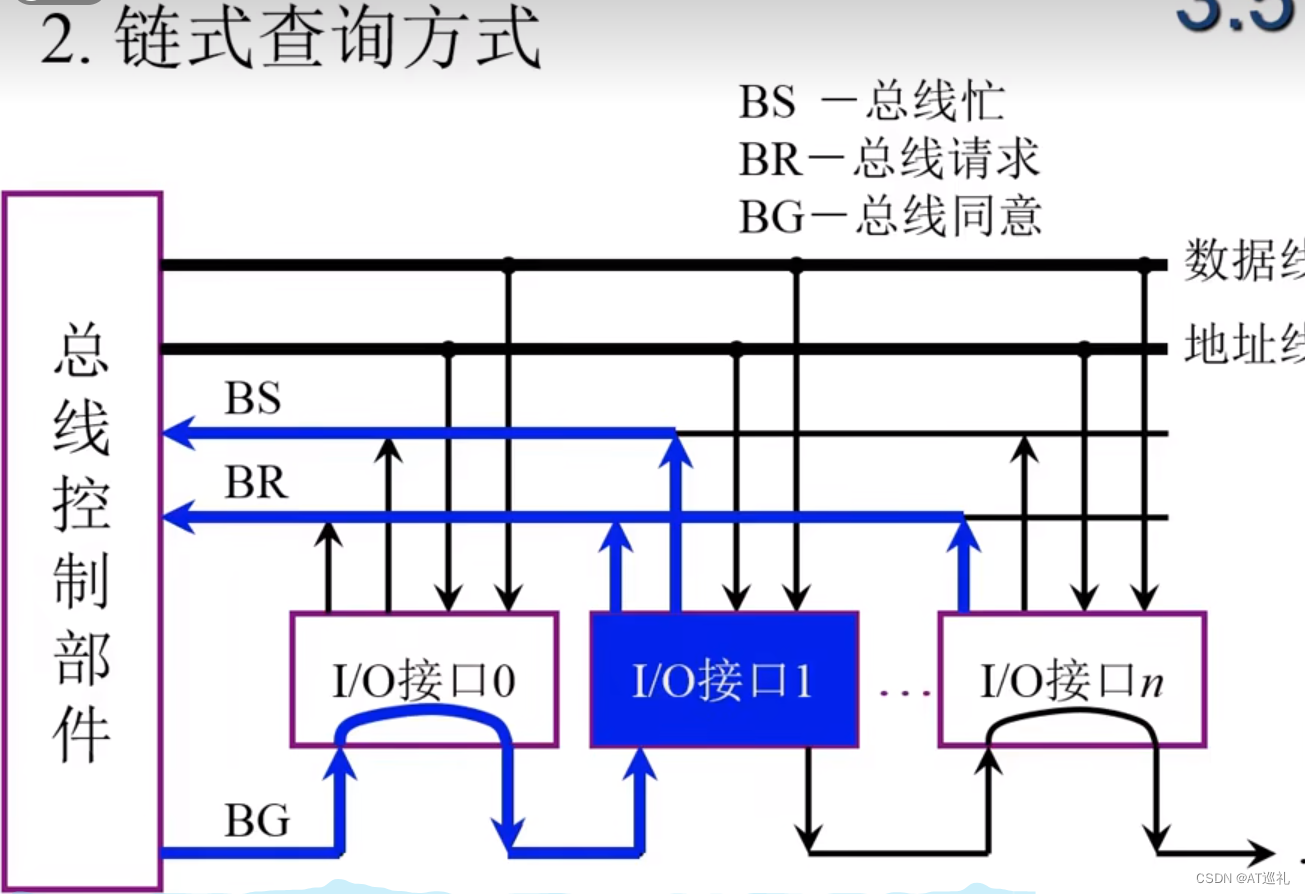

二、计数器定时查询方式

可以通过软件修改计数器的初始值,改变调用接口的优先级

地址线:

通过地址线,CPU可以确定要访问的内存或 I/O 设备的地址范围。例如,如果一个系统有 16 条地址线,那么它可以访问的地址范围为 2^16,即 0 到 65535。地址线不直接指向特定的设备,而是用于选择地址范围。

设备地址:

设备地址是特定的 I/O 设备在系统中的地址位置。这个地址通常是由设备的控制器或系统配置确定的,不同的设备有不同的地址。当 CPU 决定要访问某个 I/O 设备时,它会发送相应的地址信号,选择要与之通信的设备地址。

地址线用于选择要访问的地址范围,而设备地址用于选择具体的 I/O 设备。CPU可以通过地址线确定要访问的地址范围,然后通过发送设备地址来选择特定的 I/O 设备进行通信。

不过上面这两种都是按顺序进行查找的,这个速度依然慢

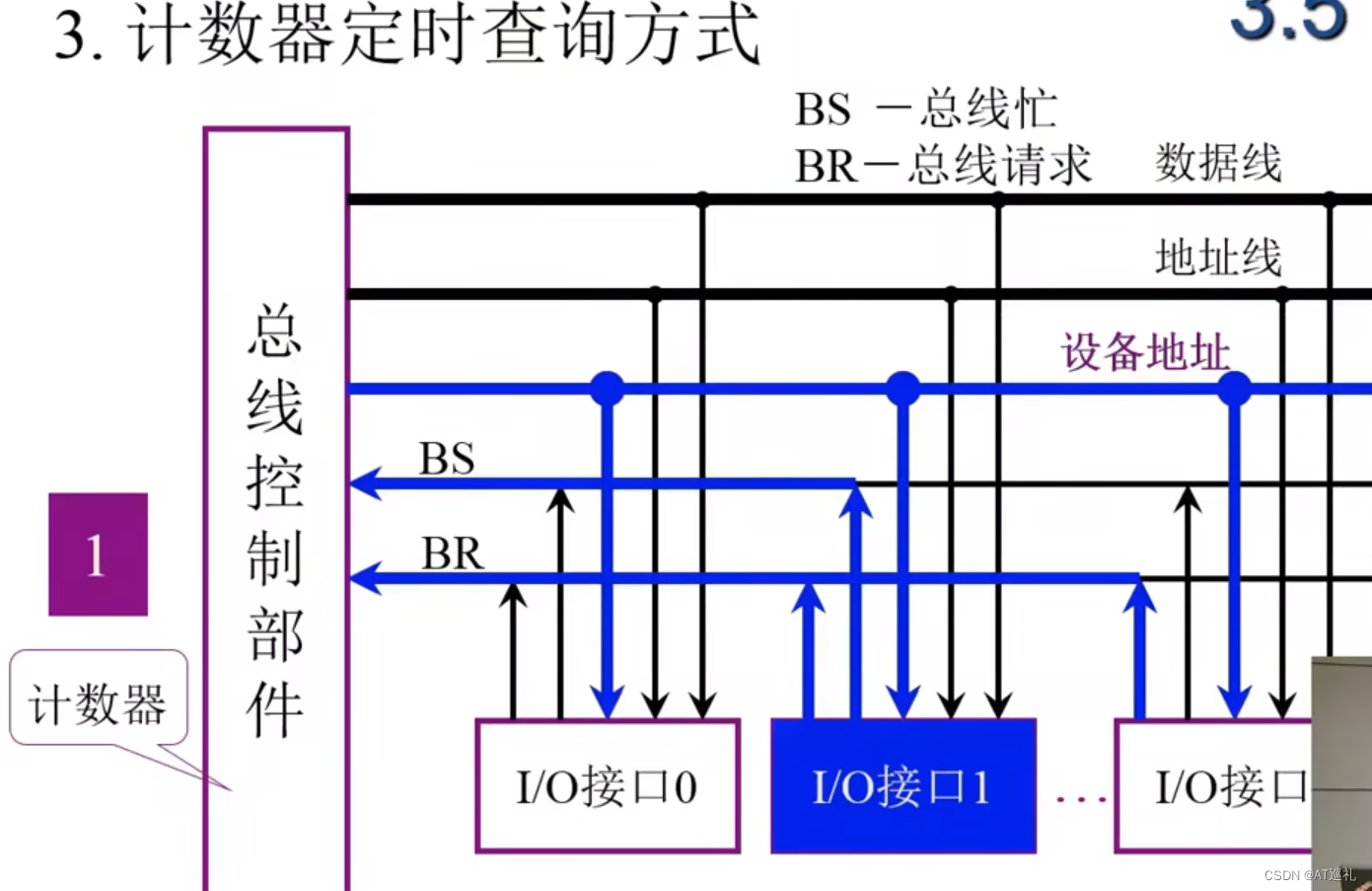

三、独立请求方式

可以通过修改排队器,改变调用接口的优先级

缺点:使用的线太多了

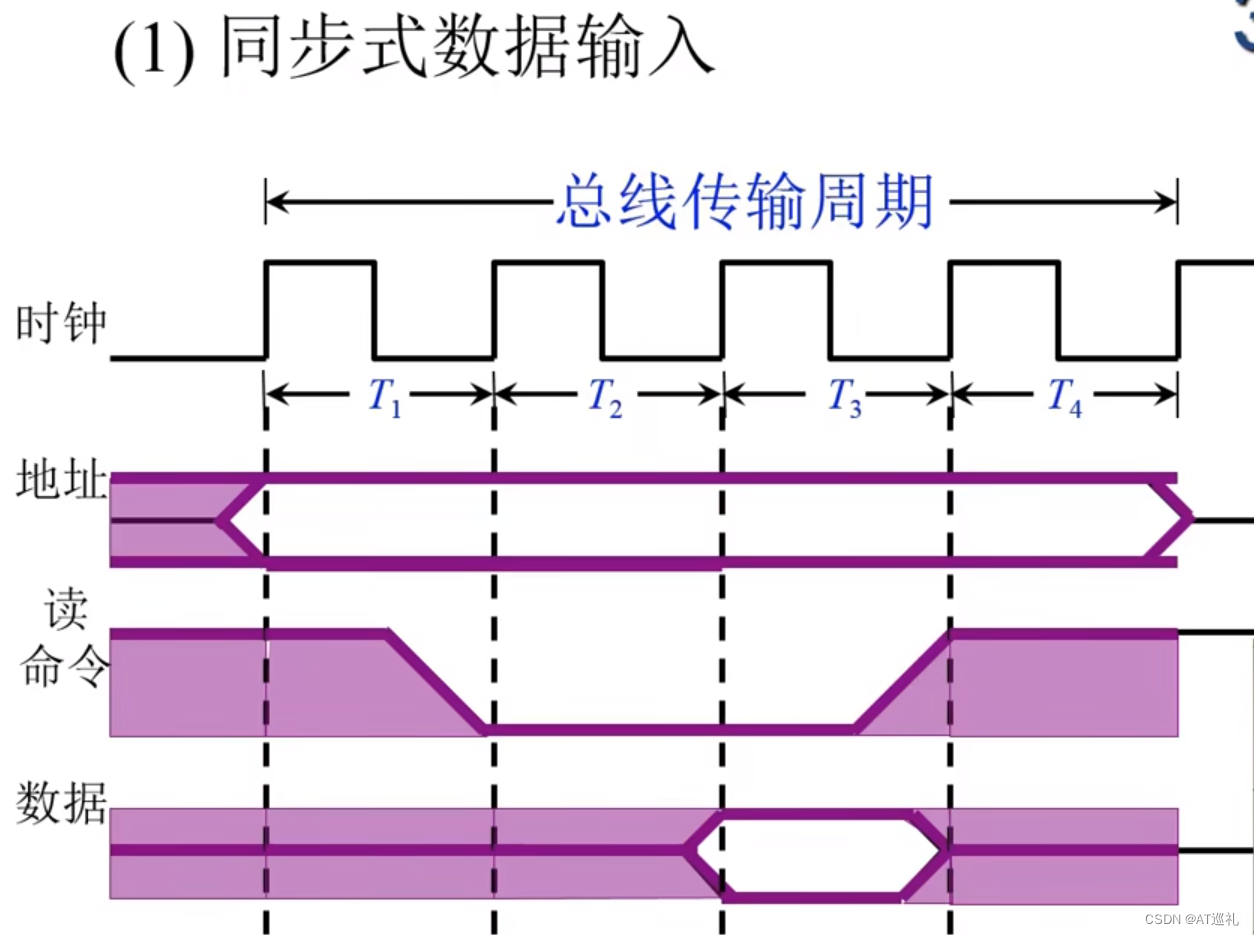

数据传输的每个阶段都严格按照定宽、定距的时钟信号进行同步,确保数据的采样和传输在预定的时刻进行。

固定的时刻进行固定的操作。

-

T1上升沿:

CPU给出地址信号,指定要访问的设备或内存位置。

-

T2上升沿:

在此期间,数据的读取准备工作在进行。CPU向外设发送读信号,指示其准备好接受数据。

-

T3上升沿:

外设将数据通过数据总线发送给CPU,CPU准备接收数据。

-

T4上升沿:

在T4上升沿时,CPU撤销控制(读)信号和数据信号,表示数据传输过程的结束。

-

T4结束时:

CPU撤销地址信号,表示数据输入过程的结束。

-

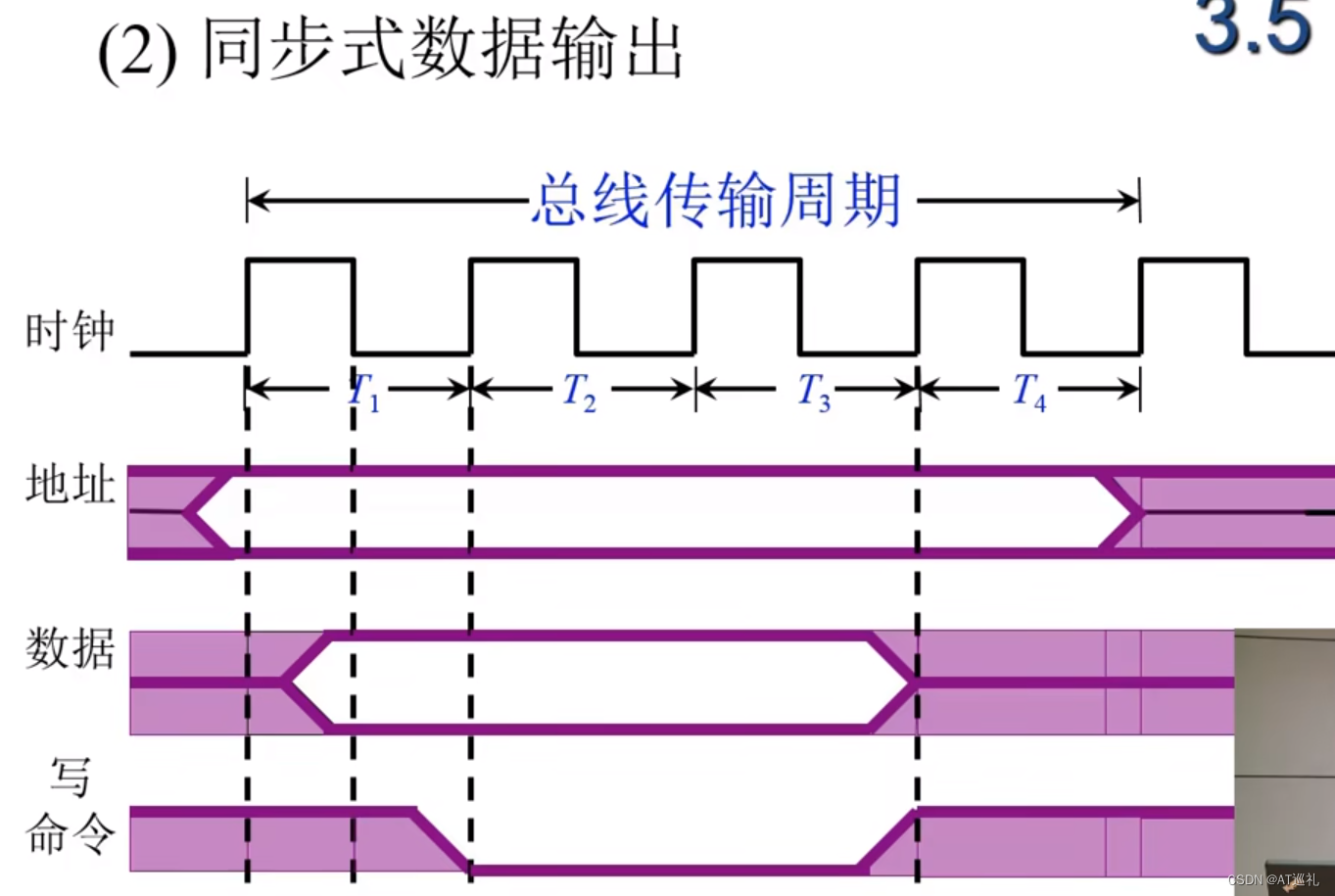

T1上升沿:

CPU给出地址信号,指定要从中读取数据的设备或内存位置。

-

T1下降沿:

外设在T1下降沿时,准备好数据并开始将数据发送到数据总线上。

-

T2上升沿:

CPU给出写命令,指示外设进行数据写入。

-

T2至T3上升沿之间:

外设进行写入操作,将数据写入到指定的设备或内存位置。

-

T4上升沿:

CPU撤销数据信号和写命令信号,表示数据写入过程的结束。

-

T4结束时:

CPU撤销地址信号,表示数据输出过程的结束。

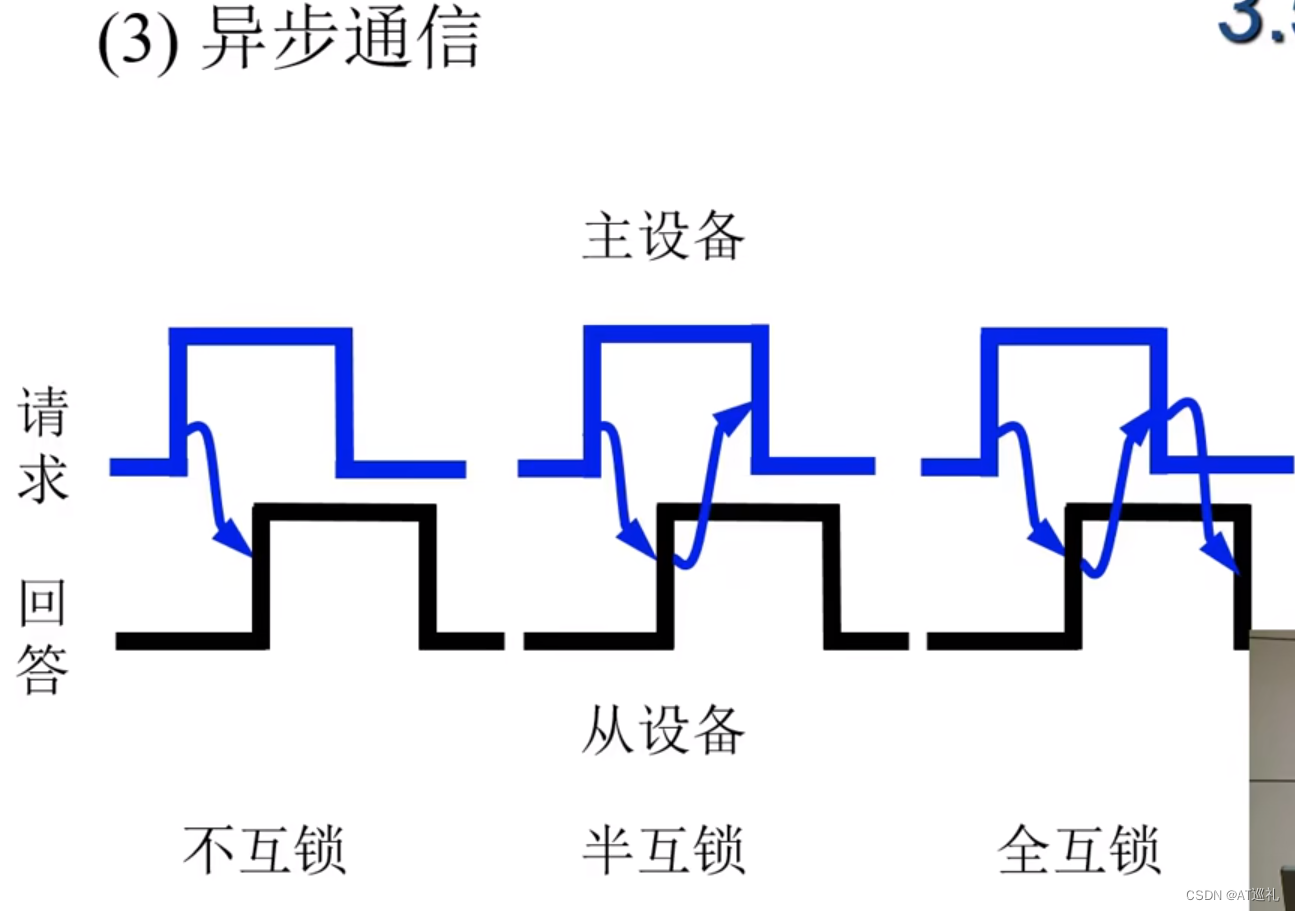

异步通信是一种数据传输方式,其中发送方和接收方的时钟信号不同步。在异步通信中,数据的传输不依赖于定时的时钟信号,而是通过特定的起始位和停止位来标识数据的开始和结束。

不互锁(Non-Handshaking):

在不互锁的异步通信中,发送方和接收方之间没有任何确认或应答信号。发送方发送数据后,不等待接收方的确认,而是直接继续发送下一个数据。

这种方式简单直接,但可能会存在数据丢失或传输错误的风险。

半互锁(Half-Duplex Handshaking):

在半互锁的异步通信中,发送方在发送数据后会等待接收方发送确认信号。一旦接收方接收到数据并进行处理,就会发送一个确认信号给发送方。

这种方式可以确保数据的可靠传输,但仍存在一定的风险,如接收方无法及时发送确认信号导致数据丢失。

全互锁(Full-Duplex Handshaking):

在全互锁的异步通信中,发送方和接收方之间进行完全的双向确认。发送方在发送数据后会等待接收方发送确认信号,同时接收方在接收到数据后会发送一个确认信号给发送方。

这种方式提供了最高级别的数据传输可靠性和稳定性,确保了数据的完整性和准确性。

-

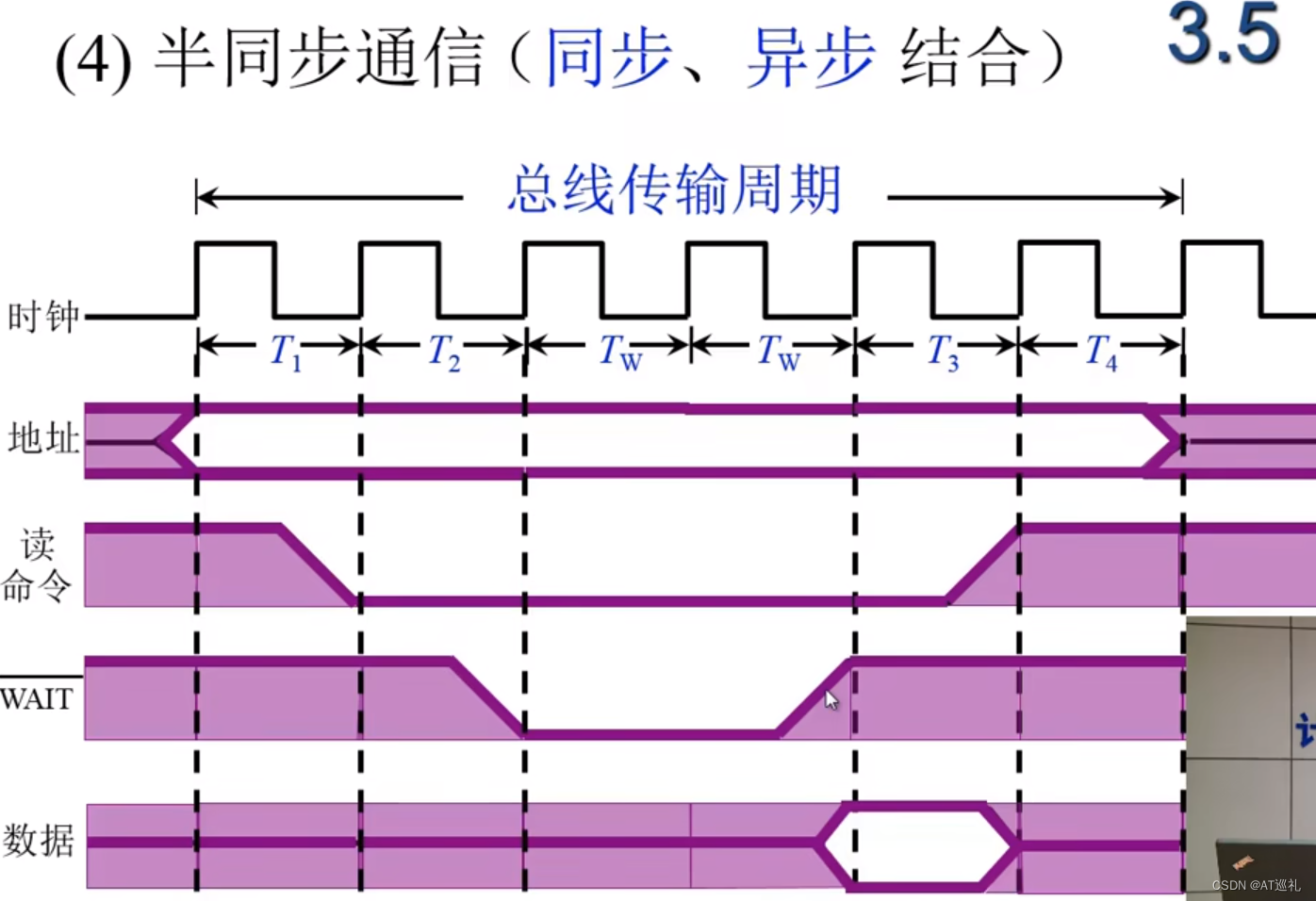

T1上升沿:

CPU给出地址信号,指定要访问的设备或内存位置。

-

T2上升沿:

CPU给出读信号

-

在T3开始之前:

从设备如果不能把数据准备好

通过wait信号给出一个低电平,告诉CPU进行等待

CPU检测wait信号是低电平,就会在T3到来之前,插入Tw

在下一个时钟周期开始之前,继续检测wait信号是否是高电平,否则重复上述操作

高电平则是,数据已经在数据总线上了,CPU可以进行数据接收

-

T3周期:

CPU开始接收数据

-

T4周期开始时:

CPU撤销读命令信号和数据信号,表示数据传输过程的结束

-

T4周期结束时:

CPU撤销地址信号,表示数据输入过程的结束。

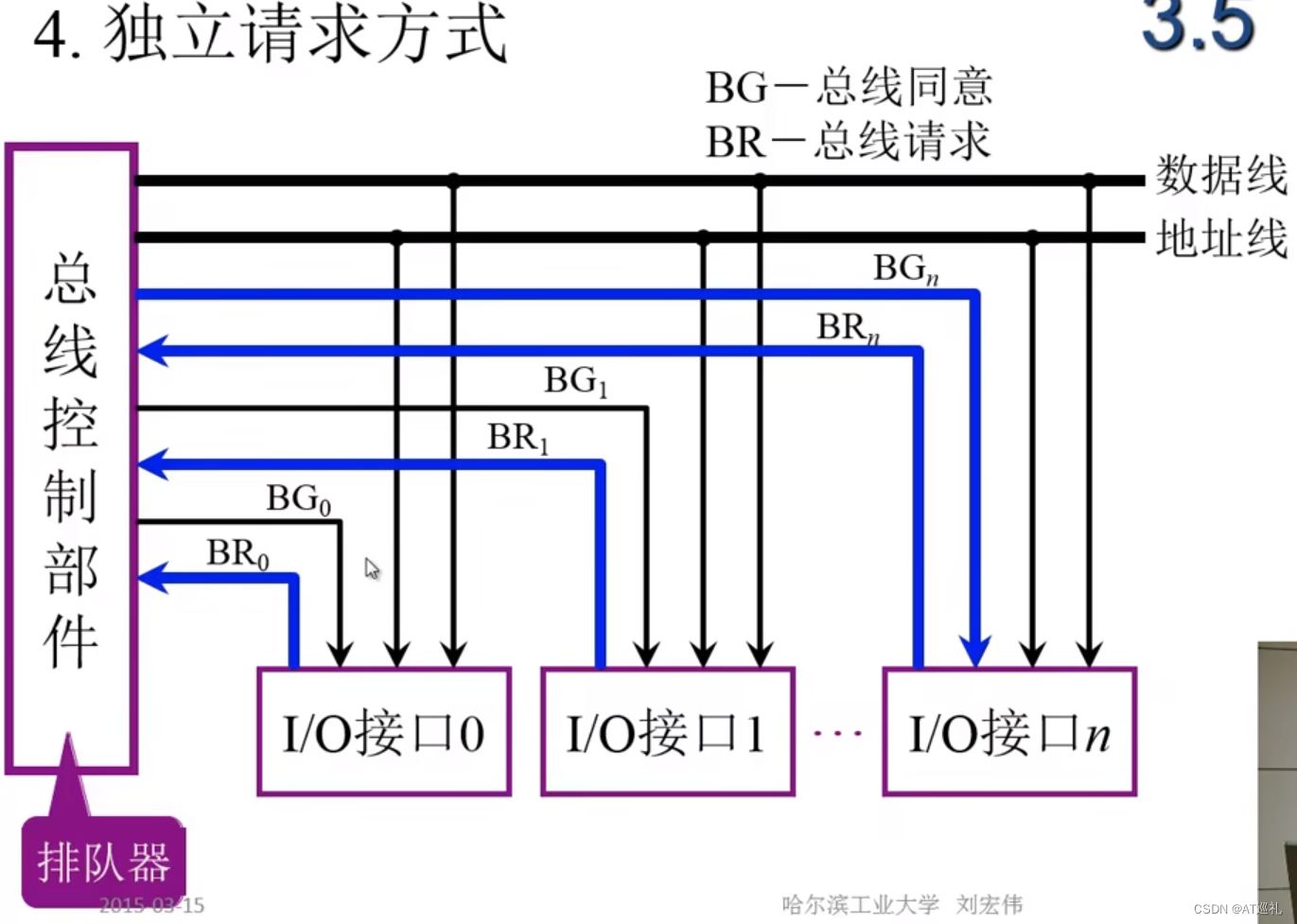

上诉三种的缺点如下图,总线会空闲,导致资源浪费