描述

网络是一组相互连接的引脚、端口和导线。每条电线都有一个网名

识别它。两条或多条导线可以具有相同的网络名称。所有电线共享一个公用网络

名称是单个NET的一部分,并且连接到这些导线的所有引脚或端口都是电气的

有联系的。

当net对象在

将RTL源文件细化或编译成网表设计。你也可以

手动为网络分配名称。

网络可以是具有单个信号的标量网络,也可以是总线网络,总线网络是

具有多个信号的标量网。总线是对相关信号进行分组的方便方式,

允许更少杂乱、更易于理解的示意图。它还阐明了这种联系

在主电路和块符号之间。公共汽车在以下方面特别有用:

•将多个信号从示意图的一侧路由到另一侧

•将多个信号连接到块符号

•连接多个信号,通过连接

到单个I/O标记

相关对象

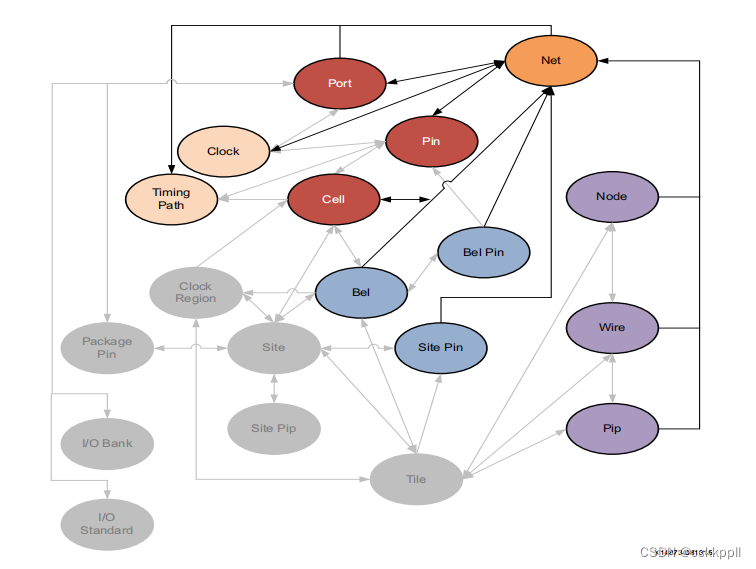

在设计网表中,NET可以连接到CELL的PIN或PORT.NET对象

还与通过PORT引入设计的CLOCK相关联,并且

TIMING_PATHs在设计中。NET也可以与DRC_VIOLATIONs相关联,以允许

您可以更快地定位和解决设计问题。您可以查询关联的网络

使用这些不同的设计对象:

get_nets-of[get_cells dbg_hub]

当设计被映射到目标Xilinx FPGA上时,NET被映射到路由

设备上的WIRE、NODE和PIP等资源,并通过连接到BEL

并且通过SITE_。您可以查询时钟、pin、端口、bel、bel_pin、,

与设计中的一个或多个特定网络相关联的site、site_pin、tile、node、pip、wire:

get_bel_pins-of[get_nets ddr4_sdram_adr[0]

属性

网络对象的特定属性可能会因网络类型的不同而有所不同

代表。下表列出了中分配给网络对象的一些属性

Vivado Design Suite,具有示例值:

Property Type Read-only Visible Value

AREA_GROUP string true true

BEL string true true

BLKNM string true true

BUFFER_TYPE enum false true

BUFG enum true true

BUS_NAME string true true DataIn_pad_0_i

BUS_START int true true 7

BUS_STOP int true true 0

BUS_WIDTH int true true 8

CLASS string true true net

CLOCK_BUFFER_TYPE enum false true

CLOCK_DEDICATED_ROUTE enum false true

CLOCK_REGION_ASSIGNMENT string false true

CLOCK_ROOT string* false true

COLLAPSE bool true true

COOL_CLK bool true true

DATA_GATE bool true true

DCI_VALUE int false true

DIFF_TERM bool false true

DIRECT_ENABLE bool false true

DIRECT_RESET bool false true

DONT_TOUCH bool false true

DRIVE int true false

DRIVER_COUNT int true true 1

ESSENTIAL_CLASSIFICATION_VALUE int false true

FILE_NAME string true true

FIXED_ROUTE string false true

FLAT_PIN_COUNT int true true 1

FLOAT bool true true

GATED_CLOCK bool false true

HBLKNM string true true

HD.NO_ROUTE_CONTAINMENT bool false true

HIERARCHICALNAME string true false top.DataIn_pad_0_i[0]

HU_SET string true false

IBUF_DELAY_VALUE double true true

IBUF_LOW_PWR bool false true

IFD_DELAY_VALUE double true true

IN_TERM enum true true

IOB enum false true

IOBDELAY enum false true

IOSTANDARD string true false LVCMOS18

IO_BUFFER_TYPE enum false true

IS_CONTAIN_ROUTING bool true true 0

IS_INTERNAL bool true true 0

IS_REUSED bool true true 0

IS_ROUTE_FIXED bool false true 0

KEEP bool true true

KEEPER bool true true

LINE_NUMBER int true true

LOC string true true

MARK_DEBUG bool false true 0

MAXDELAY double true true

MAXSKEW double true true

MAX_FANOUT string false true

METHODOLOGY_DRC_VIOS string false true

MULTI_CLOCK_ROOT string* false true

NAME string true true DataIn_pad_0_i[0]

NODELAY bool true true

NOREDUCE bool true true

OUT_TERM enum true true

PARENT string true true DataIn_pad_0_i[0]

PARENT_CELL string true true

PIN_COUNT int true true 1

PULLDOWN bool true true

PULLUP bool true true

PWR_MODE enum true true

RAM_STYLE enum false true

REUSE_STATUS enum true true

RLOC string true true

RLOC_ORIGIN string true false

RLOC_RANGE string true false

ROM_STYLE enum false true

ROUTE string false true

ROUTE_STATUS enum true true INTRASITE

RPM_GRID enum true true

RTL_KEEP string true false

RTL_MAX_FANOUT string true false

S bool true true

SCHMITT_TRIGGER bool true true

SLEW string true true

SUSPEND string true true

TYPE enum true true SIGNAL

USELOWSKEWLINES bool true true

USE_DSP48 enum false true

U_SET string true false

WEIGHT int false true

WIREAND bool true true

XBLKNM string true true

XLNX_LINE_COL int false false

XLNX_LINE_FILE long false false

_HAVE_MD_DT bool true false

async_reg string false true

要报告网络对象的特性,可以复制并粘贴以下命令

进入Vivado Design Suite Tcl外壳或Tcl控制台:

report_property -all [lindex [get_nets] 0]