1 MPSOC PL端

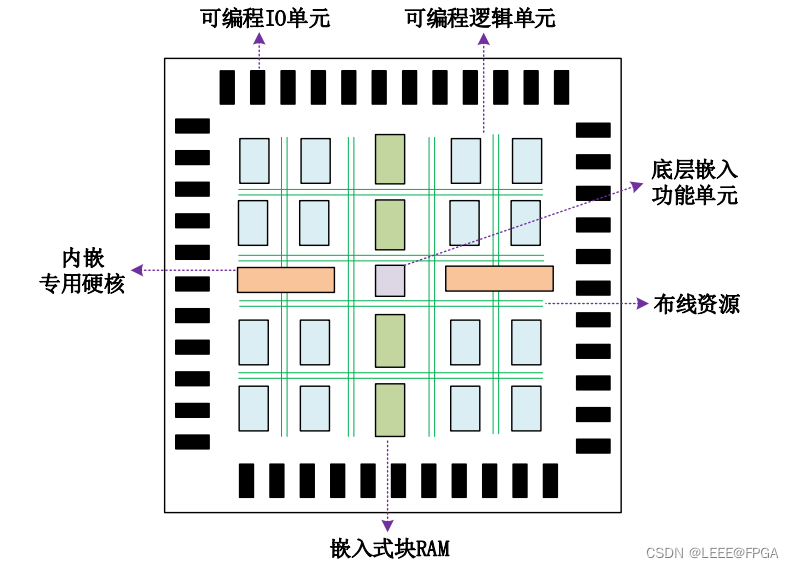

Zynq UltraScale+ MPSoC PL 部分等价于 FPGA。简化的 FPGA 基本结构由 6 部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等。

2 MPSOC PS端

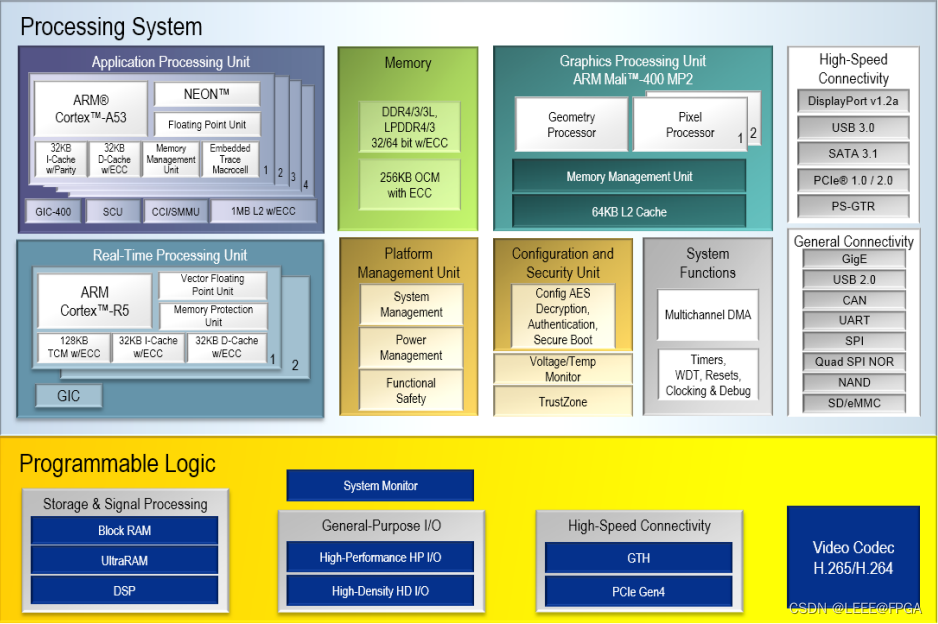

MPSoC 实际上是一个以处理器为核心的系统,PL 只是它的一个外设。MPSoC 系列的亮点在于它包含了完整的 ARM 处理器系统,且处理器系统中集成了内存控制器和大量的外设,使 Cortex-A53 处理器可以完全独立于可编程逻辑单元。而且实际上在 MPSoC 中,PL 和 PS 两部分的供电电路是独立的,这样 PS 或 PL 部分不被使用的话就可以被断电。

SOPC--FPGA 可以用来搭建嵌入式处理器,像 Xilinx 的 MicroBlaze 处理器或者 Altera 的 Nios II 处理器。像这种使用 FPGA 的可编程逻辑资源搭建的处理器我们称之为"软核"处理器,它的优势在于处理器的数量以及实现方式的灵活性。

而 MPSoC 中集成的是一颗"硬核"处理器,它是硅芯片上专用且经过优化的硬件电路,硬核处理器的优势是它可以获得相对较高的性能。另外,MPSoC 中的硬件处理器和软核处理器并不冲突,我们完全可以使用 PL 的逻辑资源搭建一个 Microblaze 软核处理器,来和 ARM 硬核处理器协同工作。MPSoC 处理器系统集成了 Arm Cortex-A53 和 Arm Cortex-R5F 内核处理器,并且像 EG、EV 器件还集成了图像处理单元,再加上丰富的外设接口,可以说 MPSoC 的 PS 端是一个非常优秀的片上系统。

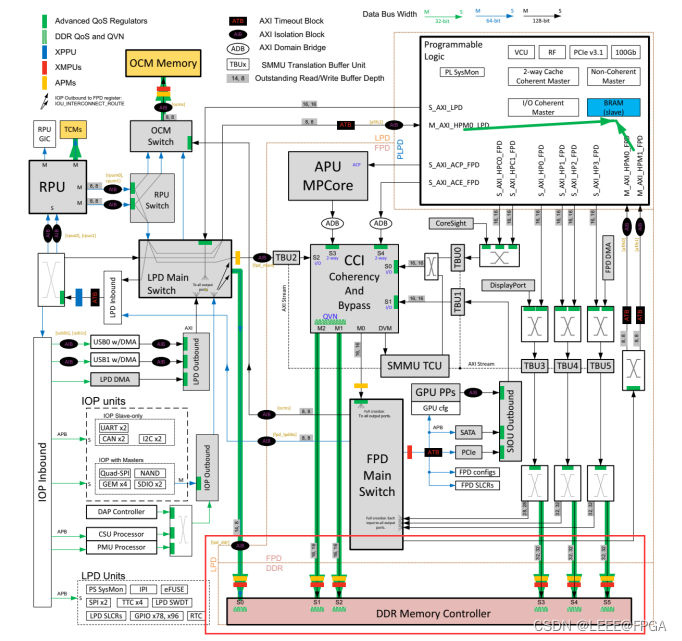

从上面的结构图中可以很清楚的看到 MPSoC 的结构,它分为 PS 和 PL 两部分。在 PS 部分中它主要由Arm Cortex-A53(APU 共 4 个核)、Arm Cortex-R5F(RPU 共两个核)以及 Arm Mali-400 MP2(GPU)三种内核处理器构成,并且还包括 DDR 控制单元、平台管理单元、高速外设控制器以及普通外设控制器等外设组成。

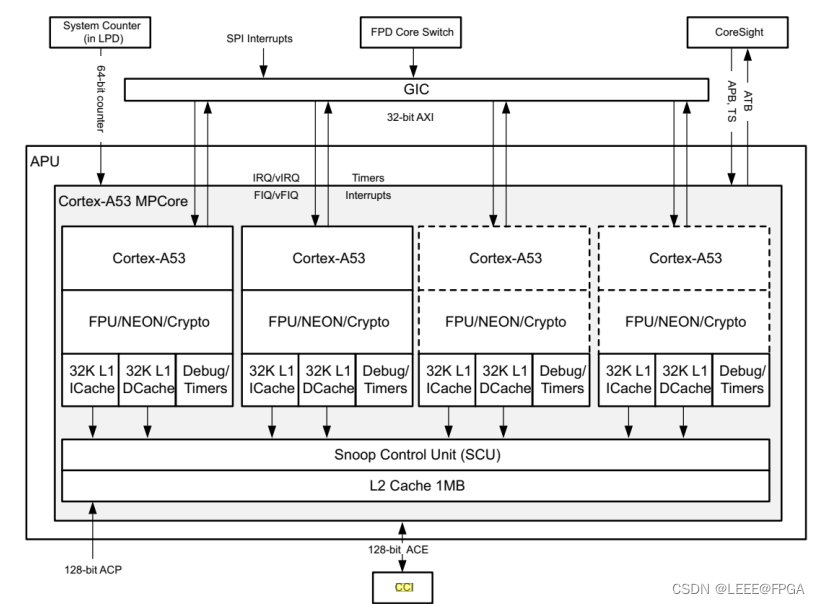

1)APU(Application Processing Unit)

APU 主要是由两个或者四个 ARM 处理器核组成的,Cortex-A53 核心是基于 Arm-v8A 架构的 32 位/64位应用程序处理器,拥有极佳的性能/功率比,每一个 Cortex-A53 核心拥有 32KB 指令和数据 L1 缓存,具有奇偶校验、ECC 保护、NEON SIMD 引擎、单精度和双精度浮点单元。除了这些模块,APU 还有一个 snoop控制单元以及一个带 ECC 保护的 1MB L2 缓存,这样的设计可以更好的提高系统级的性能。该 APU 还具有内置的中断控制器支持虚拟中断。

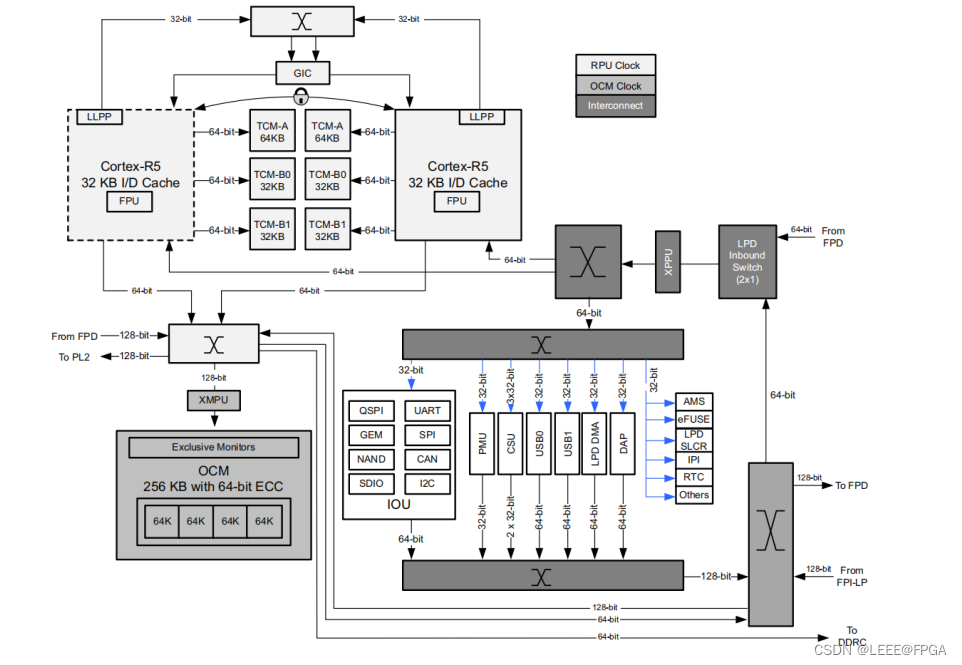

2) RPU(Real-Time Processing Unit)

PS 中的 RPU 包含一个双核 Arm Cortex-R5F 处理器,Cortex-R5F 是 32 位实时处理器,它是基于 Arm-v7R架构的处理器内核。每个 Cortex-R5F 核都有 32KB 的指令和数据缓存(L1),除了 L1 缓存,每个 Cortex-R5F核心还具有 128KB 的紧耦合内存(TCM)接口,用于实时单周期访问。RPU 还有一个专用的中断控制器。两个 RPU 既可工作在独立模式,也可以工作在同步模式。在独立模式中两个处理器都是独立运行的;在同步模式下,它们彼此并行运行,逻辑资源也会综合到一起,并且 TCM 资源也整合成 256KB。RPU 还可以通过 AXI-4 端口与 PS 端的 LPD 区域进行通信或者与 PL 端进行低延迟通信。支持实时 DEBUG 和信号跟踪,每个内核还具有一个嵌入式跟踪宏单元(ETM)方便 Arm 内核调试。Cortex-R5 处理器是用于深度嵌入式实时系统的 CPU,它采用了 Thumb-2 技术以获得最佳的代码密度和处理吞吐量,它还具有一个算术逻辑单元(ALU),为了更加有效地利用其他资源(例如寄存器资源),算术逻辑单元会执行有限的双重指令。Cortex-R5 处理器会通过重新启动和加载多个指令来保持较低的中断延迟,并且还会使用一个专用的外围端口来实现对中断控制器的低延迟访问。处理器具有紧密耦合内存(TCM)端口,用于低延迟和确定性地访问本地 RAM。错误检查和纠正功能(ECC)是用于 Cortex-R5 处理器端口和 Level 1 (L1)存储器的,这样可以提高系统的可靠性和准确性。

3)GPU(Graphics Processing Unit)

GPU 是基于 Arm Mali-400 MP2 硬件加速器的 2D 和 3D 图形子系统。它由一个几何图形处理器(GP)、两个像素处理器(PP)、64KB L2 缓存控制器(L2)、针对 GP 和每个 PP 的独立内存管理单元(MMU)以及128 位 AXI 总线接口构成。Arm Mali-400 MP2 作为 PS 专用的图形处理器它可以支持 2D 和 3D 图形加速,最高分辨率为 1080p,对于 3D 图形它能够支持 OpenGL ES 1.1 and 2.0 规范而对于 2D 的矢量图形它只能支持 Open VG 1.1 标准。它的几何处理器(GP)和 2 个像素处理器会并行地执行贴图渲染操作。它为 GP 和像素处理器提供了专用的内存管理单元,支持 4 KB 的页面大小。

GPU 还有 64KB 的二级(L2)只读缓存,它支持 4X 和 16X 全场景抗锯齿(FSAA)功能。它有内置的硬件纹理解压缩,允许纹理在图形硬件中保持压缩(ETC 格式),并在运行中解压所需的样本。它还支持在不消耗额外带宽的情况下有效地混合多个硬件层,它的像素填充率为 200 万像素/秒/MHz,三角形填充率为0.1Mvertex/秒/MHz。GPU 支持广泛的纹理格式为 RGBA 8888、565、1556 以及 YUV 格式,对于功率敏感的应用,GPU 支持对每个 GP、像素处理器和 L2 缓存的时钟和功率进行门控。在功率门控过程中,GPU 不消耗任何静态或动态功率;在时钟门控过程中,它只消耗静态电源。

4)DDR Memory Controller

DDR 存储控制器通过六个 AXI 数据接口和一个 AXI 控制接口连接到 MPSoC 的其余部分,其中一条数据路径连接到实时处理单元(RPU),两条数据路径连接到缓存相干互连(CCI-400),其他的在 DisplayPort 控制器、FPD、DMA 和编程逻辑(PL) 上多路复用。在 6 个接口中,5 个是 128 位宽,而第 6 个接口(绑定到RPU)是 64 位宽。DDR 子系统支持 DDR3,DDR3L、LPDDR3、DDR4 和 LPDDR4,它可以通过 AXI 总线接口接收来自 6 个应用主机端口的读写请求,这些请求在内部排队访问 DRAM 设备。存储器控制器在 DDR PHY 接口上向 PHY 模块发出命令,PHY 模块从 DRAM 中读取和写入数据。DDR Memory Controller 的结构如下图所示:

5) PMU(Platform Management Unit)

Zynq UltraScale+ MPSoC 包括一个专用的用户可编程处理器,用于电源、错误管理的平台测量单元(PMU)处理器,以及用于功能安全应用的可选软件测试库(STL)。

PMU 的功能如下:

1、 使用系统监视器检查电源水平,以确保 CSU 和 LP 域的其余部分正常运行。

2、 初始化 pll 的默认配置和他们潜在的旁路。

3、 触发和排序必要的扫描和 MBIST。

4、 捕获并发出错误信号,错误 ID 可以通过 JTAG 读取。

5、 释放复位到 CSU。

6、 在应用程序和实时处理器处于睡眠状态时充当它们的委托,并在接收到它们的唤醒请求之后对他们进行开机和重启。

7、 在任何时候维护系统电源状态。

8、 处理不同块的上电、下电、复位、内存内置自修复(MBISR)、MBIST 和扫描归零所需的低级事件序列。

9、 在休眠模式下管理系统,并基于各种触发机制唤醒系统。

10、 PS-level 错误捕获。

6)High-Speed Connect

Zynq UltraScale+ MPSoC 的 PS 端集成了 5 个高速外设,分别是 DP 控制器、USB3.0 控制器、SATA3.1控制器、PCIE 1.0/2.0 控制器以及 PS-GTR 收发器。下面我们来分别介绍一下这几个高速控制器。

1、 DP 接口(DisplayPort 控制器):Zynq UltraScale+ MPSoC 的 PS 端集成了 DisplayPort 控制器,它可以从内存(非实时输入)或(实时输入)可编程逻辑(PL)中获取数据,并将这些数据处理过后通过DisplayPort 源控制器块输出到外部显示设备或 PL(实时输出)上。DisplayPort 控制器由 DMA、缓冲区管理器、显示渲染块、音频混音块、DisplayPort 源控制器以及 PS-GTR 模块组成,它可以支持超高清(UHD)视频,因此 DP 接口常用来做视频图像传输的接口。

2、 USB3.0:USB 3.0 控制器由两个独立的 DRD (dual-role device)控制器组成,两者都可以单独配置为在任何给定时间作为主机或从机设备工作的模式。USB 3.0 DRD 控制器通过高级的可扩展 AXI 从接口,可以为系统软件提供一个可扩展的主控制器接口(xHCI)。控制器中有一个内部的 DMA 引擎,它利用 AXI 主接口来传输数据。三个双端口 RAM 的配置可以实现 RX 数据 FIFO、TX 数据 FIFO和描述符/寄存器缓存功能传输的功能,AXI 主端口与协议层可以通过缓冲区管理单元访问不同的RAM。

3、 SATA3.1:SATA 控制器是一种高性能双端口主机控制器,具有 AHCI 兼容的命令层,该命令层对使用端口乘法器的系统来说,具有支持基于本地命令队列和帧信息结构(FIS)交换的高级功能。SATA使用 ATA/ATAPI 命令集,但是通过不同的导线可以实现与 SATA 第 1 代、第 2 代或第 3 代相对应的 1.5、3.0 或 6.0 Gb/sec 的速率进行串行通信。串行数据采用 8B/10B 编码,确保数据模式中有足够的转换以确保直流平衡(这里的转换指数据的 0/1 转换,关于直流平衡的知识大家可以自行了解或者看我们 HDMI 相关的视频,其中有涉及),并使时钟数据恢复电路能够从输入数据模式中提取时钟。

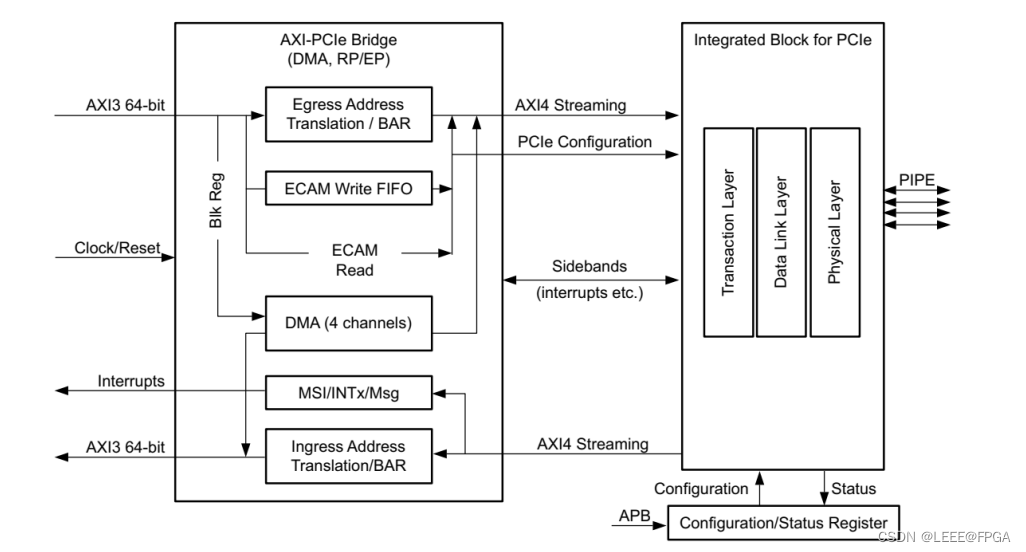

4、 PCIe 1.0/2.0 控制器:MPSoC 集成了一个 PCIe 通信控制器,用于实现 PCIe 的通信,它包含 AXI-PCIe桥和 DMA 组件,AXI-PCIe 桥主要是为 PCIe 和 AXI 提供高性能桥接。

5、 PS-GTR 收发器:千兆 GTR 收发器为串行输入输出单元(SIOU)的外围设备、媒体访问控制器(mac)以及它们的高速通信链路提供专用的 I/O。Zynq UltraScale+ MPSoC 共有四个可编程高速收发器,可以支持数据速率高达 6gb /s 的子层协议。

7)普通外设控制器

Zynq UltraScale+ MPSoC 的 PS 端除了集成的高速通信外设之外,还有一些普通的低速外设,其中包括GigE、USB2.0、CAN、UART、SPI、Quad SPI NOR、NAND 以及 SD/eMMC 等外设控制器。

8)PS-PL AXI 接口

MPSoC 将高性能 ARM Cotex-A 系列处理器与高性能 FPGA 在单芯片内紧密结合,为设计带来了如减小体积和功耗、降低设计风险,增加设计灵活性等诸多优点。在将不同工艺特征的处理器与 FPGA 融合在一个芯片上之后,片内处理器与 FPGA 之间的互联通路就成了 MPSoC 芯片设计的重中之重。如果 Cotex-A53与 FPGA 之间的数据交互成为瓶颈,那么处理器与 FPGA 结合的性能优势就不能发挥出来。

Xilinx 从 Spartan-6 和 Virtex-6 系列开始使用 AXI 协议来连接 IP 核。在 7 系列、Zynq-7000 和 Zynq UltraScale+ MPSoC 器件中,Xilinx 在 IP 核中继续使用 AXI 协议。AXI 的英文全称是 Advanced eXtensible Interface,即高级可扩展接口,它是 ARM 公司所提出的 AMBA(Advanced Microcontroller Bus Architecture)协议的一部分。

3 MPSoC 芯片命名规则

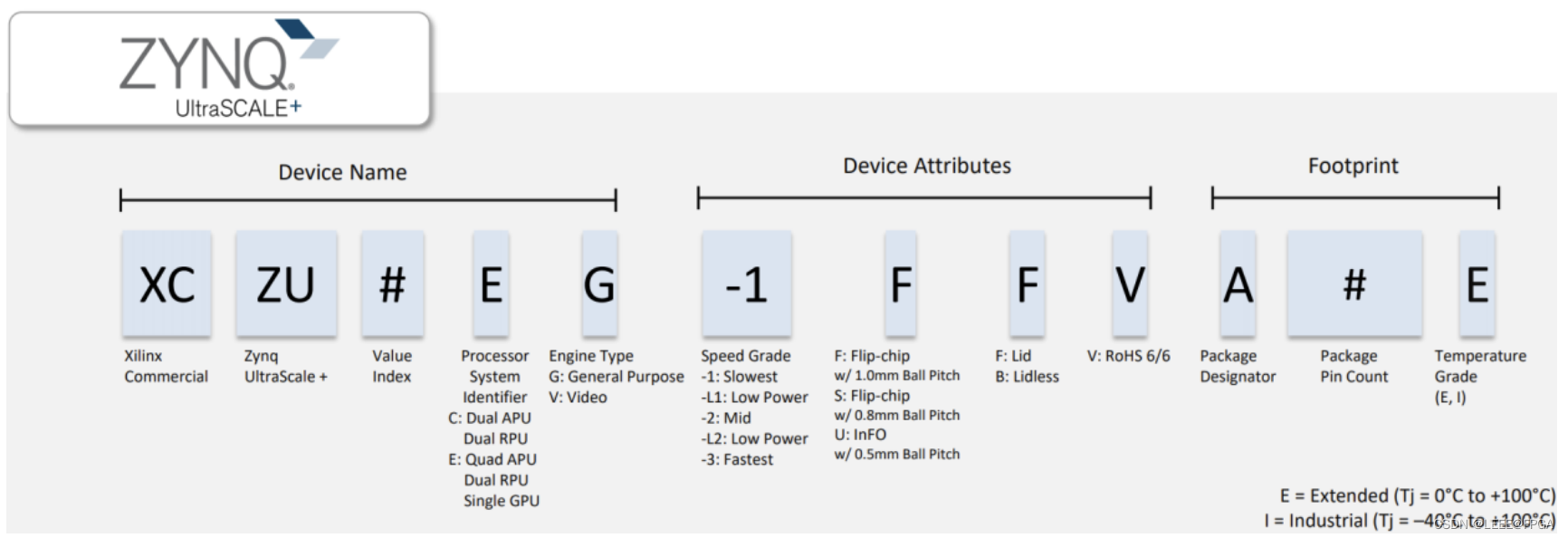

Zynq UltraScale+ MPSoC 产品命名规则如下图所示:

以 ZU+系列"XCZU4EV-SFVC784-1-I"为例,"XC"是"Xilinx 公司";"ZU"是芯片系列是 Zynq

UltraScale+;"4"是价值索引(Value Index),该数值越大对应芯片内部资源越丰富,价值越高;"E"是

处理器类型,"E"代表四核 APU,双核 RPU 以及一个 GPU;"V"是引擎类型,V 代表视频解码器类型;

"sfvc784"芯片封装信息,"SFVC"是芯片制造工艺信息,"784"是芯片封装引脚计数(Package Pin Count);

"-1"是速度等级(Speed Grade);"-I"是温度等级(Temperature Grade),温度等级有两种标准,分别

是"E"与"I"。

E:扩展级,表示芯片可以工作在 0°C 到+100°C;

I:工业级,表示芯片可以工作在-40°C 到+100°C。