目录

描述

题目描述:

使用状态机实现时钟分频,要求对时钟进行四分频,占空比为0.25

信号示意图:

clk为时钟

rst为低电平复位

clk_out 信号输出

Ps 本题题解是按照1000的状态转移进行的,不按照此状态进行,编译器可能报错但没有影响。

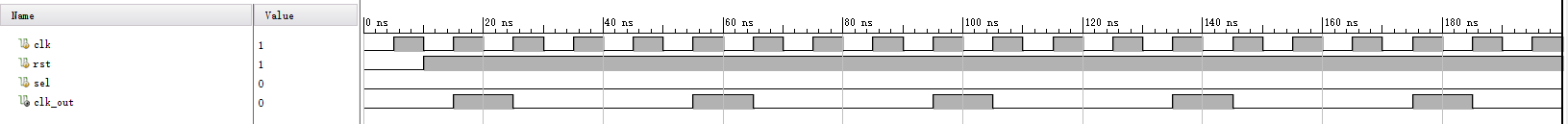

波形示意图:

输入描述:

clk为时钟

rst为低电平复位

输出描述:

clk_out 信号输出

参考代码

cpp

`timescale 1ns/1ns

module huawei7(

input wire clk ,

input wire rst ,

output reg clk_out

);

//*************code***********//

parameter [1:0] s0 = 2'b00,

s1 = 2'b01,

s2 = 2'b10,

s3 = 2'b11;

reg [1:0] state, next_state;

always @ (posedge clk, negedge rst) begin

if(!rst)

state <= s0;

else

state <= next_state;

end

always @ (state) begin

case(state)

s0: begin

next_state <= s1;

clk_out <= 1'b0;

end

s1: begin

next_state <= s2;

clk_out <= 1'b1;

end

s2: begin

next_state <= s3;

clk_out <= 1'b0;

end

s3: begin

next_state <= s0;

clk_out <= 1'b0;

end

default: begin

next_state <= s0;

clk_out <= 1'b0;

end

endcase

end

//*************code***********//

endmodule