目录

-

- [1 SDRAM](#1 SDRAM)

-

- [1.1 同步动态随机存储器](#1.1 同步动态随机存储器)

- [1.2 位宽](#1.2 位宽)

- [1.3 SDRAM结构](#1.3 SDRAM结构)

- [1.4 SDRAM引脚图](#1.4 SDRAM引脚图)

- [2 SDRAM操作指令](#2 SDRAM操作指令)

-

- [2.1 读写指令](#2.1 读写指令)

- [2.2 刷新和预充电](#2.2 刷新和预充电)

- [2.3 配置模式寄存器](#2.3 配置模式寄存器)

- [2.4 读/写突发](#2.4 读/写突发)

- [2.5 数据屏蔽](#2.5 数据屏蔽)

SDRAM是DDR3的基础,在学习DDR3之前,我们先来学习一下SDRAM的相关知识。

1 SDRAM

1.1 同步动态随机存储器

- SDRAM:synchronous dynamic random access memory

- 同步:其时钟频率与CPU前端总线的系统时钟频率相同,且内部命令的发送和数据的传输都以该时钟频率为基准

- 动态:SDRAM是易失性存储器,需要不断刷新以保证数据不丢失

- 随机:数据存储的位置可自由指定

1.2 位宽

- 物理Bank = CPU位宽

- 逻辑Bank:SDRAM内部划分的片区,一个SDRAM有多个逻辑Bank

- 芯片位宽 = 每片SDRAM的位宽

1.3 SDRAM结构

- 逻辑Bank

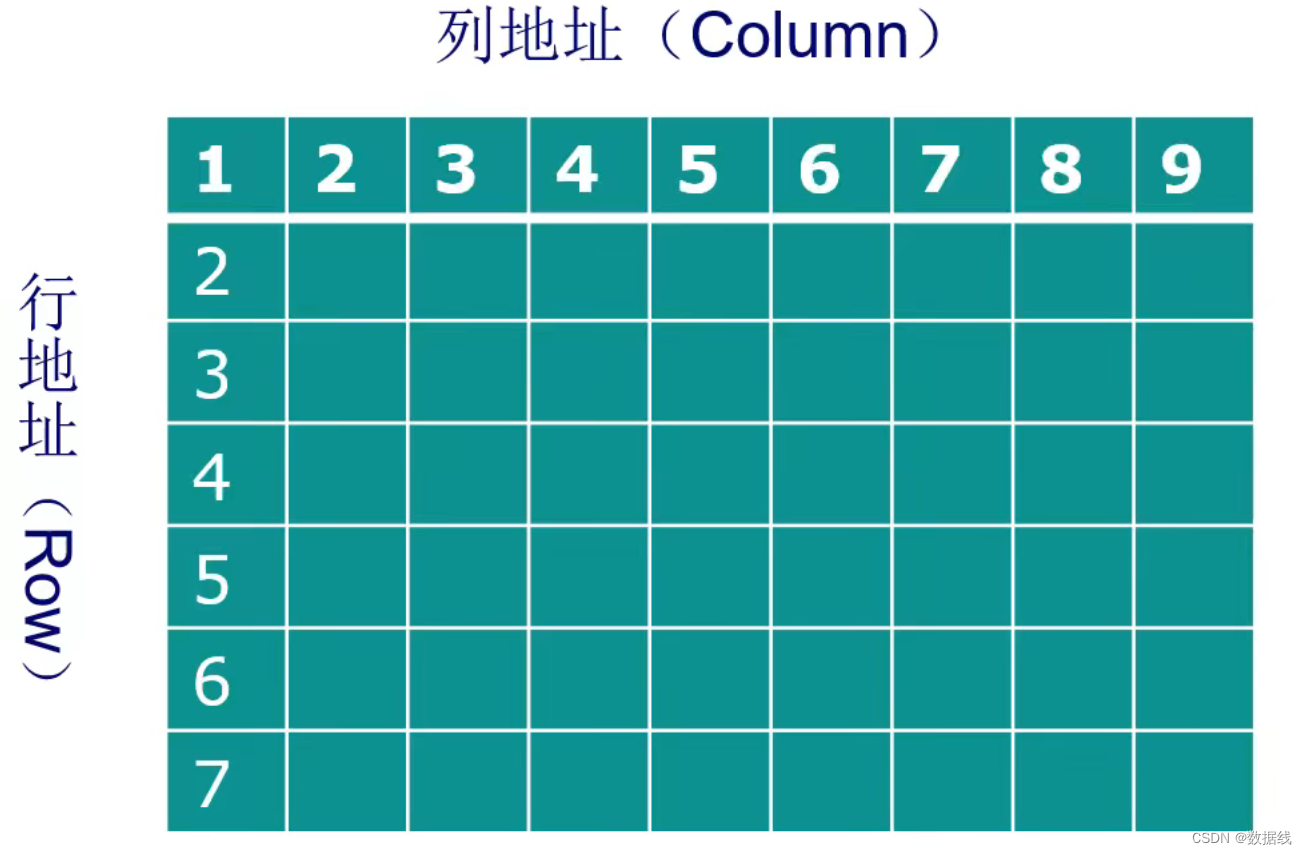

下图为一个逻辑Bank的示意图,由7行9列构成,每个单元携带m个bit,m是芯片位宽。

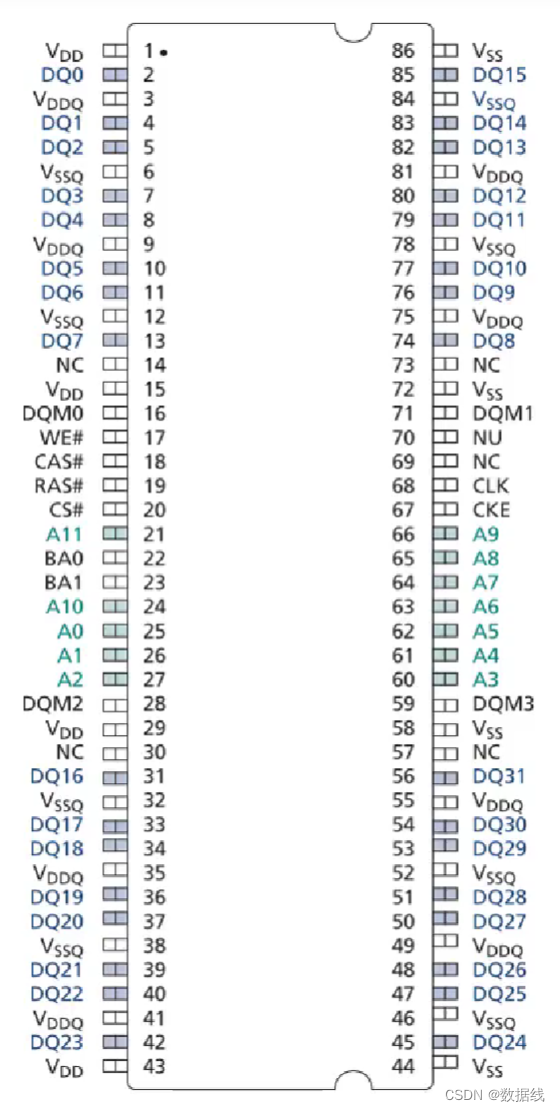

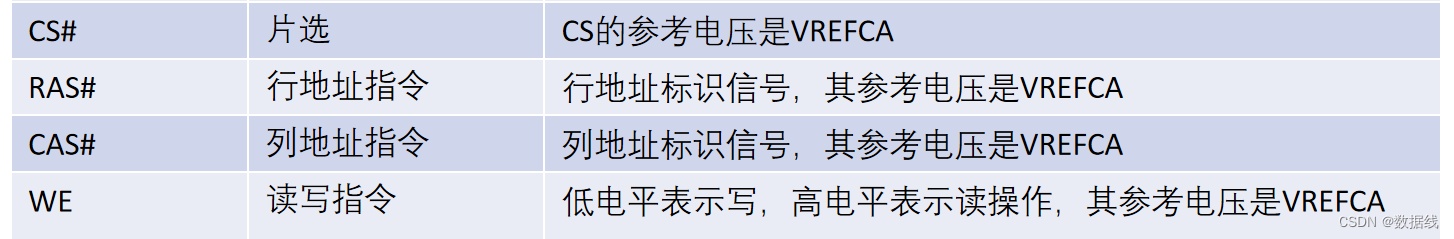

1.4 SDRAM引脚图

- 常用引脚

| 名称 | 引脚号 |

|---|---|

| 时钟线 | CLK |

| 时钟使能 | CKE |

| 行列地址 | A0~A11(行列地址总线共用) |

| Bank地址 | BA0、BA1 |

| 数据线 | DQ0~DQ31 |

| 数据掩码 | DQM |

| 命令总线 | WE#、CAS#、RAS#、CS# |

DQM线在作用时,如果是对写操作进行数据掩码,则DQM会阻止写入,如果对读操作进行数据掩码,则会在数据读出后再屏蔽掉。

- 其他引脚

| 名称 | 引脚号 |

|---|---|

| 电源 | VDD、VSS |

| 不连接 | NC |

2 SDRAM操作指令

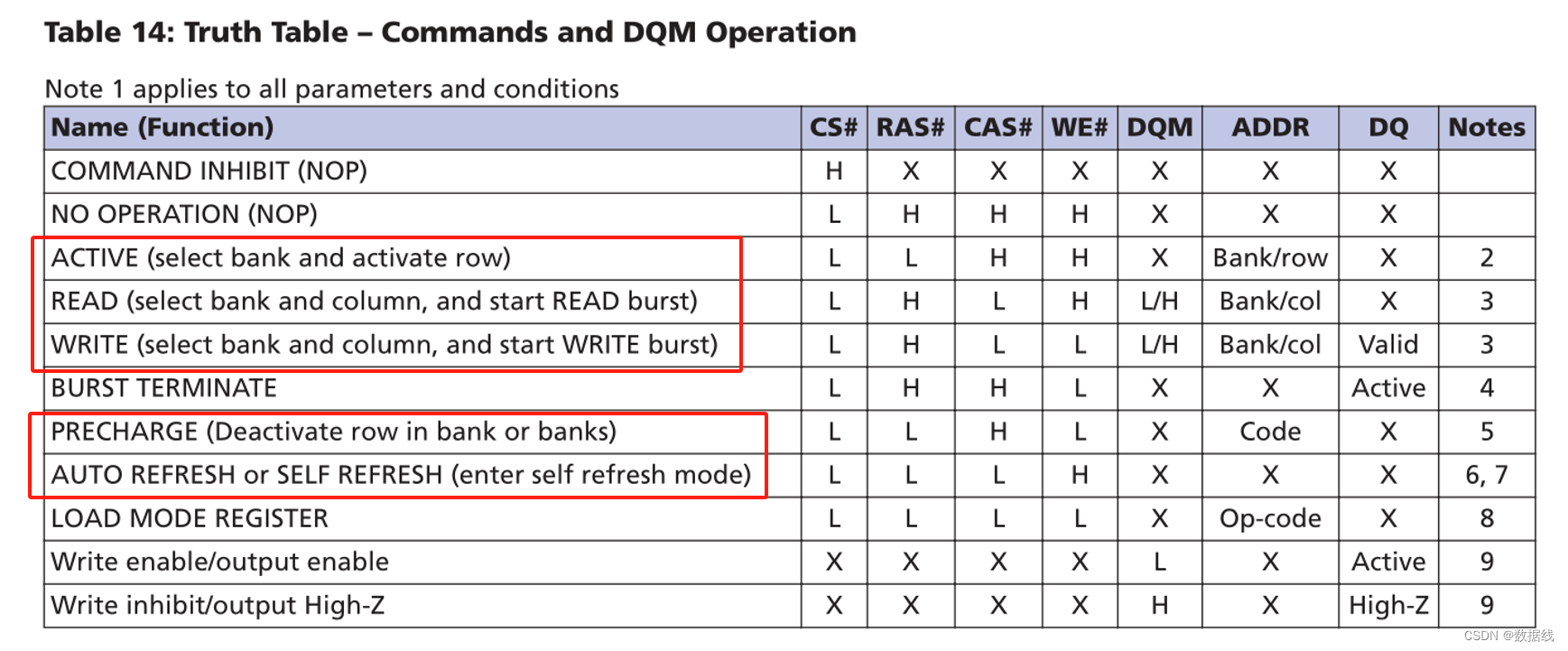

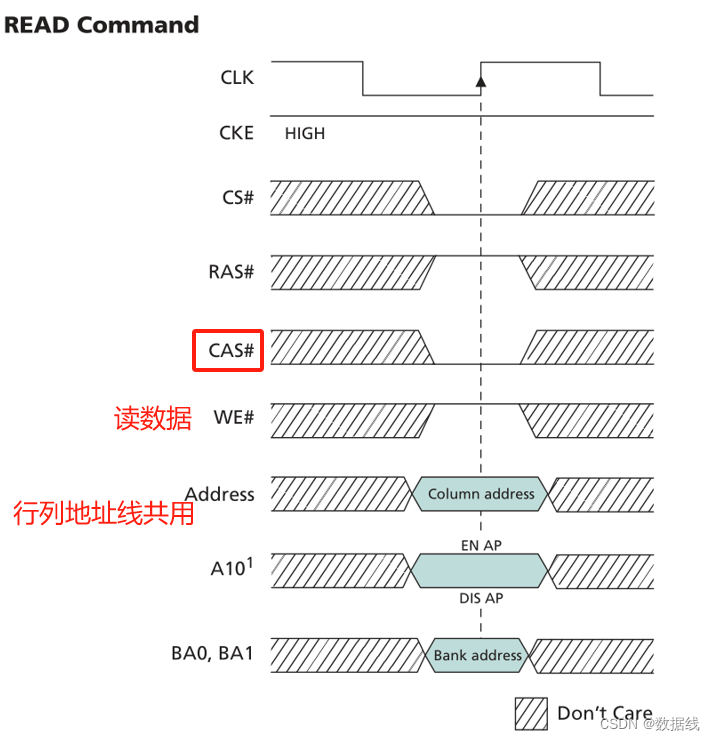

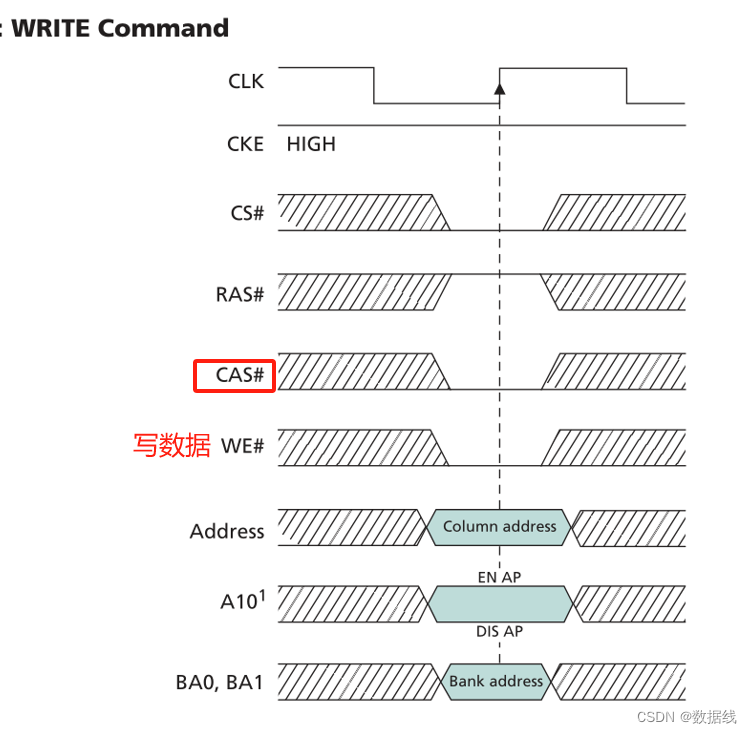

2.1 读写指令

- step1:激活命令,在读写操作之前,激活行地址和bank地址

- 行激活和Bank激活是同一个指令,激活了某一行也就激活了对应的Bank

- step 2:读写命令,列激活命令和读写指令是同时进行的

- ACTIVE指令前需要先进行预充电,即PRECHARGE指令

2.2 刷新和预充电

每读/写完一次后要进行预充电以保证数据不丢失,预充电分为手动和自动。刷新和预充电的区别在于刷新具有周期性和全面性。周期性指的是每隔多少ms进行一次刷新,全面性指的是对所有bank进行刷新。

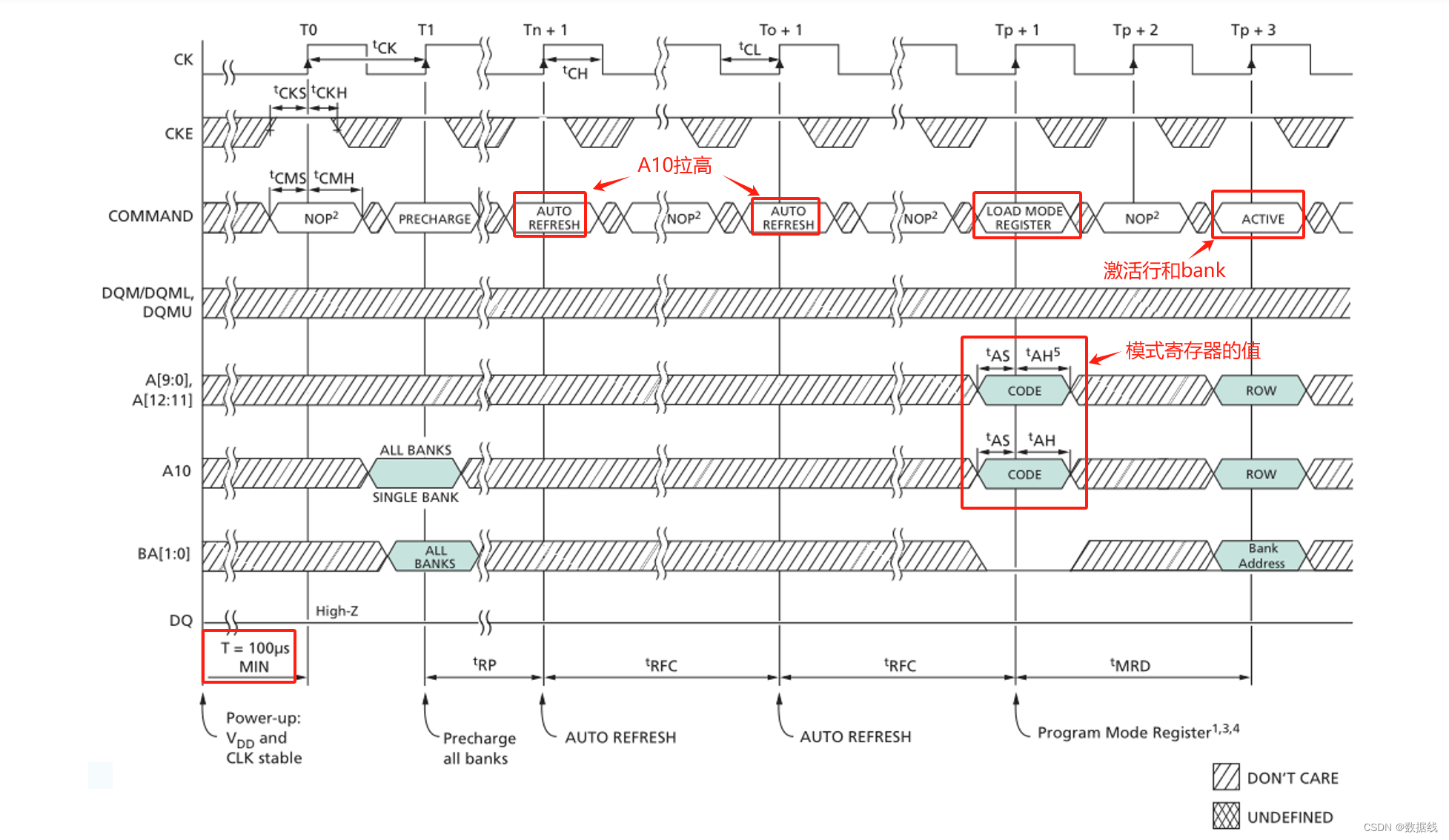

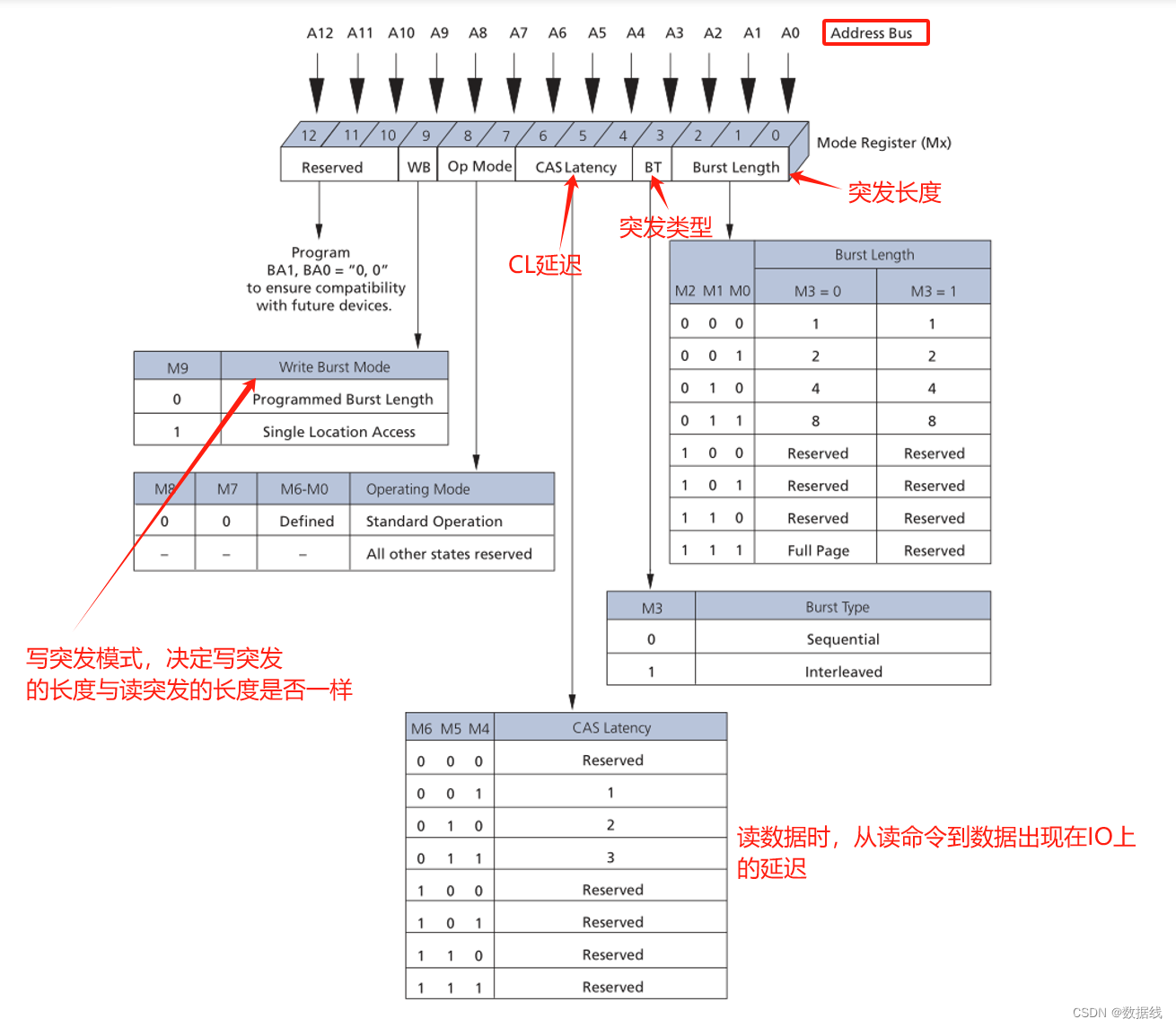

2.3 配置模式寄存器

- 下图是配置模式寄存器在SDRAM操作时序中的位置

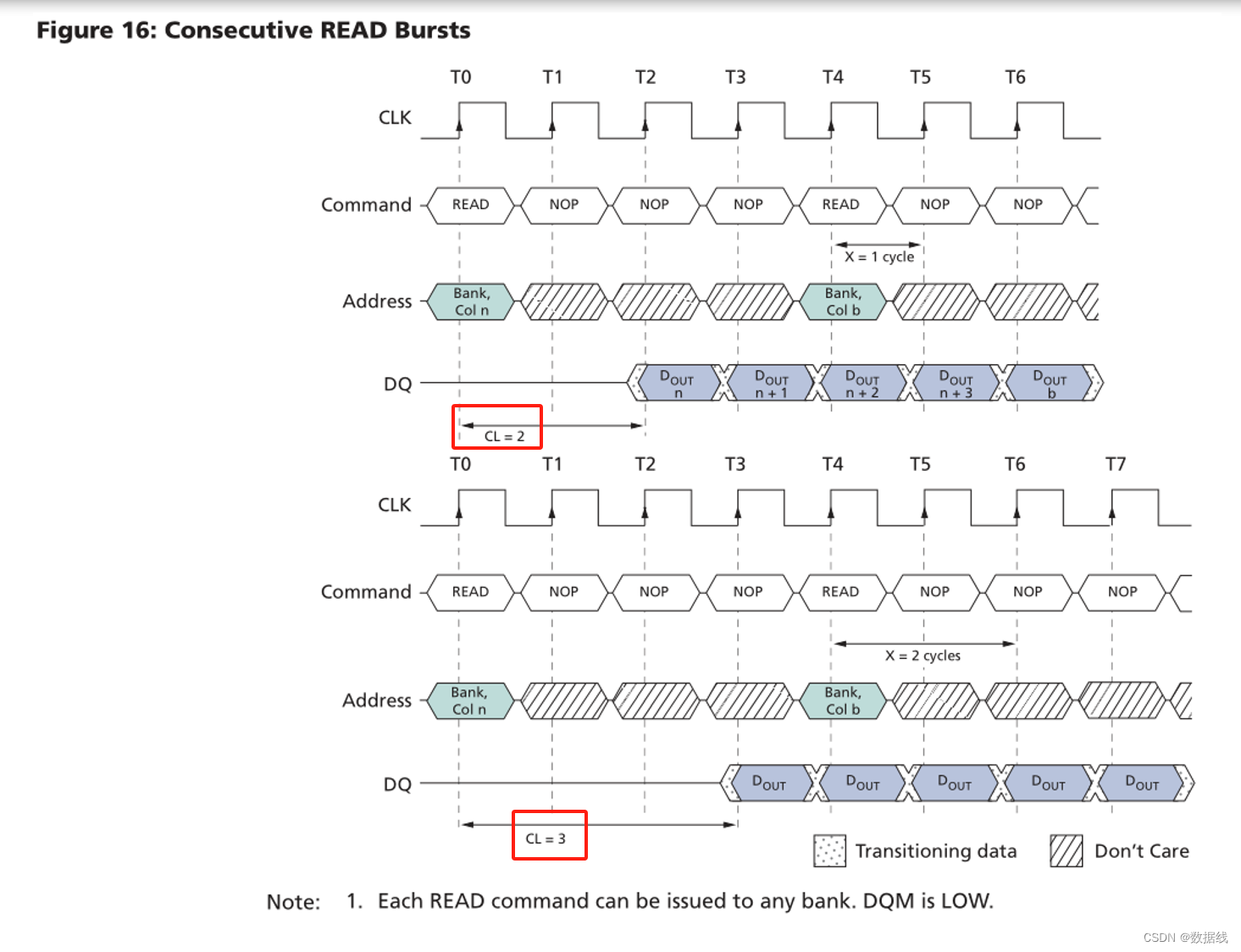

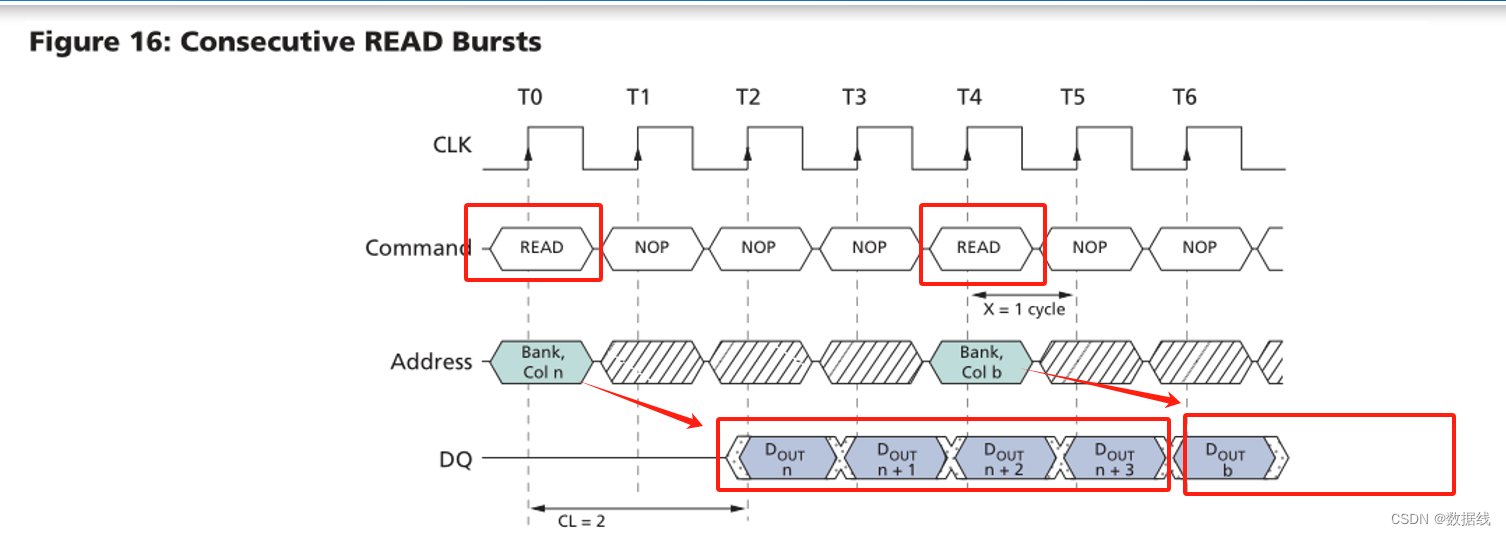

CL:从列地址激活到数据出现在IO上的延迟,读数据时的CL:

2.4 读/写突发

2.5 数据屏蔽

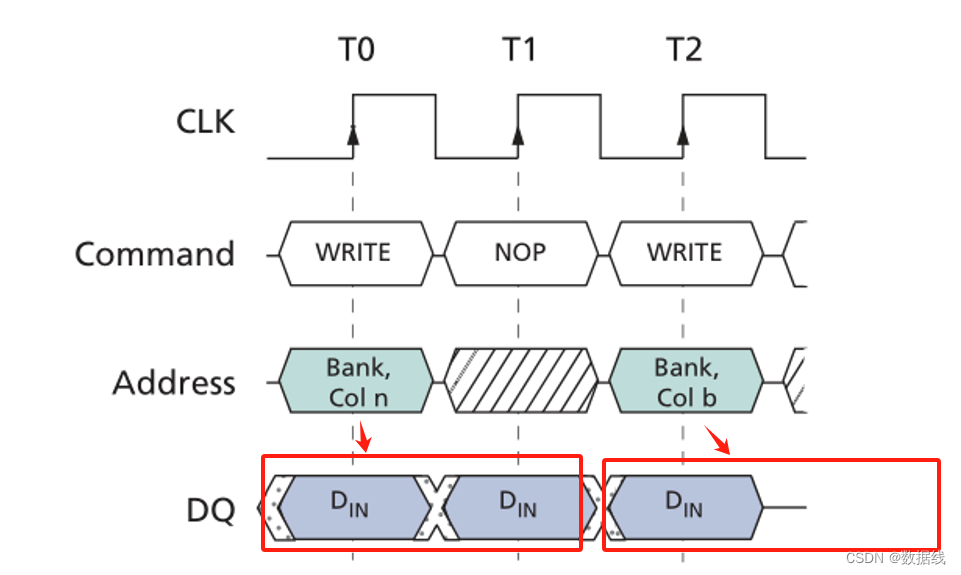

- 写数据屏蔽和读数据屏蔽的区别

在写数据屏蔽时,会直接将写数据屏蔽掉,让数据写不进去。在读数据的过程中,无法直接屏蔽(无法阻止数据读出,但读出数据之后会通过读数据寄存器,将不想要的数据屏蔽掉。 - 写入/读出数据时,DQM的区别

写入数据时,DQM为低时的数据被写入,DQM拉高时数据被屏蔽。

读出数据时,DQM有CL的延迟。