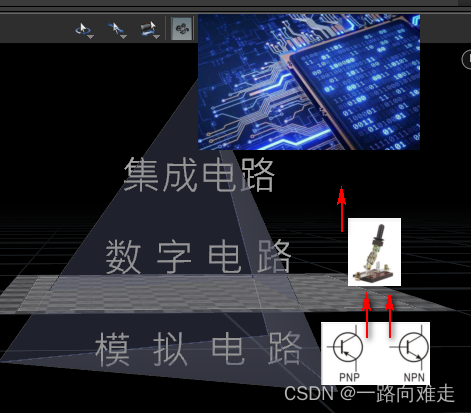

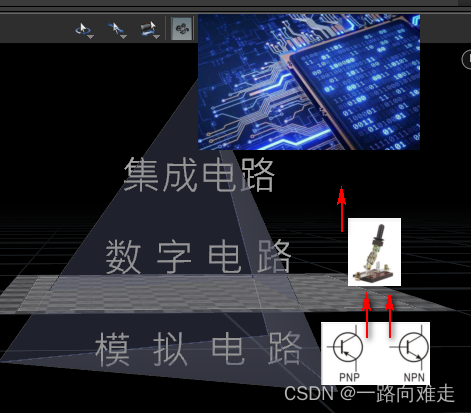

类似于面包板上搭建电路,但是使用的是逻辑单元模块;如加法器,减法器,寄存器等

没有模拟电路的电容,电阻;但是逻辑单元的底层实现,使用MOS管等电路实现电路的开关;从而表示0,1;

速度的理想值,应该取决于开关管的速度;时序逻辑的速度取决于时钟的频率设置

而连线的实现,应该是由开关管的开关来实现断开,连接不同的器件(通过内存的01值,直接决定连线的断开,连接,实现硬连接

类似于面包板上搭建电路,但是使用的是逻辑单元模块;如加法器,减法器,寄存器等

没有模拟电路的电容,电阻;但是逻辑单元的底层实现,使用MOS管等电路实现电路的开关;从而表示0,1;

速度的理想值,应该取决于开关管的速度;时序逻辑的速度取决于时钟的频率设置

而连线的实现,应该是由开关管的开关来实现断开,连接不同的器件(通过内存的01值,直接决定连线的断开,连接,实现硬连接