目录

描述

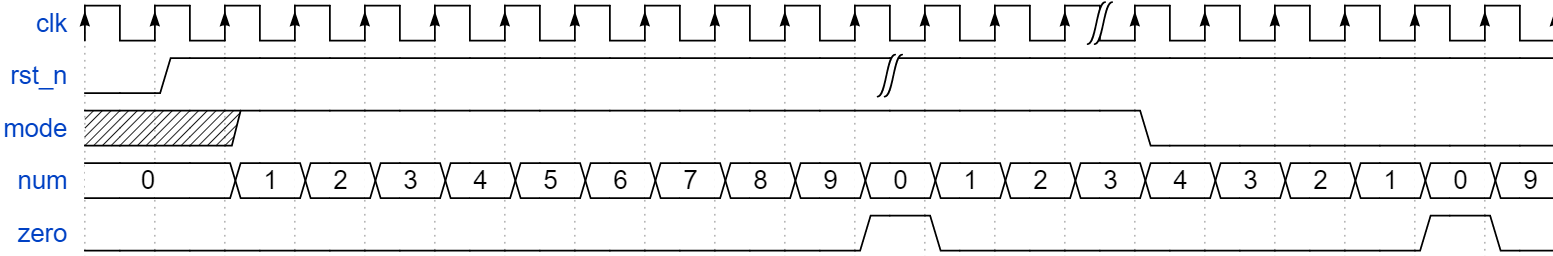

请编写一个十进制计数器模块,当mode信号为1,计数器输出信号递增,当mode信号为0,计数器输出信号递减。每次到达0,给出指示信号zero。

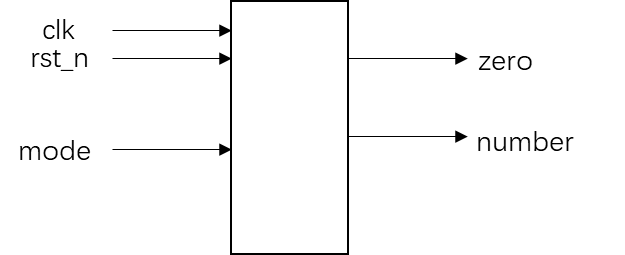

模块的接口信号图如下:

模块的时序图如下:

请使用Verilog HDL实现以上功能,并编写testbench验证模块的功能

输入描述:

clk:系统时钟信号

rst_n:复位信号,低电平有效

mode:模式选择信号,当该信号为1,计数器每个时钟加一;为0,则每个时钟减一。

输出描述:

number:4比特位宽,计数器当前输出读数。

zero:过零指示信号,当number为0时,该信号为1,其他时刻为0.

参考代码

cpp

`timescale 1ns/1ns

module count_module(

input clk,

input rst_n,

input mode,

output reg [3:0]number,

output reg zero

);

reg [3:0]num;

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

zero <= 1'd0;

end

else if (num == 4'd0)

begin

zero <= 1'b1;

end

else

begin

zero <= 1'b0;

end

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

num <= 4'b0;

end

else if(mode)

begin

if(num == 9)

num <= 0;

else

num <= num + 1'd1;

end

else if(!mode)

begin

if(num == 0)

num <= 9;

else

num <= num - 1'd1;

end

else num <= num;

always @(posedge clk or negedge rst_n)

if (!rst_n)

begin

number <= 4'd0;

end

else

begin

number <= num;

end

endmodule