一、简介

在我们进行FPGA进行开发时通常都会经历代码编写,仿真,下板验证等过程。使用FPGA进行开发的小伙伴都知道,在代码编写时往往花费不了太长的时间,下板验证更是。在开发中占绝大部分时间的是仿真,有时候编写代码只需要1天,而仿真就需要几天才能调试出来。而仿真有分为功能仿真(RTL仿真)、在线调试等两方面。

在一般情况下我们往往只需要编写测试文件进行功能仿真就行,这样就能解决大多数问题。但这是在项目功能少,结构简单的方面。如果在大的项目或者结构复杂的设计中,如果要进行功能仿真,在编写测试文件时往往需要编写大量的测试数据才能进行我们相应功能的验证。在这个时候我们就可以采取在线调试的方式进行波形的抓取,这相对于功能仿真来说,就省去了编写测试代码的时间,减少我们的工作量。

这篇文章我们就来说一下Signal Tap 的简单使用!

二、Signal Tap的介绍

1、什么是 SignalTap II?

SignalTap II 是第二代系统级调试工具(类似: 逻辑分析仪), 可以捕获和显示实时信号, 是一款功能强大的 FPGA 片上调试软件、 捕获的触发方式以及捕获的数据样本深度, 并将数据实时提供给工程师协助 debug。

传统的 FPGA 板级调试是由外接的逻辑分析仪连接到 FPGA 的控制管脚, 然后再将内部信号引出至引脚 IO 上, 进行板级调试。 (缺陷: 1.需要逻辑分析仪、 2.需要修改代码、 3.引脚多外接时比较麻烦)。

2、功能

SignalTap II 借用了传统逻辑分析仪的理念以及大部分的功能, 使用 SignalTap lI 无需额外的逻辑分析设备, 只需将一根JTAG 接口的下载电缆连接到要调试的 FPGA 器件, 数据通过JTAG 接口从 FPGA 传送到 Quartus II 软件中显示。

3、局限

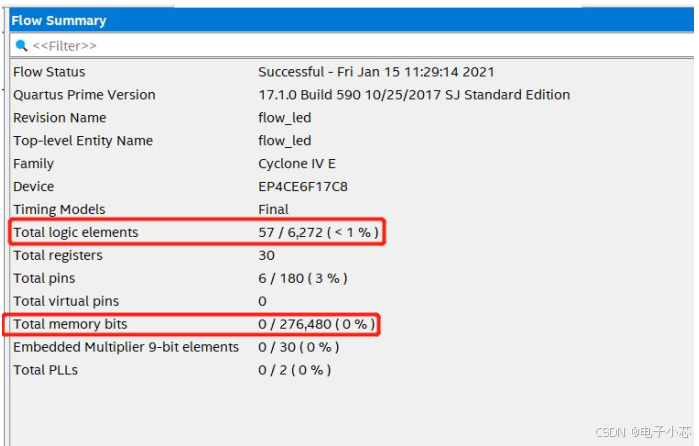

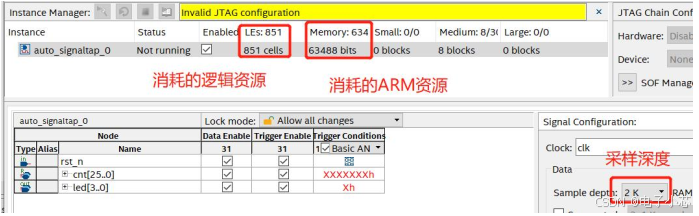

SignalTap Il 在工程中额外加入了模块来采集信号, 所以使用 SignalTap II 需要消耗 FPGA 的逻辑资源和 RAM 资源, 如果工程中剩余的 RAM 资源比较充足, 那么 SignalTap ll 一次可以采集较多的数据;反之, 如果 FPGA 资源已被工程耗尽则无法使用SignalTap Il 调试。

三、Signal Tap 的使用

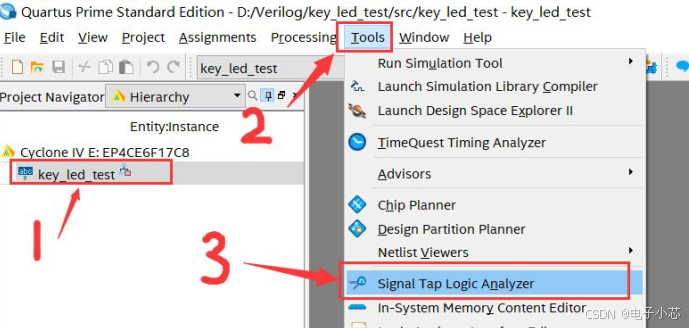

1、打开 SignalTap 工具界面

这里我们需要打开一个建立好的工程,才能进行操作,如图所示,我们Quartus 里面已经打开了一个key_led_test的工程,然后就是点击Tools选项里面的Signal Tap Logic Analyzer:

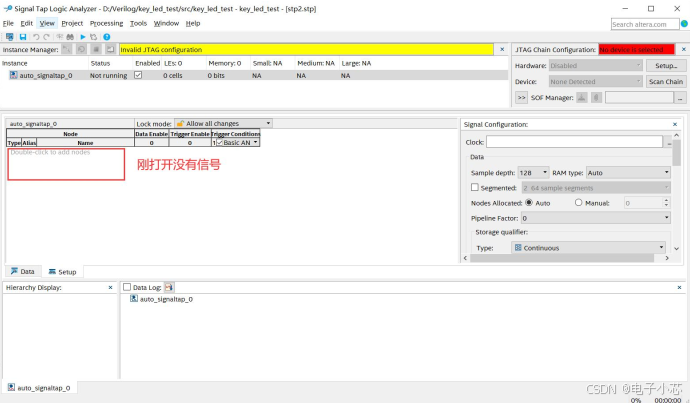

2、SignalTap 工具界面

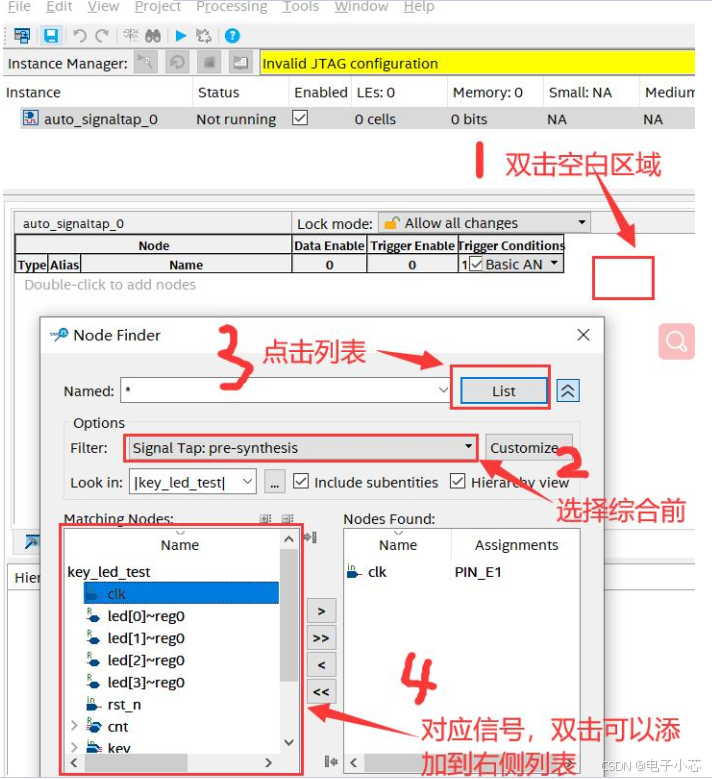

3、双击信号空白区域, 打开信号列表

这里除了双击的方式也可以使用右键,找到Add Nodes...的方式打开信号列表。

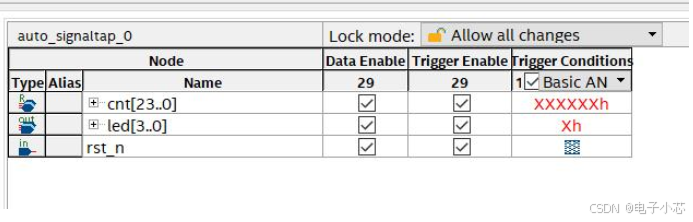

4、添加好后的结果

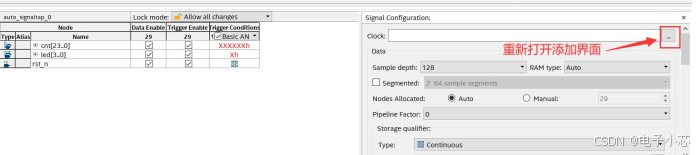

5、重新打开添加界面

6、添加采样时钟(注: 不一定是系统时钟)

7、设置采样深度

采样的值设置越大则观看的点数越多, 同样占用的资源越多

8、电脑连接开发板, 打开开发板

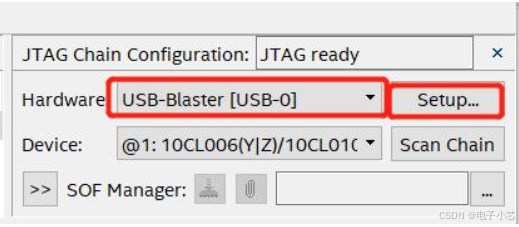

9、SignalTap II 界面右上角选 Hardware: usb-blaster

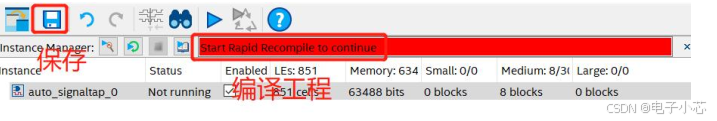

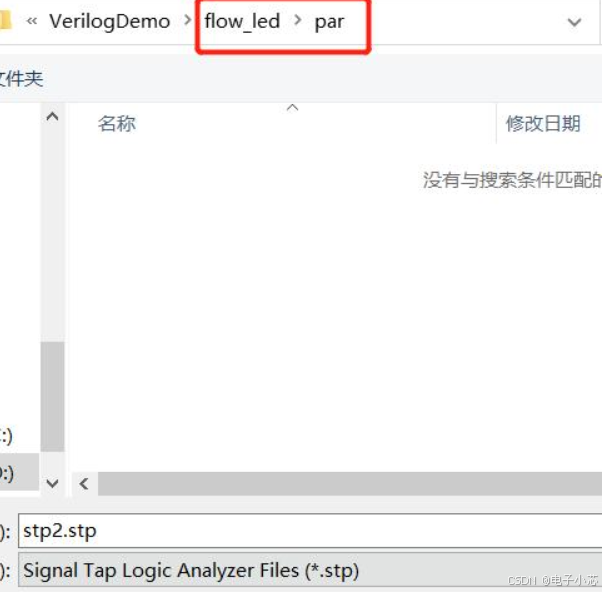

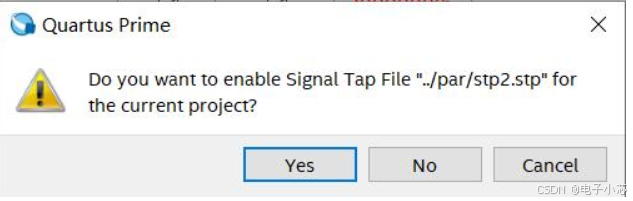

10、编译工程(注: 先保存文件到项目 par 文件夹)

是否将 stp2.stp 文件添加至工程

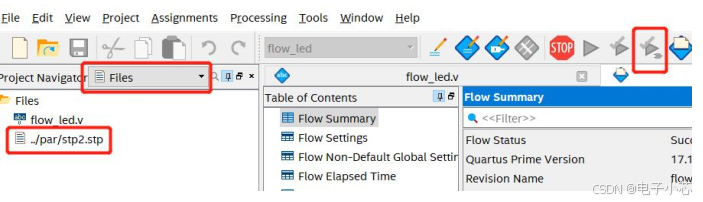

11、切换视图, 编辑工程

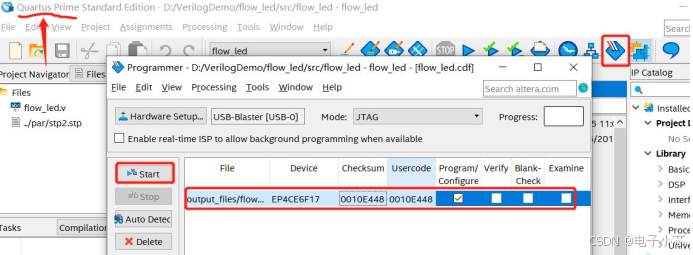

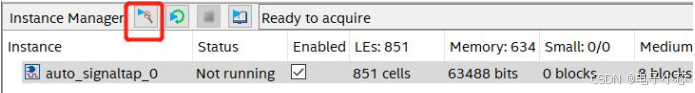

12、编译完后, 程序下载到开发板

第一步:

第二步:

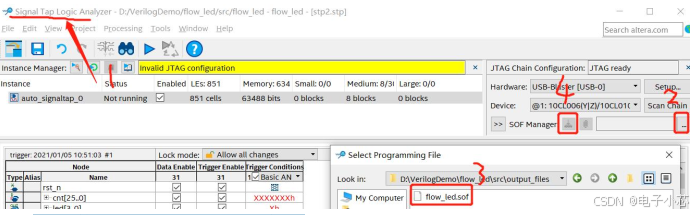

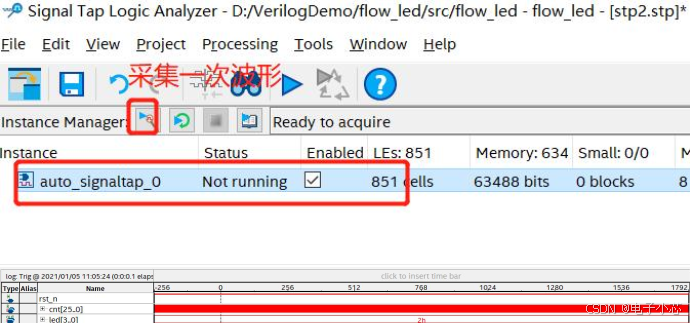

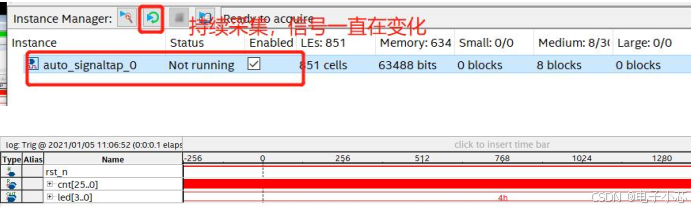

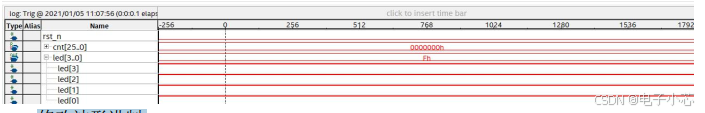

13、使用 SignalTap II 调试代码

按下复位按键:

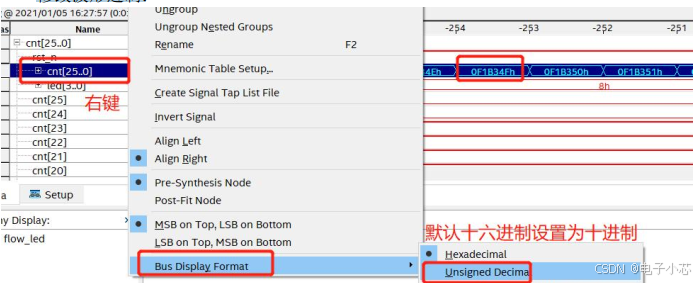

修改波形进制:

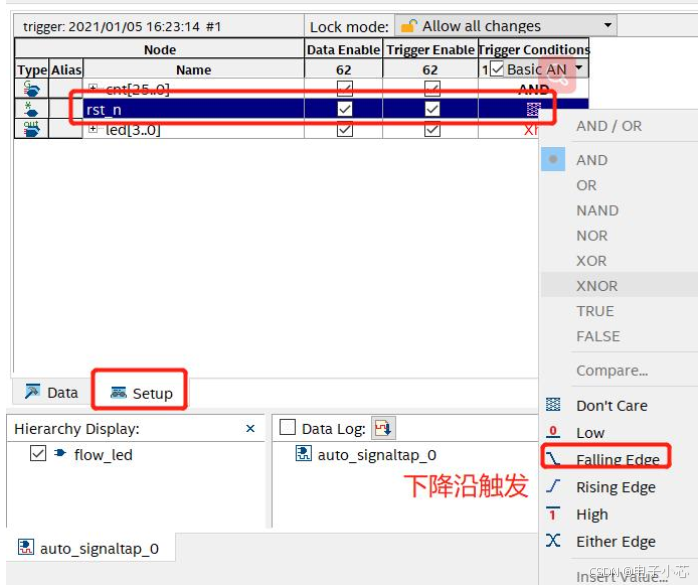

14、使用 SignalTap II 通过触发的方式查看波形

复位按键通过下降沿触发:

按下复位按键后波形图:

15、使用 SignalTap II 通过触发的方式查看波形(续)

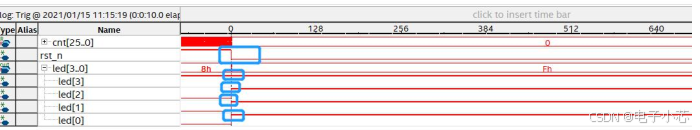

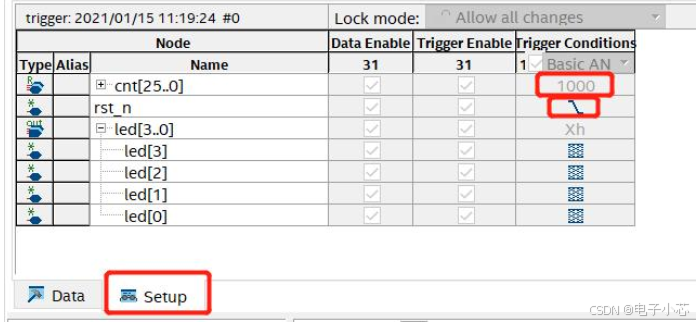

设置 cnt 为 1000, 并且复位下降沿时触发

按了复位按键后一直无法采集到波形, 因为条件很难同时满足

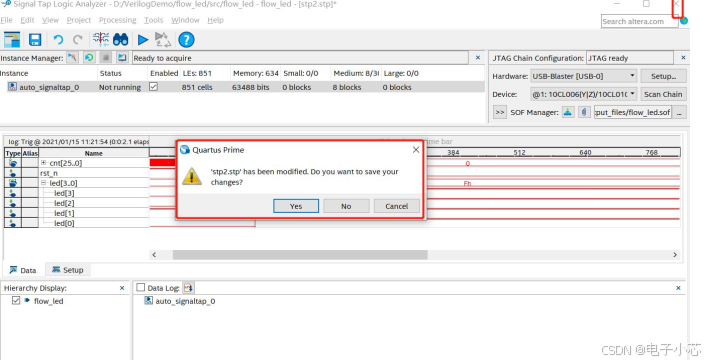

16、关闭 SignalTap II 界面

提示: 采集的信号波形发生改变是否需要保存

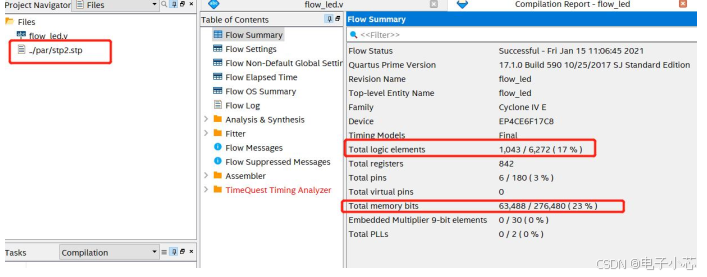

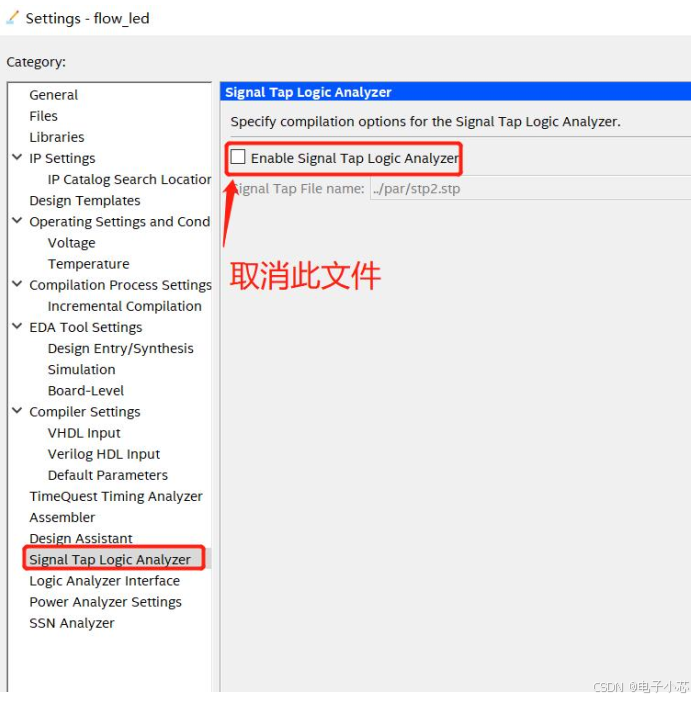

17、从工程中删除 SignalTap 文件

原因: 调试结束后发现添加 SignalTap 消耗资源比较多, 调试结束后并不需要此文件, 需要从工程中删除 SignalTap 文件

在Settings 界面取消调试文件。

18、重新编译工程

通过重新编译之后我们可以看到资源使用情况回归到没使用Signal Tap进行抓取状态之前的资源使用量。