- Virtex UltraScale+系列 FPGA处理器:XCVU13P-2FHGB2104I

- 动态存储数量:2组DDR4 SDRAM

- 动态存储容量:每组4GByte,每个颗粒为8GBit

- 动态存储带宽:工作时钟1000MHz,数据率2000Mbps

- 板载6路QSFP+光纤接口

- 板载4个FMC+高速扩展接口

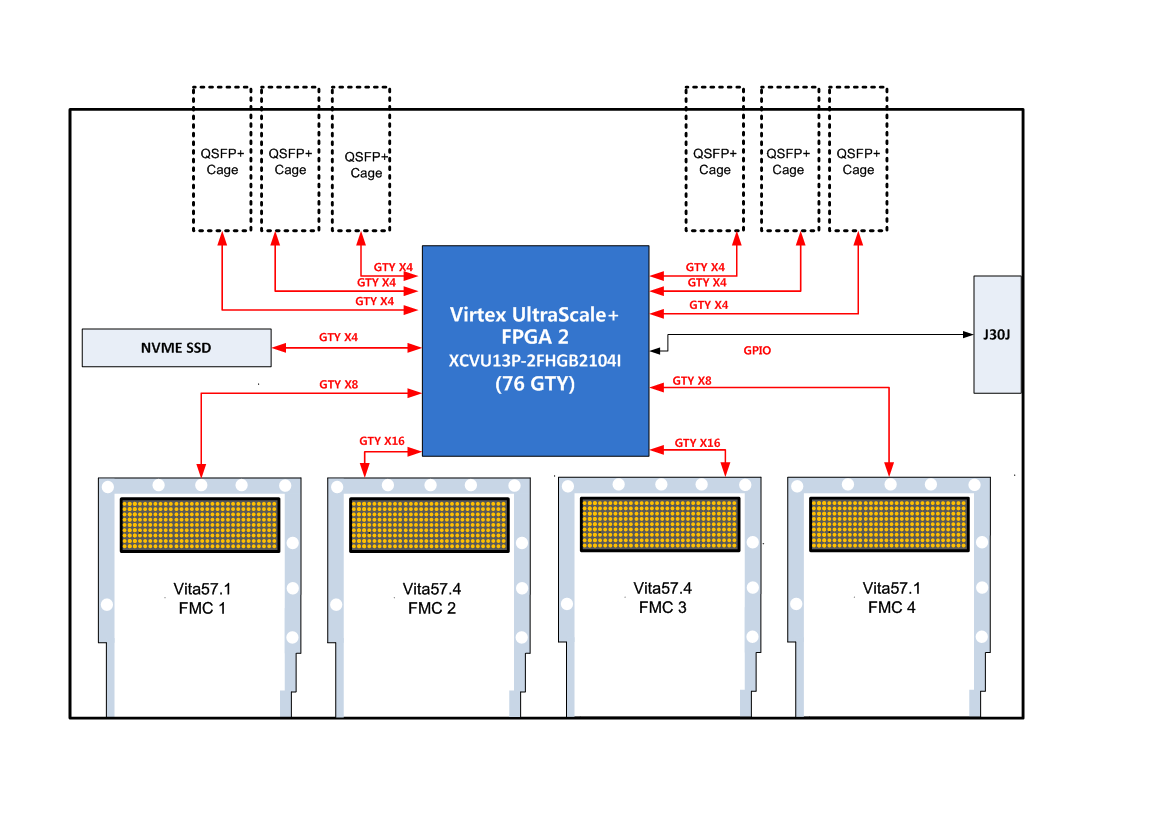

基于Virtex UltraScale+系列FPGA的高性能4路FMC接口基带信号处理平台,该平台采用1片Xilinx的Virtex UltraScale+系列FPGA XCVU13P作为信号实时处理单元,该板卡具有4个FMC子卡接口(其中有2个为FMC+接口),各个节点之间通过高速串行总线进行互联,该FPGA支持最大32Gbps的高速串行总线,适用于100G以太网、JESD204B/JESD204C等高速接口。板卡采用嵌入式非标结构,具有优良的抗振动设计、散热性能和独特的环境防护设计,适用于超带宽基带信号处理、多路AD/DA等同步采集处理等场景。

功能框图

技术指标

- FPGA + 多核DSP协同处理架构;

- 1 个多核 DSP 处理节点、1 个 Kintex-7 FPGA 处理节点;

- 处理性能:

- DSP 定点运算:40GMAC/Core*8=320GMAC;

- DSP 浮点运算:20GFLOPs/Core*8=160GFLOPs;

- 存储性能:

- DSP 处理节点:4GByte DDR3-1333 SDRAM;

- DSP 处理节点:4GByte Nand Flash;

- FPGA 处理节点:1 组 2GByte DDR3-1600 SDRAM;

- 互联性能:

- DSP 与 FPGA:SRIO x4@5Gbps/lane;

- FPGA 与 FMC 接口:2 路 GTH x4@10Gbps/lane;

- 物理与电气特征

- 板卡尺寸:171 x 204mm

- 板卡供电:3A max@+12V(±5%)

- 散热方式:金属导冷散热

- 环境特征

- 工作温度:-40°~﹢85°C,存储温度:-55°~﹢125°C;

- 工作湿度:5%~95%,非凝结

应用领域

- 软件无线电;

- 雷达与基带信号处理;

- 高速图像图形处理;