异步复位同步释放

描述

题目描述:

请使用异步复位同步释放来将输入数据a存储到寄存器 中,并++画图说明异步复位同步释放的机制原理++

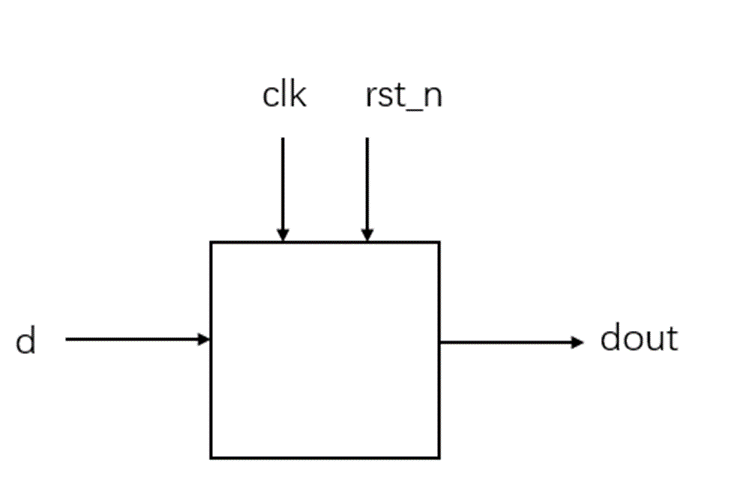

信号示意图:

clk为时钟

rst_n为低电平复位

d信号输入

dout信号输出

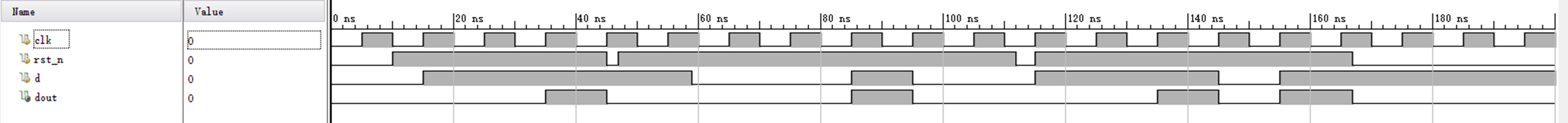

波形示意图:

输入描述:

clk为时钟

rst_n为低电平复位

d信号输入

输出描述:

dout信号输出

解题思路

主要参考以下博文

了解复位的概念

电路的任何一个**寄存器、存储器结构和其他时序单元都必须++附加复位逻辑电路++,以保证电路能够从错误状态中恢复、可靠地工作。**对于综合实现的真实电路,通过复位使电路进入初始状态或者其他预知状态。

同步复位

下面给出一个简单的同步复位的D触发器,Verilog代码如下:

cpp

module Sync_rst(

input clk,

input rst, //Synchronous reset

input d,

output reg q

);

always @(posedge clk) begin

if (!rst) q <= 1'b0;

else q <= d;

end

endmodule其RTL视图如下所示:

同步复位的优点:

- 抗干扰性高,可以剔除复位信号中周期短于时钟周期的毛刺;

- 电路稳定性强。

同步复位的缺点:

- 大多数逻辑器件的目标库内的DFF都只有异步复位端口,将其用于同步复位时,综合器就会在寄存器的数据输入端插入额外的组合逻辑,占用更多的逻辑资源;

- 同步复位依赖于时钟,如果电路中的时钟信号出现问题,则无法完成复位。

- 对复位信号的脉冲宽度有要求,必须大于指定的时钟周期,由于线路上的延迟,可能需要多个时钟周期的复位脉冲宽度,且很难保证复位信号到达各个寄存器的时序;

异步复位

一个简单的异步复位的D触发器,Verilog代码如下:

cpp

module Async_rst(

input clk,

input rst_n,

input d,

output reg q

);

always@(posedge clk or negedge rst_n) begin

if(!rst_n) q<= 1'b0;

else q <= d;

end

endmodule其RTL视图如下所示:

异步复位的优点:

- 无需额外的逻辑资源,实现简单;

- 复位信号不依赖于时钟。

异步复位的缺点:

- 复位信号容易受到外界的干扰,如毛刺等影响;

- 复位信号释放的随机性,可能导致时序违规,倘若复位释放时恰恰在时钟有效沿附近,就很容易使电路处于亚稳态;

异步复位同步释放

异步复位 :复位信号可以直接不受时钟信号影响,在任意时刻只要是低电平就能复位,即复位信号不需要和时钟同步;如上图所示,当rst_n有效时(即rst_n = 1'b0 时),第一级D触发器和第二级D触发器的输出rst_0、rst_1均为低电平(即rst_0=1'b0、rst_1'b0 );此时,以rst_1作为复位信号的第三个D触发器的复位信号有效,其输出dout被复位,即dout = 1'b0;该过程被称为异步复位;

同步释放 :让复位信号取消的时候,必须跟时钟信号同步,即刚好跟****时钟同沿;在上图中,假设rst_n撤除(即rst_n = 1'b1)时发生在clk上升沿,如果不加该电路(异步复位同步释放电路)可能会发生亚稳态事件(有的时候会打三拍)。但是加上此电路后,假设第一级D触发器在clk_上升沿时rst_n刚好撤除(即rst_n = 1'b1) ,则第一级D触发器可能输出高电平"1",也可能输出亚稳态,也可能输出低电平。但此时第二级触发器不会立刻更新输出,第二级触发器输出值为前一级触发器的输出状态rst_0。显然++第一级触发器之前为低电平++ ,故第二级触发器输出保持复位(rst_2 = 1'b0).直到下一个时钟有效沿到来之后,才随着变为高电平(rst_2 = 1'b1)。即实现同步释放;

其Verilog代码如下(题解Verilog代码):

cpp

`timescale 1ns/1ns

module ali16(

input clk,

input rst_n,

input d,

output reg dout

);

//*************code***********//

reg rst_0, rst_1;

//异步复位同步释放

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin rst_0 <= 1'b0; rst_1 <= 1'b0; end

else begin rst_0 <= 1'b1; rst_1 <= rst_0;end

end

//将输入数据存储到寄存器中

always @(posedge clk or negedge rst_1) begin

if (!rst_1) dout <= 1'b0;

else dout <= d;

end

//*************code***********//

endmodule异步复位同步释放的波形图如下所示:

异步复位同步释放的优点

- 避免复位信号释放的时候造成的亚稳态问题

- 只要复位信号一有效,电路就处于复位状态,以时钟沿无关

- 有效捕捉复位,即使是短脉冲复位也不会丢失

- 有明确的复位撤销行为,复位的撤离是同步信号,因此有良好的撤离时序和足够的恢复时间

- 用两级触发器打两拍的方法解决亚稳态的问题;