以下是关于正点原子B站课程中 i.MX6ULL主频和时钟配置实验的博客内容框架与详细解析,结合实验原理、配置流程及关键代码实现,适合嵌入式开发者参考学习:

一、 实验背景

i.MX6ULL默认启动时由内部BootROM将主频设置为396MHz,但其标准工作频率为528MHz,部分型号可超频至696MHz。通过配置系统时钟与外围时钟,可最大化芯片性能并满足不同外设需求。本实验目标是通过编程调整主频至528MHz。

二、 硬件原理

1. 时钟源与PLL结构

i.MX6ULL的时钟系统由两路外部晶振驱动:

24MHz晶振:内核及外设主时钟源。

32.768kHz晶振:RTC专用。

芯片内部通过7路PLL(锁相环)生成高频时钟:

-

ARM_PLL (PLL1):专供ARM内核,可编程倍频至最高1.3GHz。

-

528_PLL (PLL2):固定22倍频(24MHz×22=528MHz),生成系统总线时钟。

-

USB1_PLL (PLL3):固定20倍频(480MHz),提供USB及外设时钟。

-

其他PLL:如ENET_PLL(500MHz)、VIDEO_PLL(650-1300MHz)等。

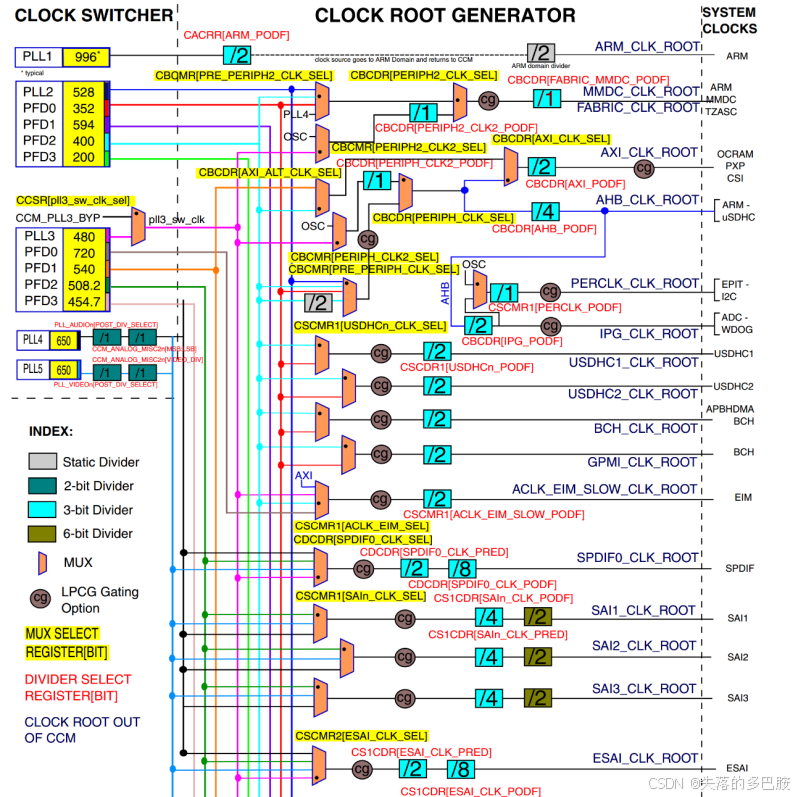

部分时钟树展示

2. 主频配置流程

根据博主个人的理解,在配置主频的编程中,本质上就是根据图中相应的多路选择器配置相应的寄存器,进而控制多路选择器进行选择。

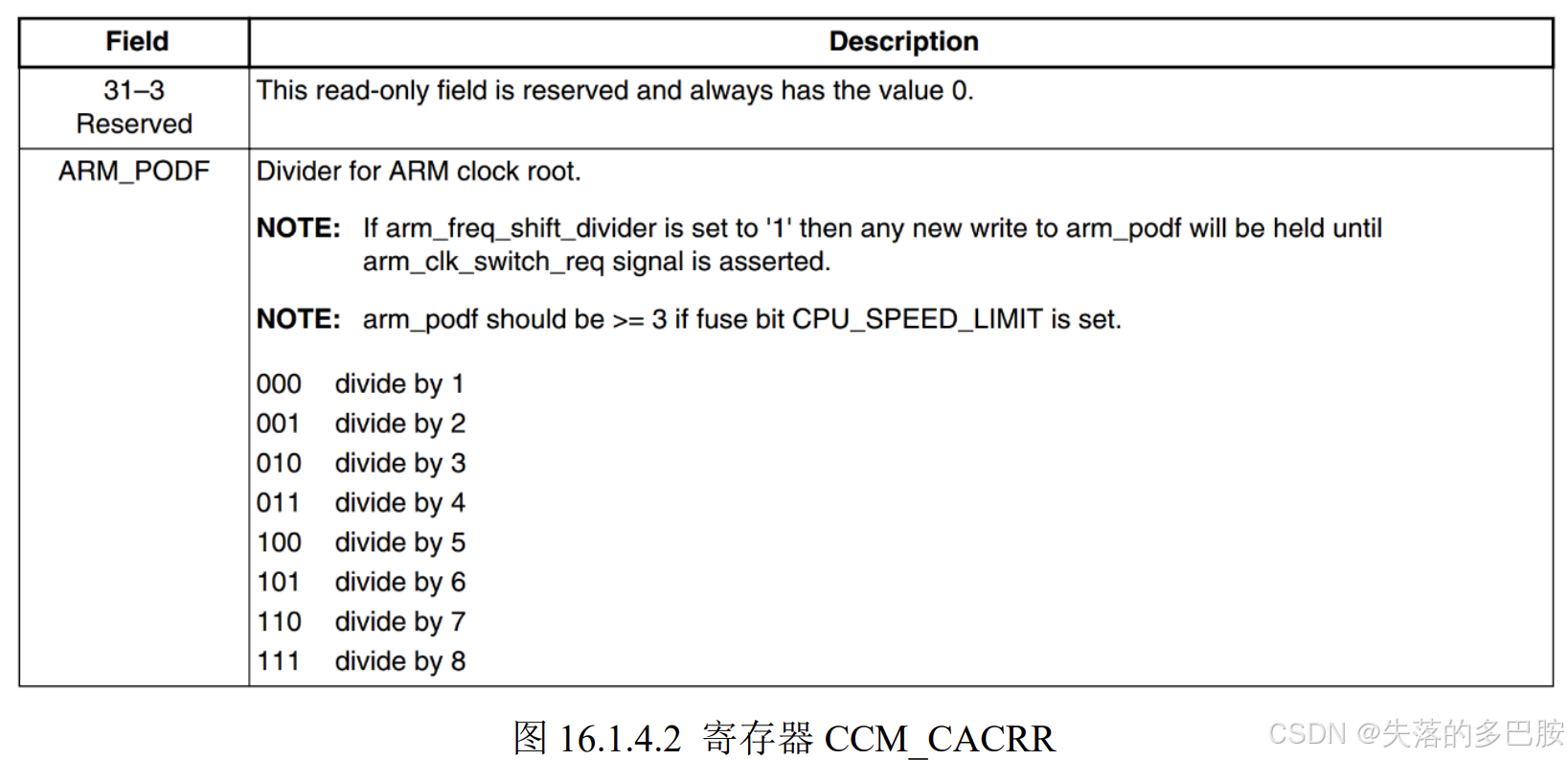

- 要设置ARM内核主频为528MHz,设置CACRR寄存器的ARM_PODF位为2分频,

然后设置PLL1=1056MHz即可。CACRR的bit3~0为ARM_PODF位,可设置0~7,分别对

应1~8分频。如果要设置为2分频的话,CCM_CACRR就要设置为1。再来看一下寄存器CCM_ANALOG_PLL_ARMn, 此寄存器结构如图 16.1.4.3 所示:

在寄存器 CCM_ANALOG_PLL_ARMn 中重要的位如下:

ENABLE: 时钟输出使能位,此位设置为 1 使能 PLL1 输出,如果设置为 0 的话就关闭 PLL1 输出。

DIV_SELECT : 此位设置 PLL1 的输出频率,可设置范围为:54~108,PLL1_CLK = Fin * div_seclec/2.0,Fin=24MHz。如果 PLL1 要输出 1056MHz 的话,div_select 就要设置为 88。

分频设置:如下图

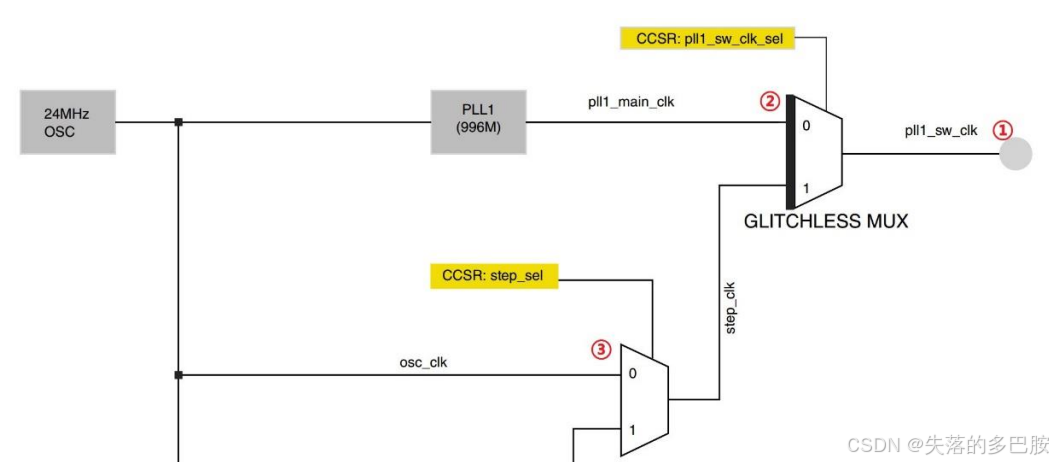

- 设置 PLL1=1056MHz。PLL1=pll1_sw_clk。pll1_sw_clk有两路可以选择,分别为

pll1_main_clk,和step_clk,通过CCSR寄存器的pll1_sw_clk_sel位(bit2)来选择。为0的时候

选择pll1_main_clk,为1的时候选择step_clk。

- 切换临时时钟源

修改主频需先切换至临时时钟step_clk,步骤如下:

-

设置step_clk时钟源为24MHz晶振。如图,(通过CCSR寄存器的step_sel进行选择)。

-

切换pll1_sw_clk到step_clk,确保修改PLL1时系统仍有时钟运行。

为什么要切换到临时时钟呢?打个比方,我们在为病人做心脏手术时取出病人原有的心脏(pll1_main_clk)进行修复,就需要使用一个人造的心脏(即临时时钟step_clk)临时使用,维持病人生命体征,否则病人就无了,这里也是同样的道理。

所以保险起见,在开始之前我们进行判断,判断是否需要切换时钟。

if (((CCM->CCSR >> 2) & 0x1) == 0) { // 判断当前是否使用PLL1

CCM->CCSR &= ~(1 << 8); // step_clk选择24MHz晶振

CCM->CCSR |= (1 << 2); // pll1_sw_clk切换至step_clk

}- 配置PLL1频率

通过CCM_ANALOG_PLL_ARM寄存器设置PLL1倍频参数:

公式:PLL1输出频率 = 24MHz × DIV_SELECT / 2

我们配置的目标为528MHz:需设置DIV_SELECT=88(1056MHz),再通过2分频得到528MHz。

CCM->ANALOG->PLL_ARM = (1 << 13) | ((88 << 0) & 0X7F)

CCM->CACRR = 1; //设置分频系数为2-

切换回PLL1时钟源

CCM->CCSR &= ~(1 << 2); // pll1_sw_clk切换回PLL1_main_clk

所以,最终整个初始化的函数如下

/*初始化时钟*/

void imx6u_clkinit(void)

{

/*初始化6U的主频为528Mhz*/

if(((CCM->CCSR >> 2) & 0X1) == 0)//当前时钟使用pll1_main_clk,需要切换时钟

{

CCM->CCSR &= ~(1 << 8); //设置step_clk = osc_clk = 24M

CCM->CCSR &= ~(1 << 2); //设置pll1_sw_clk = step_clk = 24M

}

/* 设置PLL1 = 1056M */

CCM->ANALOG->PLL_ARM = (1 << 13) | ((88 << 0) & 0X7F)

CCM->CACRR = 1; //设置分频系数为2

CCM->CCSR &= ~(1 << 2); //设置pll1_sw_clk = pll1 = 1056M

}三、实验注意事项

-

时钟切换顺序:需先切换到临时时钟再修改PLL,避免系统崩溃。

-

分频参数范围:PFD分频值需在12~35之间。

-

注意频率范围:PLL1最高频率为1.3GHz,我们假设要设置的不是528M而是792MHz,采用二分频计算公式发现求得的结果明显超过最大频率1.3G的上限,这时就应采用1分频方式,设置792MHz。

参考资源:

i.MX6ULL参考手册第10章、第18章](https://www.nxp.com)

B站正点原子