1,

使用modelsim仿真DDR3报错Module 'SIP_PHY_CONTROL' is not defined

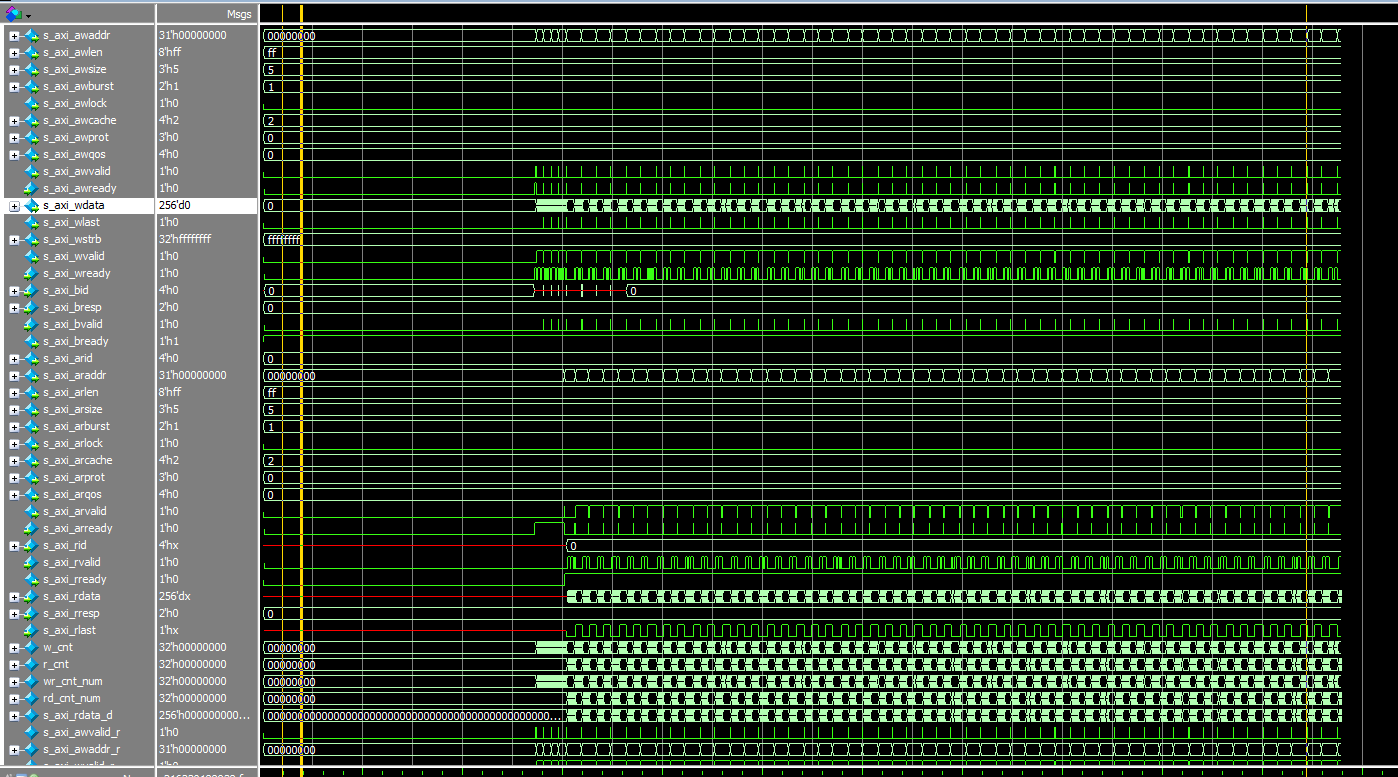

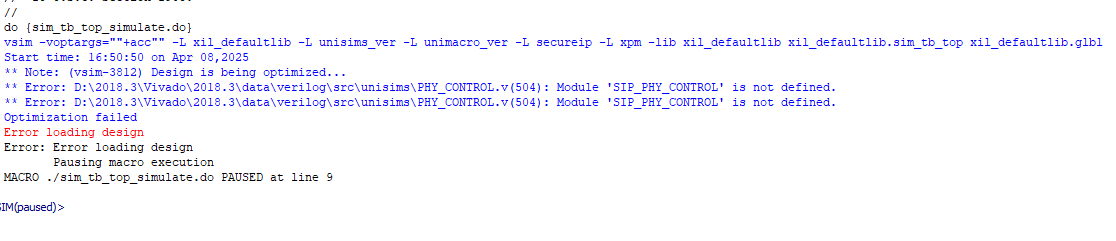

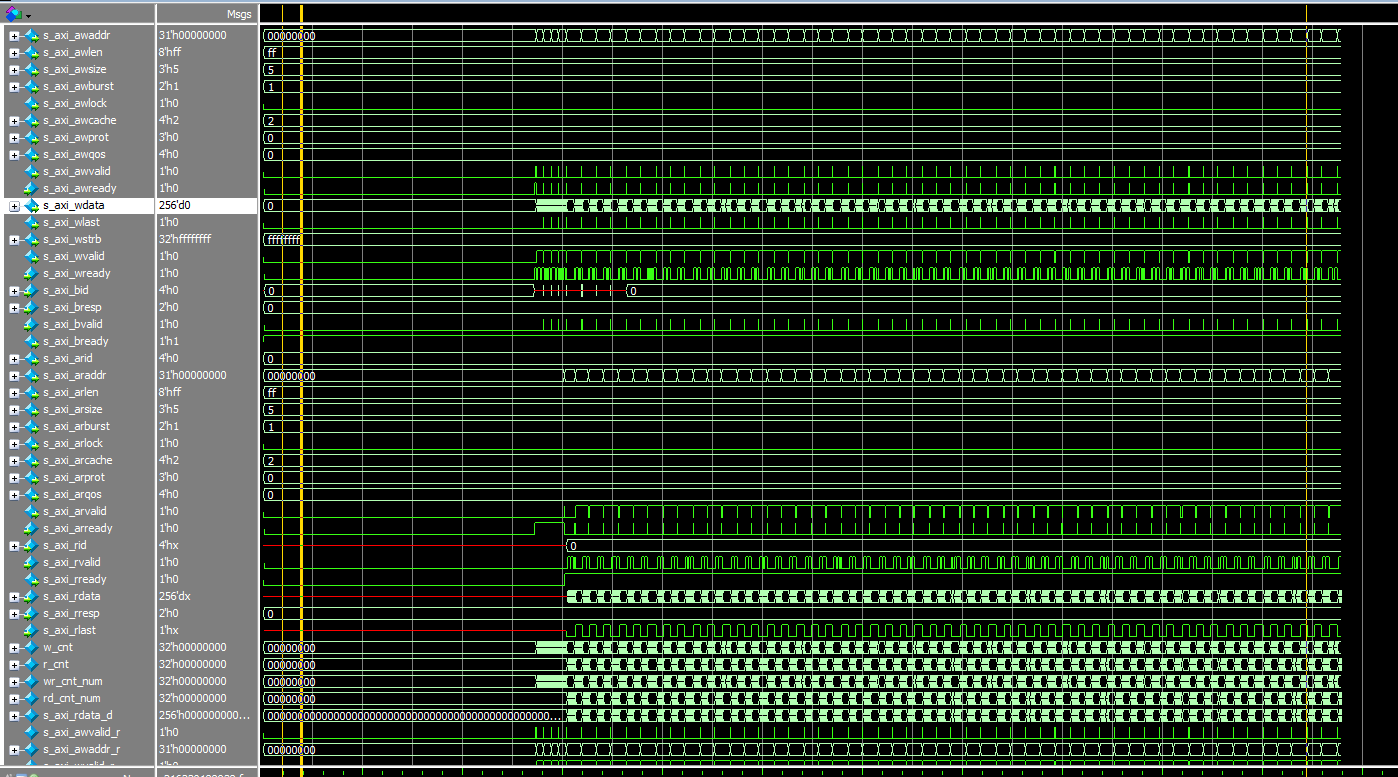

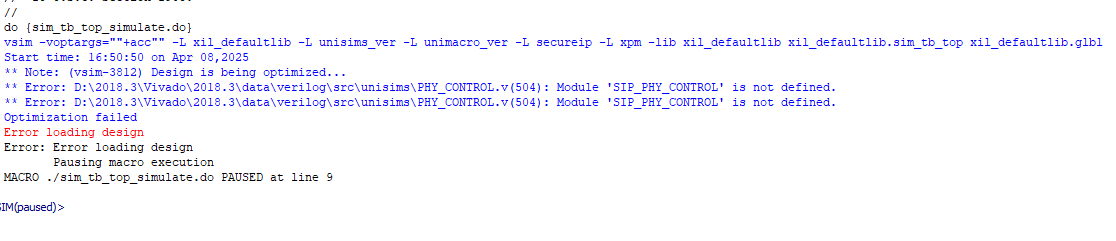

在配置ddr3的时候vivado 速度太慢了,所以选用modelsim。我的是2018.3vivado,modelsim用了10.4 但是不行报错

然后看了帖子说 questasim可以下载了还是报错。

然后又试了 2019.2

解决报错

1,

使用modelsim仿真DDR3报错Module 'SIP_PHY_CONTROL' is not defined

在配置ddr3的时候vivado 速度太慢了,所以选用modelsim。我的是2018.3vivado,modelsim用了10.4 但是不行报错

然后看了帖子说 questasim可以下载了还是报错。

然后又试了 2019.2

解决报错