目录

[2.1 逻辑独立时钟](#2.1 逻辑独立时钟)

[2.2 物理独立时钟](#2.2 物理独立时钟)

专栏目录:

FPGA时序分析与约束(0)------目录与传送门![]() https://ztzhang.blog.csdn.net/article/details/134893857

https://ztzhang.blog.csdn.net/article/details/134893857

一、同步时钟与异步时钟

在一个复杂系统的设计中,通常包含有多个时钟。这个时候,我们在进行时序分析的时候,不仅需要关注时钟频率,还需要关注不同时钟之间的关联关系。

- 同步时钟指的是一种共享确定相位关系的时候,通常同步时钟是同源的。例如基准时钟 clk_100m → 分频得到 clk_50m(同步关系)。

- 异步时钟则不共享固定的相位关系,通常来说,他们不是来源于同一个主时钟或者没有相同的周期。例如:来自独立的晶振、时钟发生器或FPGA不同全局时钟网络(如 clk_a 来自外部晶振,clk_b 来自另一个板载时钟源)。

如果不进行正确的时钟组区分,时序工具(如Vivado)默认会检查所有时钟之间的路径。如果两个时钟实际是异步的(如来自不同晶振),但未声明为异步组,工具会强制分析它们的时序关系(例如建立时间/保持时间)。由于异步时钟的相位关系随机,这种分析毫无意义,且会生成大量虚假违例,干扰真正的时序问题定位。例如:时钟A(100MHz)和时钟B(25MHz)来自不同的晶振。若未声明异步,工具会尝试分析A的上升沿与B的上升沿所有可能的对齐方式,导致无法满足的时序要求。

此外,异步时钟路径的检查会增加工具的运行时间和内存占用。显式声明异步组后,工具会跳过这些路径的分析,提升编译效率。而且异步时钟组的声明是CDC设计的第一步。它提示设计者必须对跨时钟域信号采用同步措施(如两级触发器、FIFO等),否则工具可能忽略潜在的亚稳态风险。

二、逻辑与物理独立时钟

在数字电路设计中,逻辑独立时钟(Logically Exclusive Clocks) 和**物理独立时钟(Physically Independent Clocks)**是两个关键概念,直接影响时序约束和功能可靠性。

2.1 逻辑独立时钟

逻辑独立时钟通常指的是多个时钟在逻辑上不会同时激活 (例如通过多路复用器选择,同一时刻仅有一个时钟有效)。硬件行为 :时钟的切换通常由控制信号(如 sel)决定,且切换时可能有保护电路(如握手协议)。如下图中的C1和C2,就是一组逻辑独立时钟。

2.2 物理独立时钟

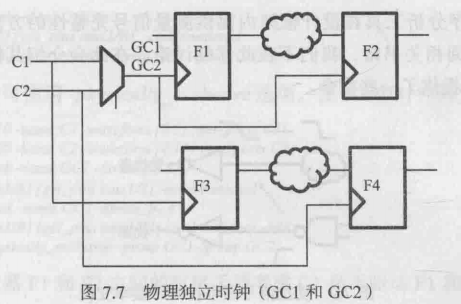

如下图所示,由于C1,C2是逻辑独立的,因此两个生成时钟GC1和GC2也是独立的,但是它们不会存在于同一个网络下,因此,GC1和GC2被认为是物理独立的。

三、如何设置时钟组

为了能让时序工具正确识别异步时钟,我们可以采用set_clock_groups命令。该命令的BNF为:

set_clock_groups

[-name group_name]

[-group clock_list]

[-logically_exclusive]

[-physically_exclusive]

[-asynchronous]

[-allow_paths]

[-comment string]互斥性声明(必须选其一):

-asynchronous:声明组内时钟为异步关系(最常见,用于不同源时钟)。

-physically_exclusive:时钟在物理上不可能同时存在(如动态切换的时钟)。

-logically_exclusive:时钟在逻辑上不会同时激活(如多路复用时钟)。

可选参数:

-name:为时钟组命名(用于调试和报告)。

-group:指定属于同一组的时钟列表(可多次使用,每组时钟与其他组异步)。

-comment:添加注释(如注明时钟来源)。

-quiet/-verbose:控制命令执行时的输出信息级别。

四、注意事项

在设定时钟组时,设计者必须注意以下几点:

尽管你可能定义了一个时钟组,但这并不意味着它们就是同步的。组内时钟之间的关系可另外定义(可利用set_clock_group指令或者工具默认的设置)。

使用错误的选项(-physically_exclusive、-logically_exclusive、-asynchronous)定义时钟组可能不会影响时序,因为所有受影响的时序电路路径都被忽略了,但这会影响信号完整性分析。

即便定义了主时钟和其他时钟之间的时钟组关系,这种关系也不会被主时钟派生出的生成时钟所继承。所有的关系都应当明确地设定。

记住时钟分组最好的办法是:

a)如果设计中共存多个时钟,却没有相位关系,则应在set_clock_group中设定-asynchronous.

b)如果设计中共存多个时钟,并且电路仅选择其中一个,则应在set_clock_group中设定-logically_exclusive.

c)如果设计中不能共存多个时钟,则应在set_clock_group中设定-physically_exclusive。