DW的IP要被vivado等综合还是很麻烦的,而是用synplify等综合工具,然后再嫁接到vivado中也非常麻烦。本文提供一种解决办法。

- 对DW的IP进行gtech综合。即使用DC工具对DW IP进行综合。而使用的综合库是gtech。脚本如下:

bash

set target_library "gtech.db"

set synthetic_library "dw_foundation.sldb"

set link_library " * $target_library $synthetic_library "

analyze -format sverilog -vcs "-sverilog -f ***" > analyze.log

elaborate *_module > elaborate.log

current_design xxx

link

compile

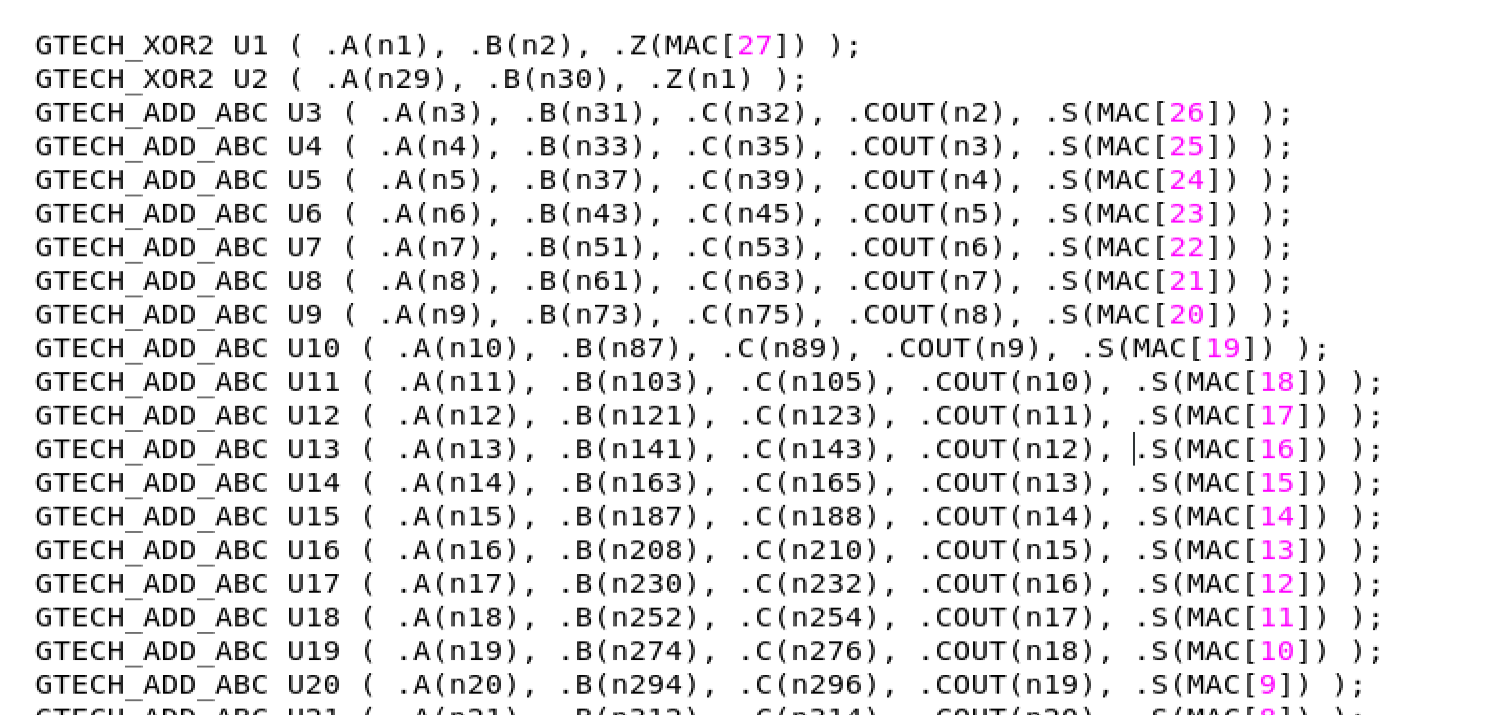

write_file -f verilog -hier -o design_gtech_netlist.v生成完的design_gtech_netlist.v为一堆使用gtech的网表:

- 编写一个gtech.v,对上述网表中的每一个门电路都进行描述,例如:

bash

module GTECH_ADD_ABC(A,B,C,S,COUT);

input A,B,C;

output S,COUT;

assign S=A^B^C;

assign COUT=A&B|A&C|B&C;

endmodule由于gtech的种类不是很多,所以一开始描述会麻烦点。但随着时间的推移。很快就会形成一个完整gtech.v的库。

-

然后将design_gtech_netlist.v和gtech.v一同引用至vivado中,即可完成综合。

-

对于参数化IP,可以根据不同参数分别gtech综合。然后在实际引用IP的代码中,用下面的方式进行fpga和流片版本的区分:

bash

`ifdef FPGA_SIM

DW02_mac_12x12

`else

DW02_mac #(A_BW, B_BW)

`endif

u_mac (.A(a), .B(b), .C(c), .TC(1'b1), .MAC(mac) );DW02_mac_12x12是gtech综合后的版本。