一、几个注意点

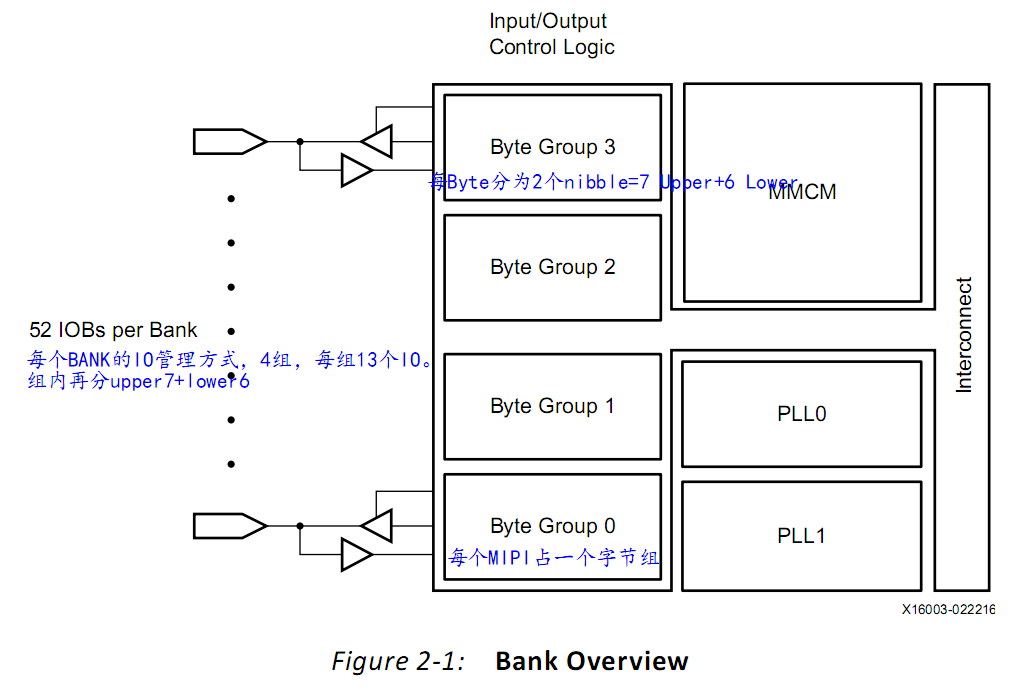

1、每个bank中IO的组织形式

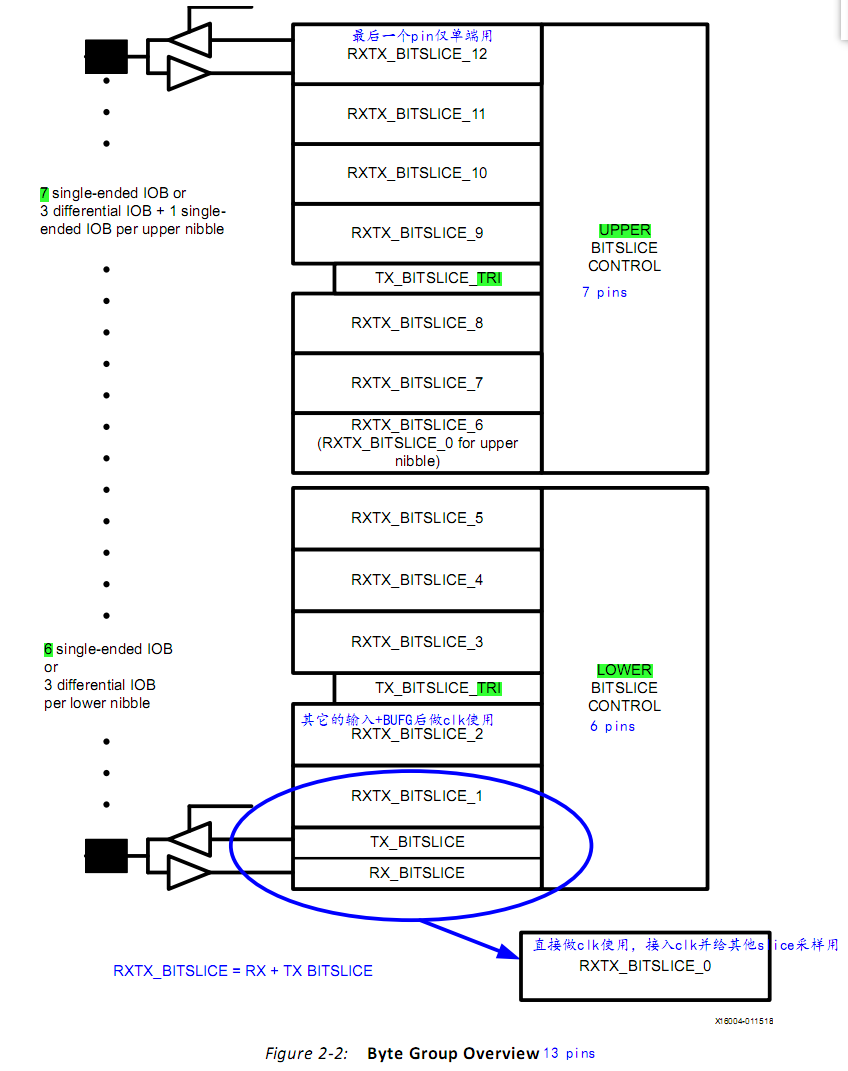

1Bank的52Pins分4 Byte Group,每Byte Group 13Pins=Nibble_up 7Pins + Nibble_low 6Pins。

每个nibble一个bitslice_control管理自己的6~7个pins 。

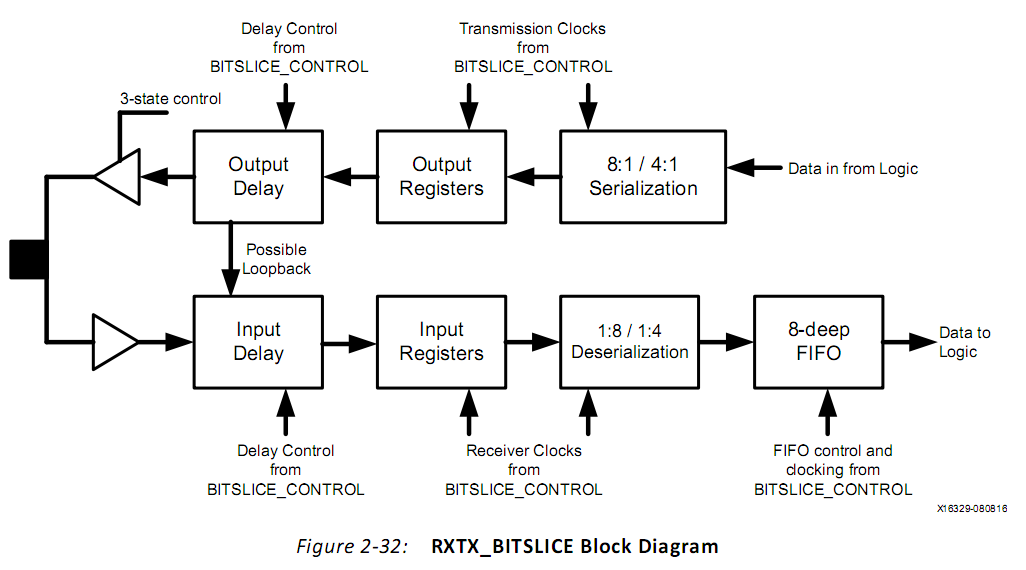

每个pin对应一个bitslice,它内部又包含多个component,如IOSerdes,IODelay等。可以单独作为组件使用调用Component Primitives;也可整体使用调bitslice原语称为native mode;也可以个两个混合使用Mixing Native and Non-Native Mode,此时的控制只能使用bitslice_control,不能使用idelayctrl。参考 《ug571-ultrascale-selectio》Native Primitives章节。

2、idelayctrl的使用

一个bank中的所有IOdelay用共用一个idelayctrl,可以使用约束IDELAY_GROUP约束为一组。

有多个bank用iodelay时,可以在顶层文件中定义一个idelayctrl,vivado软件自动为各bank复制一份。也可以为每个bank定义一个并约束分组,用不同的组名区分。

set_property IODELAY_GROUP group_name [get_cells IDELAYCTRL_inst]

set_property IODELAY_GROUP group_name [get_cells IDELAY_inst]

set_property IODELAY_GROUP group_name [get_cells ODELAY_inst]

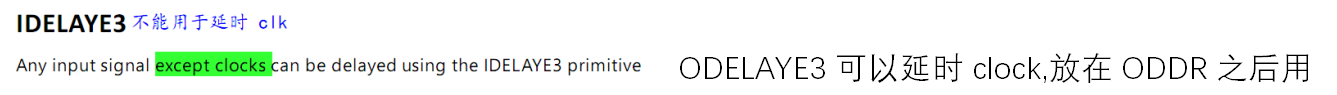

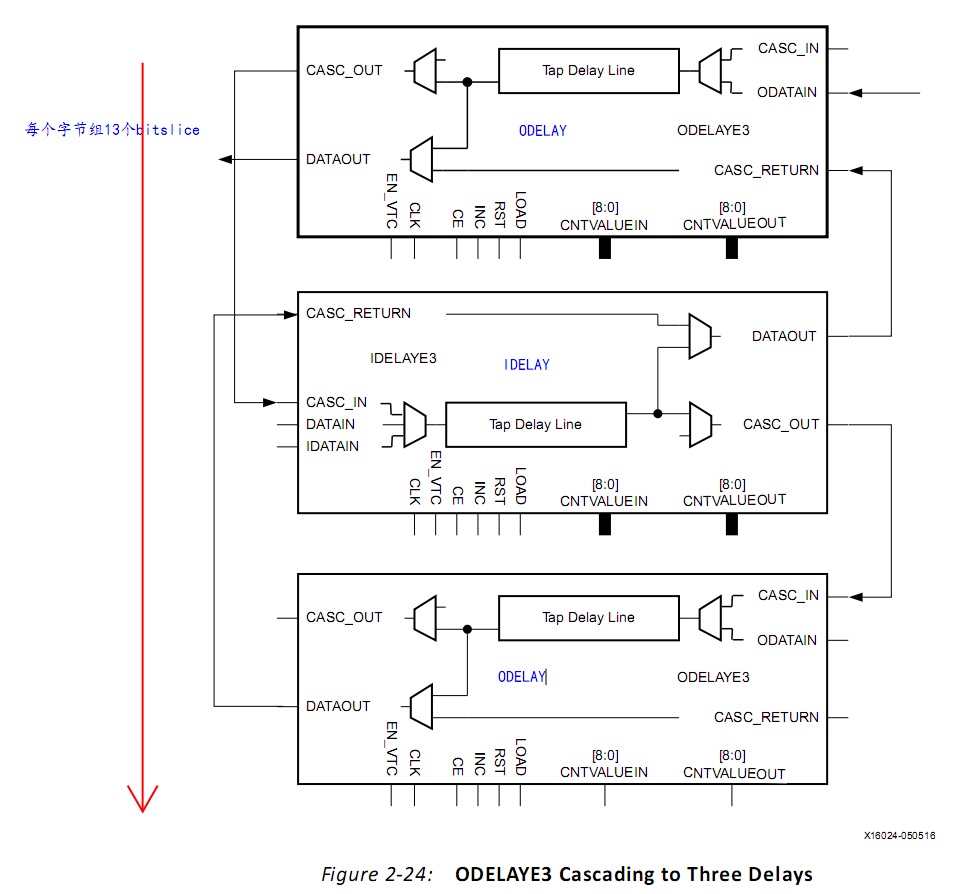

3、iodelay的级联

级联时只能向下个IO的iodelay级联,比如RXTX_BITSLICE_10只能向下级联RXTX_BITSLICE_9,不能向上级联_11。一个bitslice内部IDELAY在上,ODELAY在下 。同一个bitslice内部的Iodelay 延时值必须相同。IDELAY可以级联自己内部的ODELAY,ODELAY只能级联下一个bitslice中的IDELAY。级联时I + O穿插交替。

可以用XDC更改配置组件的级联属性(MASTER,NONE,SLAVE_END,SLAVE_MIDDLE)、延时值:

set_property CASCADE NONE [get_cells xxx]

set_property DELAY_VALUE 100 [get_cells xxx]

4、RGMII接口中2ns延时的添加位置

可以由发送方,也可以由接收方添加2ns延时,最终实现中心点采样。但添加位置的不同,影响FPGA的input/output约束值。

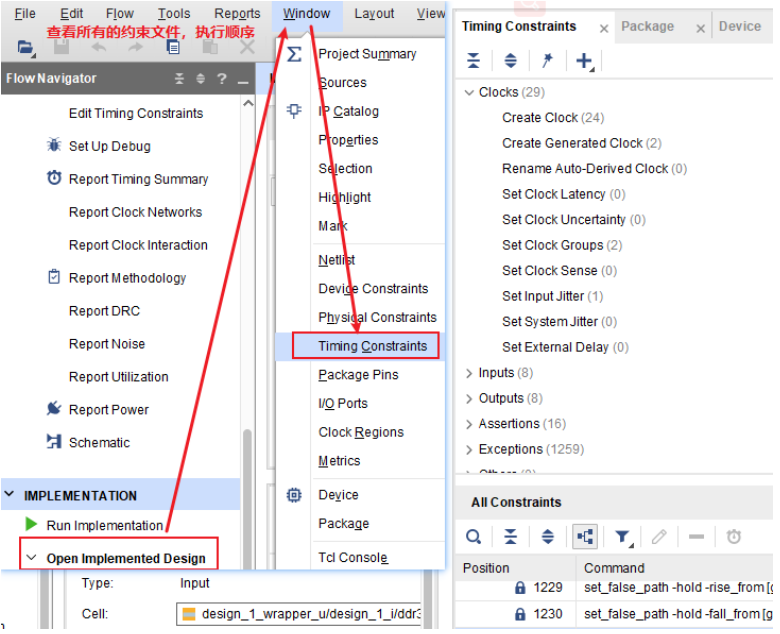

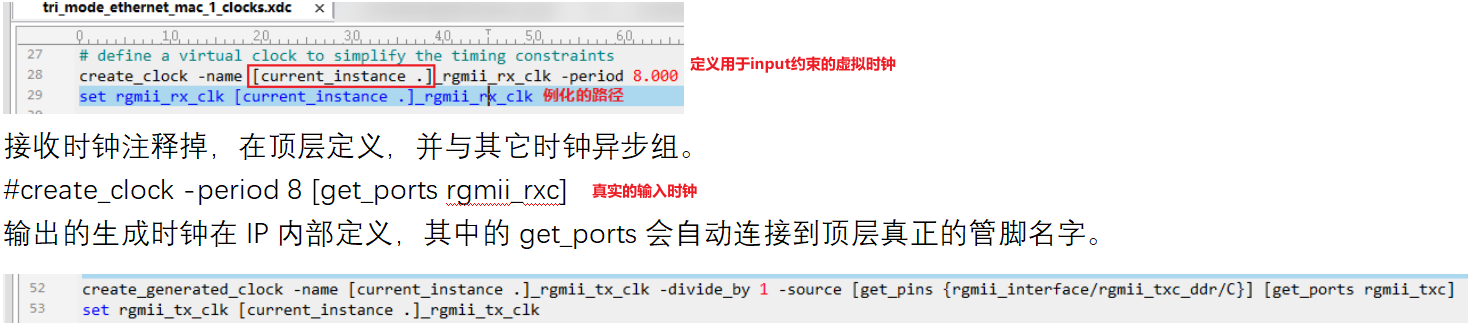

5、MAC IP内部约束文件中的port和pin

IP内部自带约束文件中的get_ports并非工程的IO=工程port,仅是指自己所在例化模块的IO=工程cell的pins。在约束文件的查看界面可以看到-scpoed_to_current_instance 。通常在顶层约束文件tcl指令中,port是指工程的IO,pin是指工程cell的IO。

某个IP自带约束文件中对时钟的约束: set ip_gtx_clk [get_clocks -of [get_ports gtx_clk]] ,get_ports仅指当前IP的顶层,在Vivado中Timing Constrains中查看工程所有的约束语句,可以找到该条语句被添加了在工程中的绝对路径。

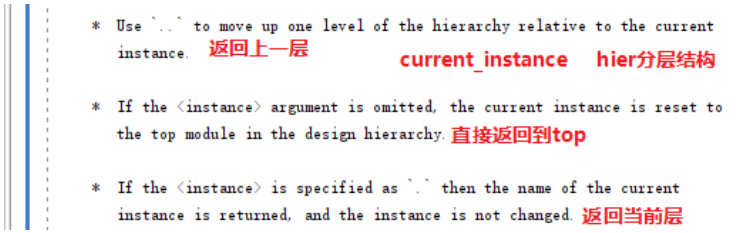

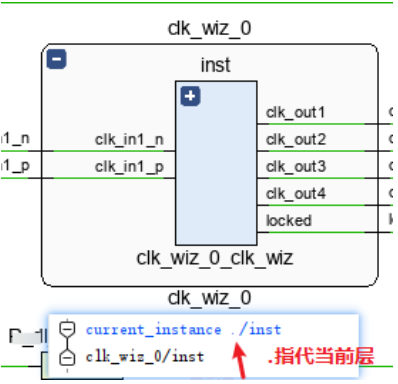

6、current_instance 调整层级

- current_instance A/B 进入A下的B层;

- current_instance . 返回当前层的名字B,层级不动。.指代当前层;

- current_instance .. 返回到上一层A;

- current_instance 返回到top层;

二、两个问题

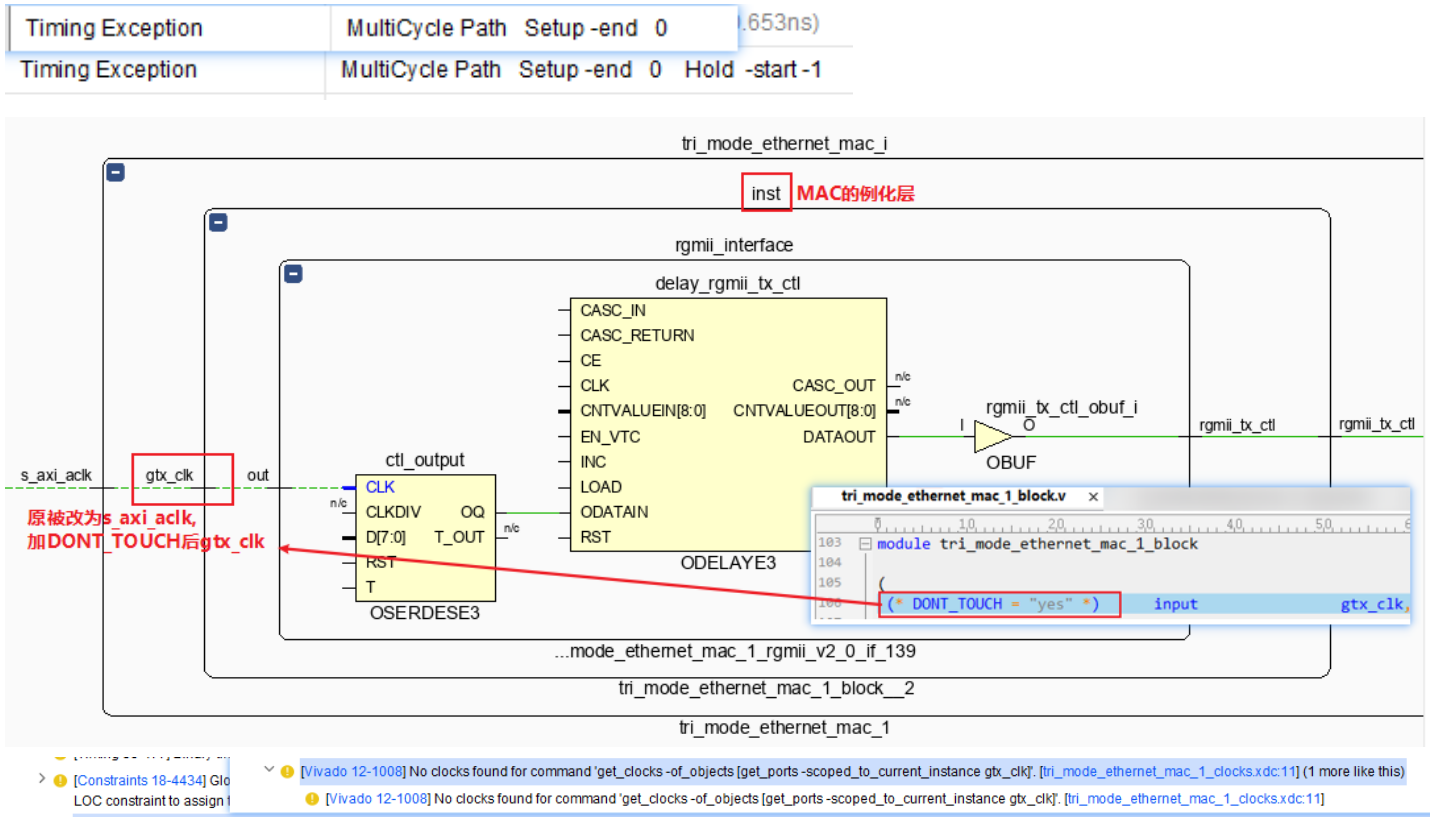

1、时钟约束未生效

大工程中的MAC IP内的set_false_path -setup -hold没有生效;set_multicycle_path 没有生效。原因:IP模块的顶层时钟接口名字被vivado更改,此处找不到端口了,也就找不到时钟,造成忽略所有相关的约束。

Vivado 12-1008\] No clocks found for command 'get_clocks -of_objects \[get_ports -scoped_to_current_instance gtx_clk\]'. \["f:xxx/tri_mode_ethernet_mac_3_ex.gen/sources_1/ip/tri_mode_ethernet_mac_1/synth/tri_mode_ethernet_mac_1_clocks.xdc":11

Designutils 20-1567\] Use of 'set_false_path' with '-hold' is not supported by synthesis. The constraint will not be passed to synthesis. \["f:/tri_mode_ethernet_mac_3_ex.gen/sources_1/ip/tri_mode_ethernet_mac_1/synth/tri_mode_ethernet_mac_1_clocks.xdc":42

Designutils 20-1567\] Use of 'set_multicycle_path' with '-hold' is not supported by synthesis. The constraint will not be passed to synthesis. \["f:/tri_mode_ethernet_mac_3_ex.gen/sources_1/ip/tri_mode_ethernet_mac_1/synth/tri_mode_ethernet_mac_1_clocks.xdc":46

通过增加DONT_TOUCH指令,禁止vivado在综合时改变信号的名字,保证约束中的名字有效

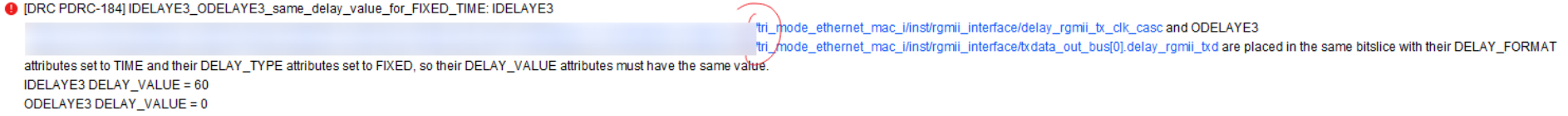

2、设置O+I 延时值总是报错

虽然BITSLICE_67 中ODELAY=BITSLICE_66 中IDELAY,符合延时级联时所有级均分延时值的要求 ,但不满足同一个BITSLCE中的两个I、Odelay延时值须相同。

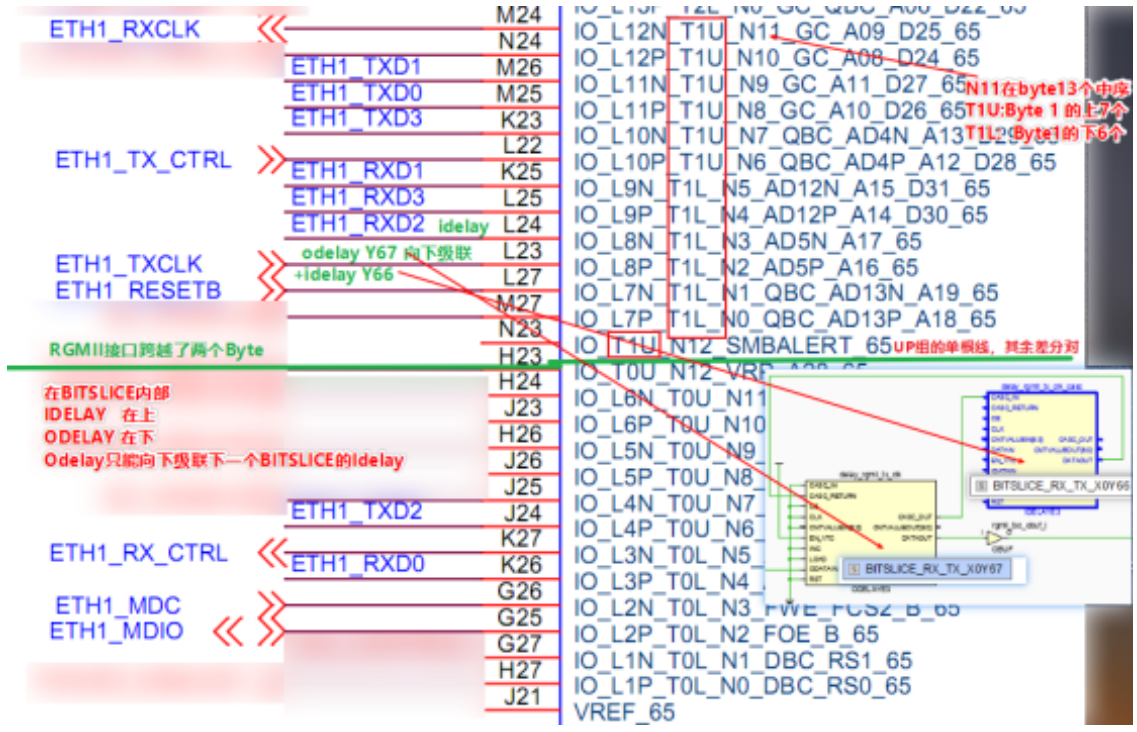

以下错误出现在下面的原理图中,提示同一个BITSLICE内的IDELAY和ODELAY的值不相同。

图中L23的管脚在设计中使用了两级联的输出延时,BITSLICE_67中ODELAY=60+ BITSLICE_66 中IDELAY=60 ,而 BITSLICE_66 中ODELAY=0 被用于自身L27管脚的延时。如此存在 BITSLICE_66 中IDELAY≠ODELAY,故Vivado会报错。

3、接收时钟的BUFGCE被软件放置的很远

使用LOC约束BUFG的位置

set_property LOC BUFGCTRL_XxYy [get_cells BUFG_instance_name]