文章目录

- [0 前言](#0 前言)

- [1 设计信息](#1 设计信息)

-

- [1.1 设计需求](#1.1 设计需求)

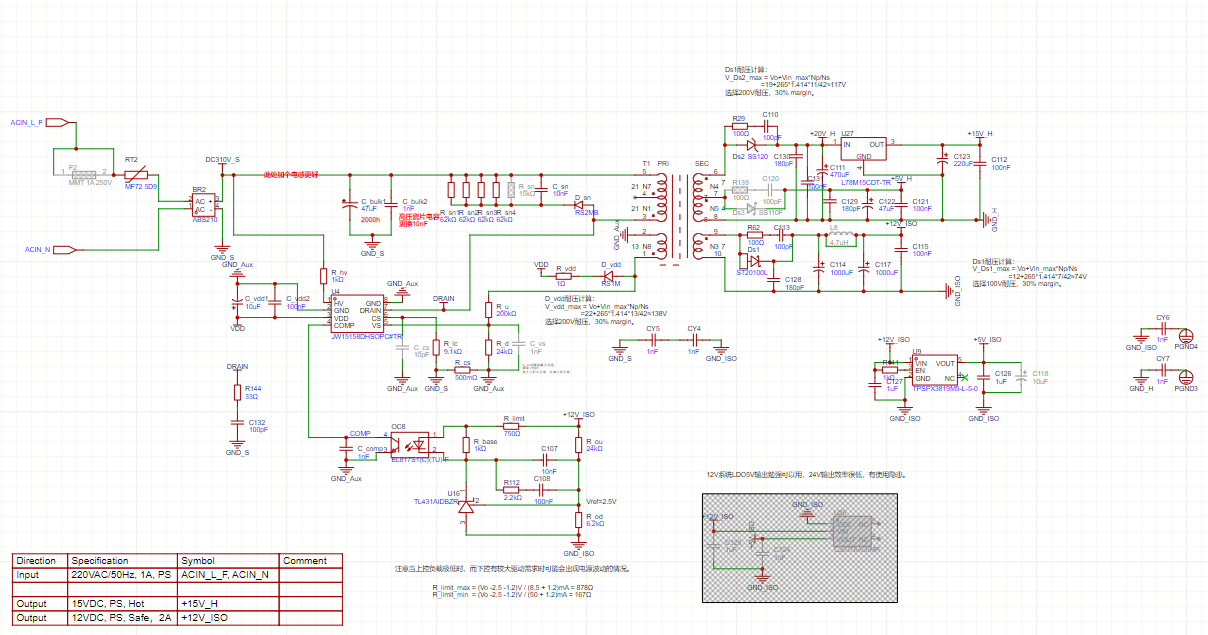

- [1.2 原理图](#1.2 原理图)

- [1.3 电源表现](#1.3 电源表现)

- [2 原因分析](#2 原因分析)

- [3 横向对比](#3 横向对比)

-

- [TI UCG28826 (GaN)](#TI UCG28826 (GaN))

- 采购的普通QR反激变换器

- [4 总结](#4 总结)

0 前言

笔者原计划设计一款省电的,效率尚可的,稳定的2路输出反激电源,用于系统供电。选定JW15158B作为反激控制器。

设计出来的电源带载能力尚可,但输出端受到开关噪声影响,始终存在与原边同步的开关尖峰,尝试多种方式无果。

1 设计信息

1.1 设计需求

输入:85~265VAC

输出:12V2.5A + 15V1.0A 双路输出,峰峰值要求<±150mV。

1.2 原理图

有需要的读者请私信笔者。

1.3 电源表现

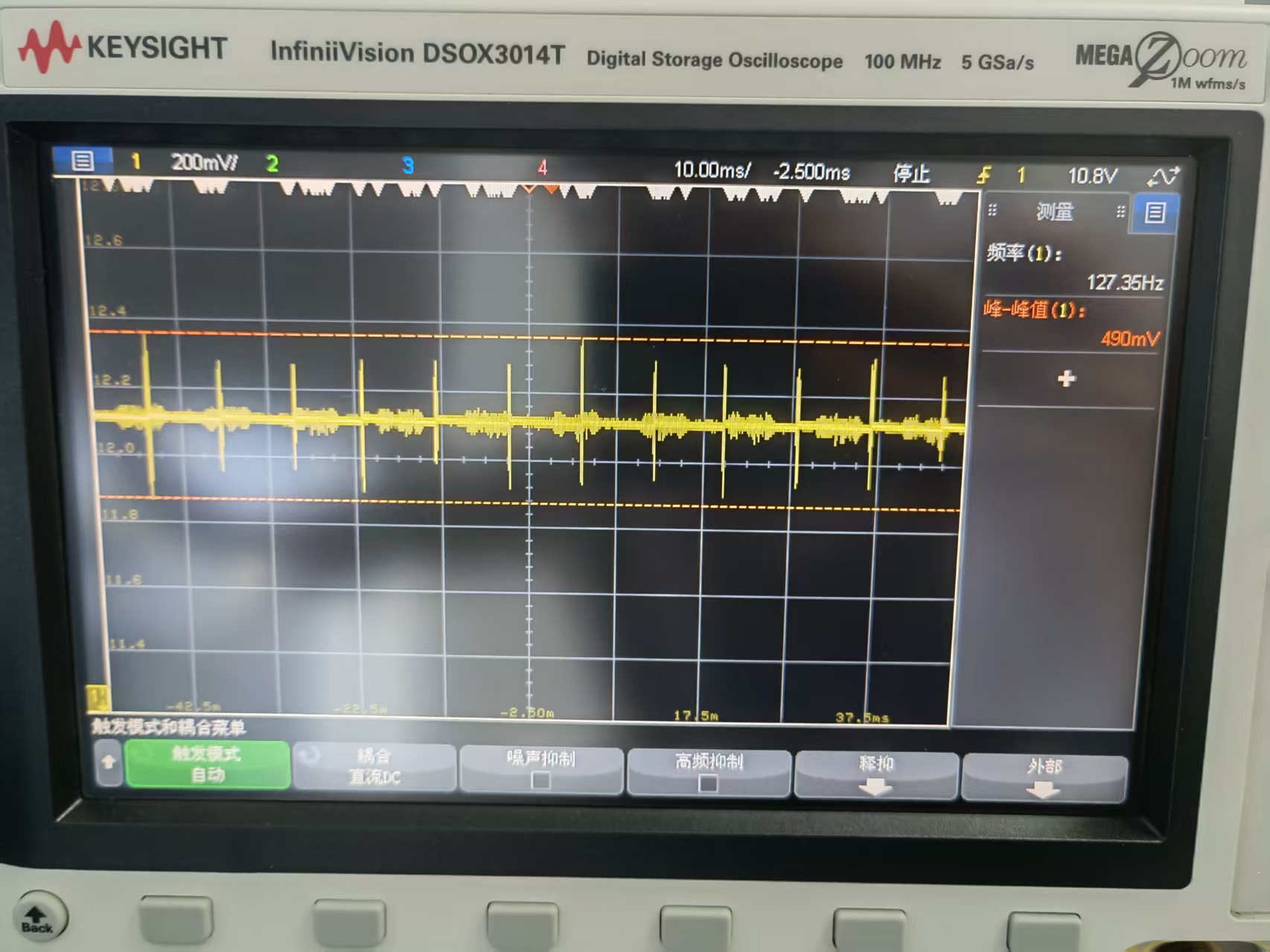

示波器接线非严格按纹波测量要求测试

空载(注意时间分辨率):

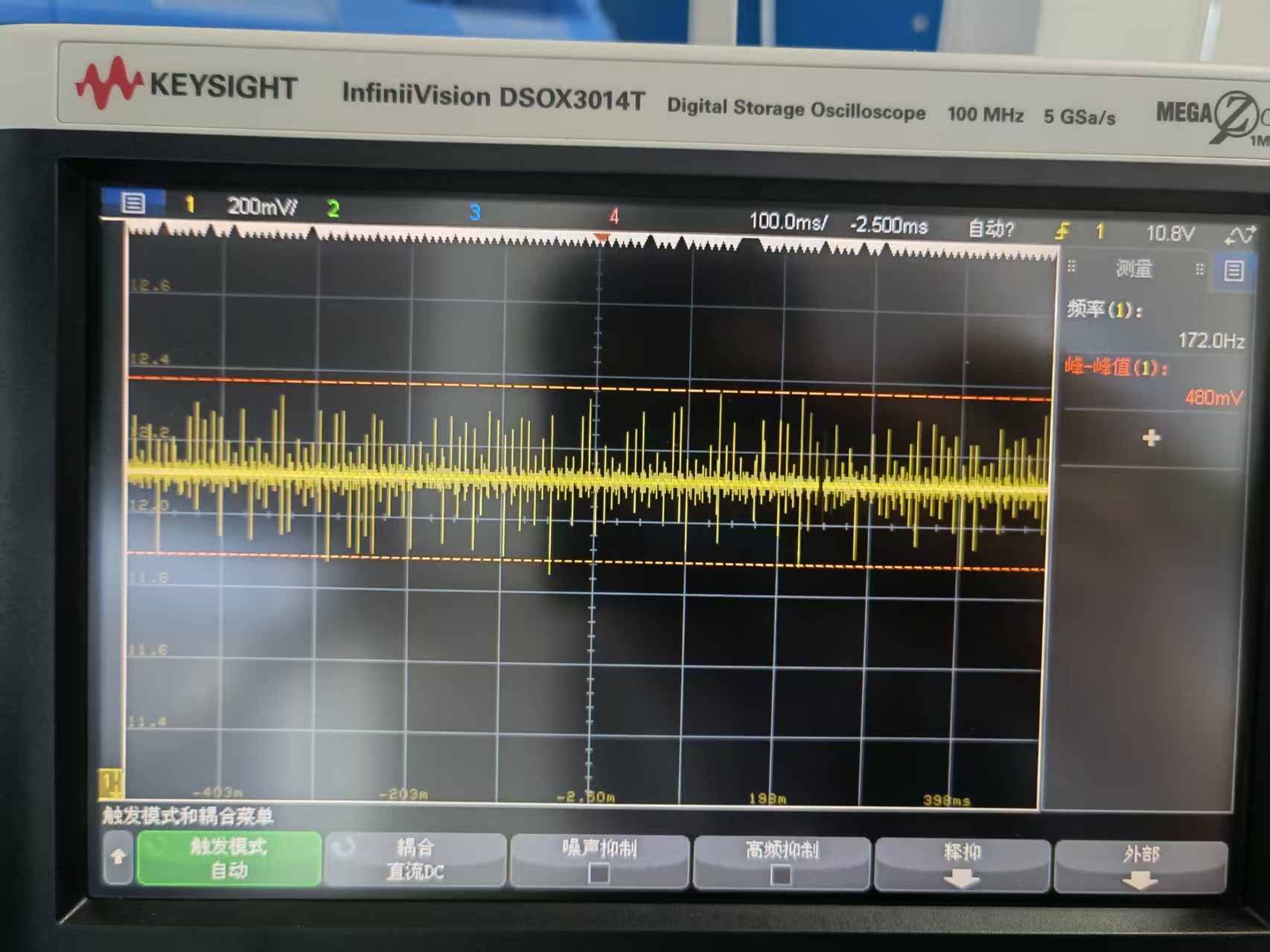

带载(12V1.6A)

尝试很多调整方式都无法将开关噪声抑制到目标要求,包括但不限于如下方法:

环路优化、RCD参数调整、输出滤波、输出RC吸收电路参数调整、初次级Y电容参数调整、变压器调整(470uH,漏感<10uH)。

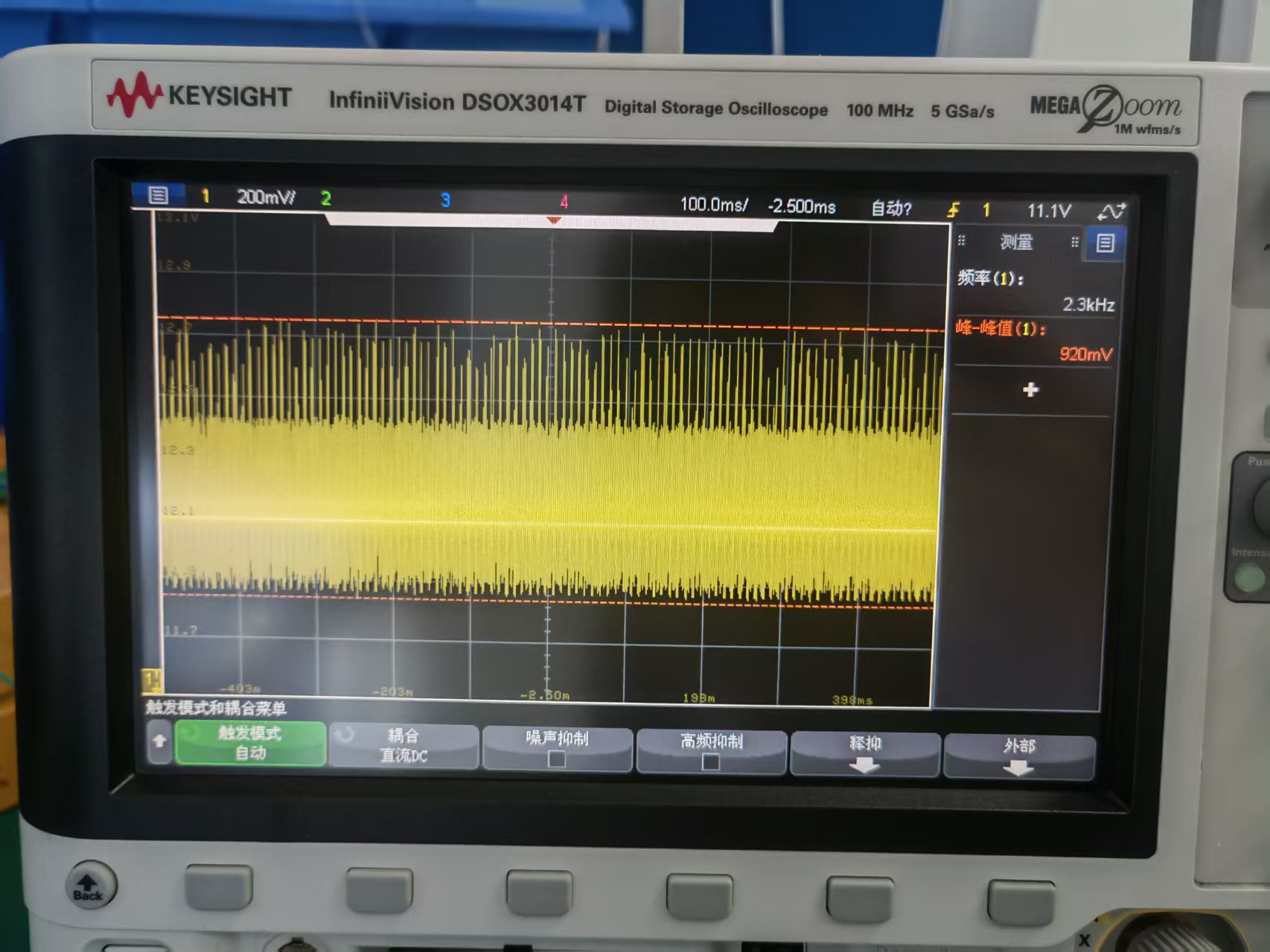

探头按纹波测试方式接线

!!!!!!

空载电压峰峰值260mV,12V1A带载时峰峰值340mV。

!!!!!!

2 原因分析

理论上来说,GaN的开关频率比MOSFET的要高,可以做到更优秀的输出纹波。难道是dv/dt变大的原因导致输出受到更大的噪声干扰?

还没找到更好的解决方案。路过大神多多指点。

3 横向对比

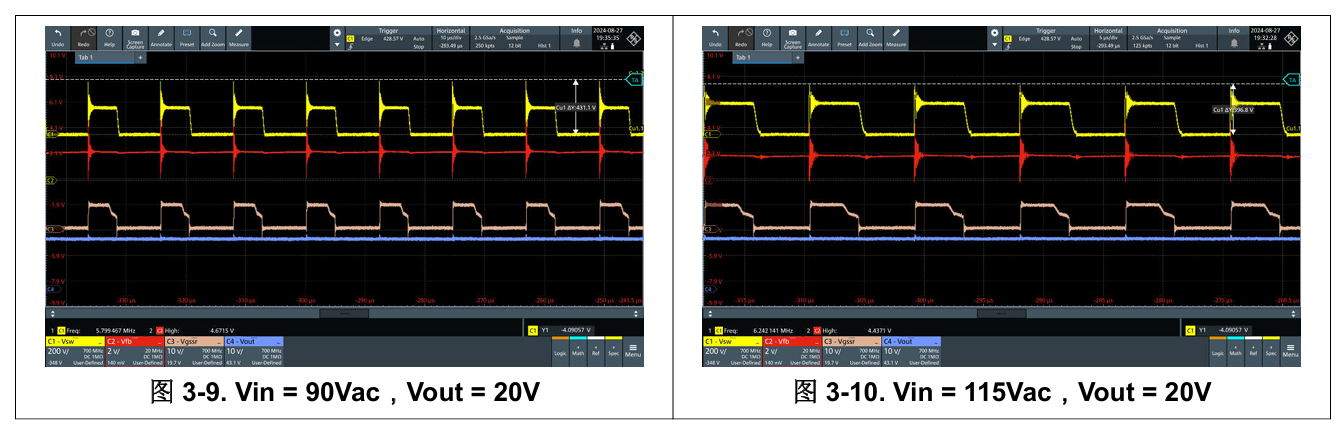

TI UCG28826 (GaN)

链接: UCG28826

链接: EVM User's Guide: UCG28826EVM-093

从评估板测试报告中可以找到如下图示。由于分辨率是10V/格,不能很好的分析输出电压波动情况,我用卡尺量了一下每格高度和输出电压的峰峰值,结果发现20V输出居然有3V的峰峰值 !

也查了一下其他家GaN的反激控制器,其应用领域都是在USD PD充电上。猜想是不是这个应用场景对于电压的稳定性要求没有那么高。

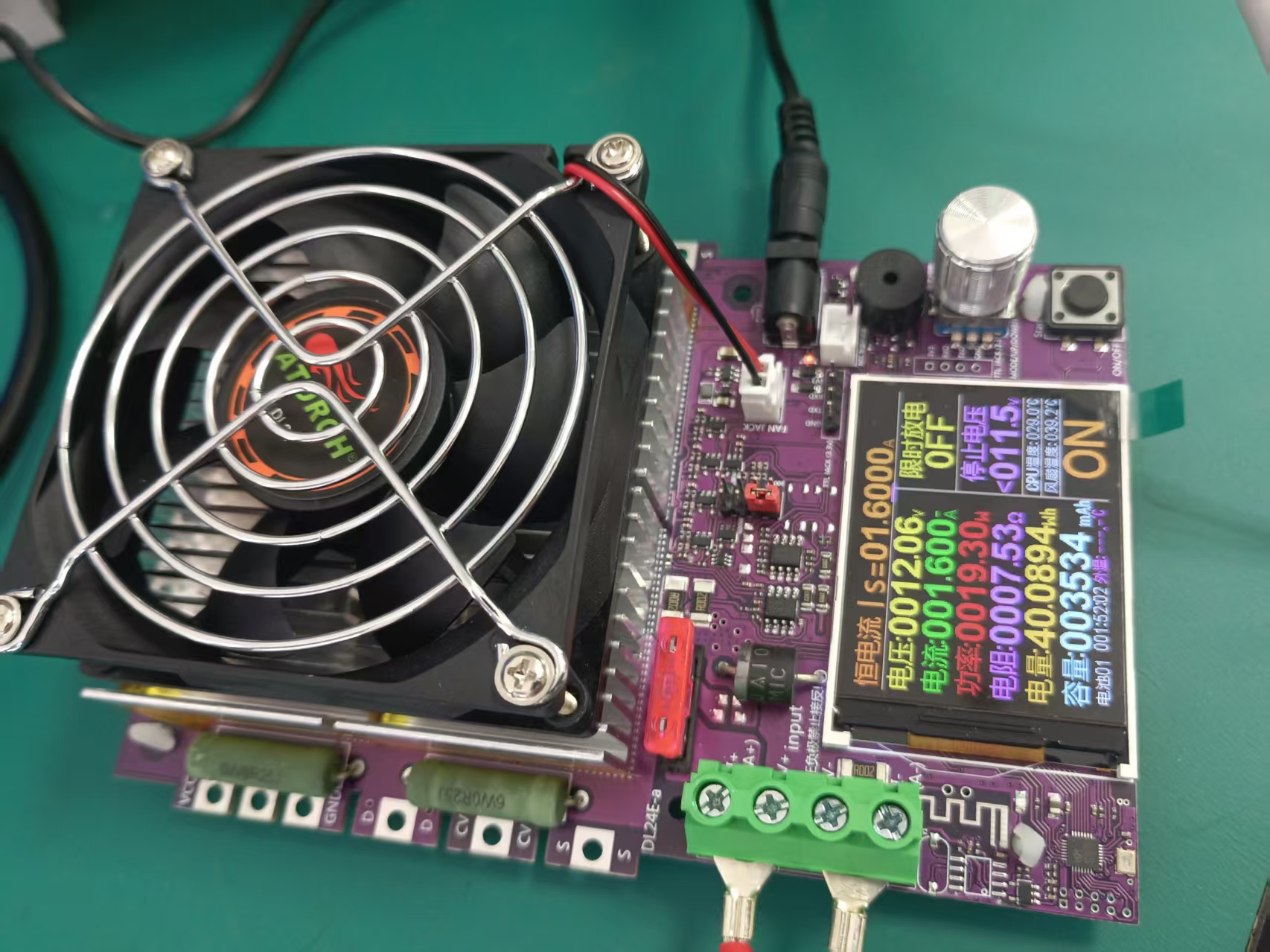

采购的普通QR反激变换器

输出峰峰值可以做到200mV。也是非严格测量方式接线测量。说明去除测量手法的影响,还有改进空间。

4 总结

问题还没解决,同志还须努力。