一、基础知识

1、fpga的约束文件为.fdc,synopsys的约束文件为.sdc。想通过fpga验证soc设计是否正确,可以通过syn工具(synplify)吃.fdc把soc code 转换成netlist。然后vivado P&R工具通过吃上述netlist、XDC 出pin脚约束、fdc时序约束三个约束来完成P&R的布局布线任务。

2、.fdc约束文件中标记的含义:

c:代表clk

n:代表net

p:代表port

t:代表pin

i:代表cell

3、.fdc中若没有把clk定义到group中会默认是异步时钟,而.sdc则是没指定clk到某个group中,会默认为同步时钟。

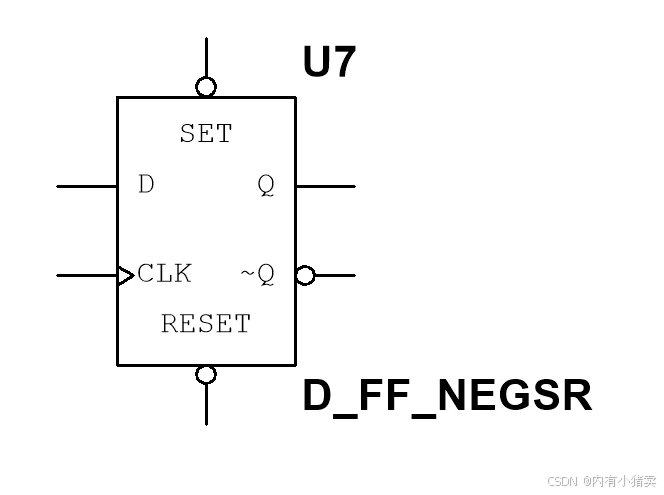

4、时序报告中type下的FDC代表带异步清零(clear)的DFF。

5、get_pins get_cells 区别

该DFF一般有两类路径(在不考虑input port -> DFF 或 DFF -> output port路径时):

(1)其他DFF的CK端到该DFF的D端

(2)该DFF的CK端到其他DFF的D端

注意:有时工具会把Q端 认为是CK端,指的路径一样就是叫法不同。

get_pins 会指定某个pin脚的时序路径,表示(1)或(2)的其中一个,如以D端为ending或以Q端为start的一类时序路径

get_cells 会指定该DFF的所有时序路径,表示(1)(2)的所有路径。