引言:上一节我们讲到了使用Alinx 7020b自带的sd卡中的petalinux进行epics的编译,但此种方案个性化程度不足。如:我们项目需要FPGA侧的配合,那么我们需要重新编译petalinx。

注意:本文的知识点来自下面两篇文章,我已经假设大家对petalinux有了一定的了解。

FPGA----ZCU106使用petalinux 2019.1(全网最详)-CSDN博客文章浏览阅读3.5k次,点赞18次,收藏31次。本文完成了Vivado 2019.1版本下的基于ZCU106的全部linux系统移植https://blog.csdn.net/qq_37912811/article/details/134519735FPGA----基于ZYNQ 7020实现EPICS通信系统-CSDN博客文章浏览阅读966次,点赞9次,收藏23次。本文详细介绍了如何在EPICS(ExperimentalPhysicsandIndustrialControlSystem)环境中创建一个IOC(Input/OutputController),编写aiRecord的驱动程序,包括dbd文件和C语言源代码,然后编译并启动IOC,最后通过通道访问查看运行结果,实现每秒生成0-999随机数的功能。

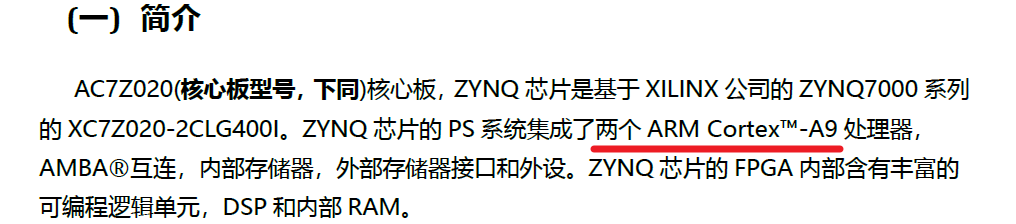

https://blog.csdn.net/qq_37912811/article/details/1471689801、本文软硬件:AX7Z020b、Vivado 2019.1、Ubuntu 18.04.1、make 3.81

这些配置在我先前的文章都可以找到下载地址。

2、在sdk中找到导出的.hdf文件

3、创建ax_peta工程

bash

# 创建ax_peta工程

petalinux-create --type project --template zynq --name ax_peta

# 创建hardware文件夹,将xxx.hdf文件(在vivado中launch sdk生成的)存入

mkdir harware

# 进入工程

cd ax_peta

# 配置工程

petalinux-config --get-hw-description ../hardware

# 依据我之前的博客配置即可

# 配置内核,默认配置保存并退出即可

petalinux-config -c kernel

# 配置根文件系统,默认配置保存并退出即可

petalinux-config -c rootfs4、编译工程,并导出文件

bash

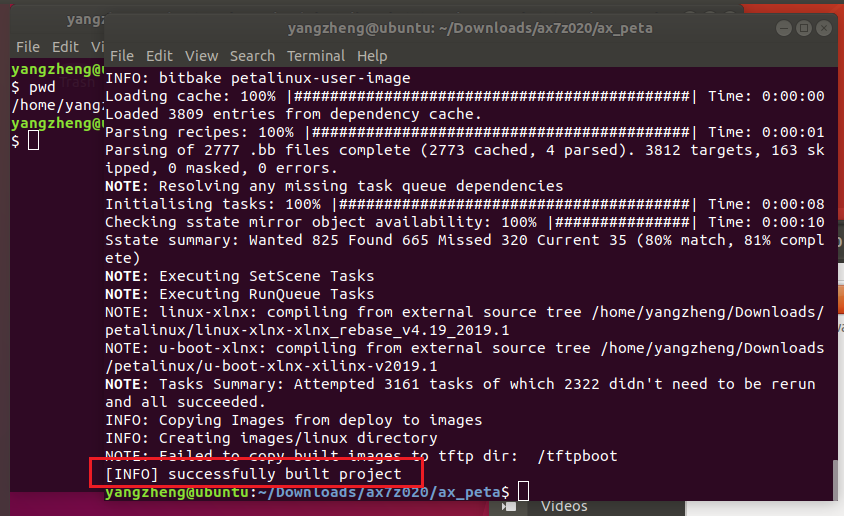

petalinux-build

# 如果提示需要配置权限,那么就输入下述命令

sudo chmod -R 777 linux-xlnx-xlnx_rebase_v4.19_2019.1/

sudo chmod -R 777 linux-xlnx-xlnx_rebase_v4.19_2019.1/scripts/

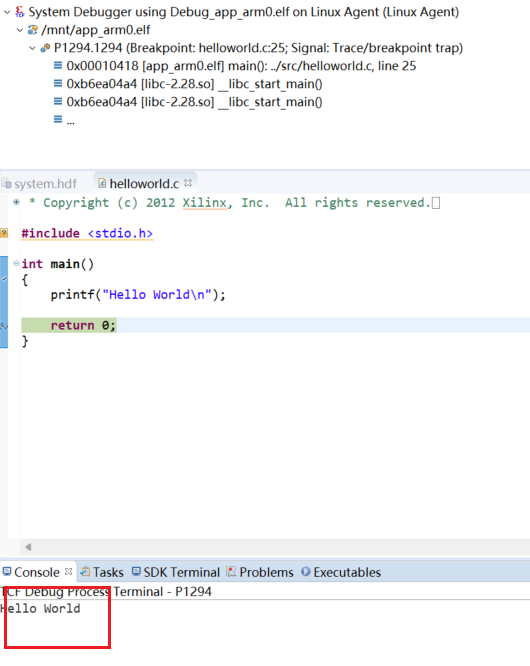

出现下图就是编译好了

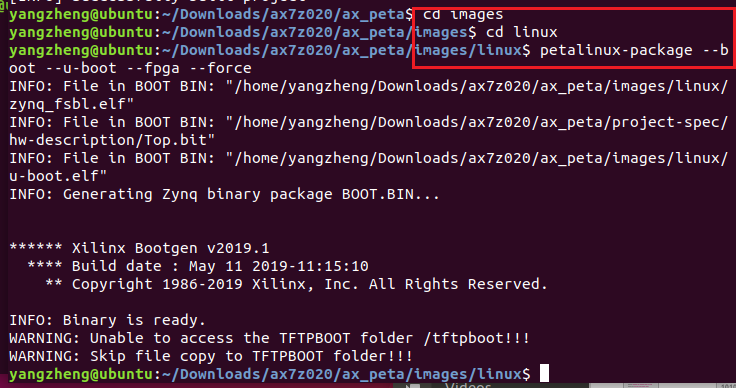

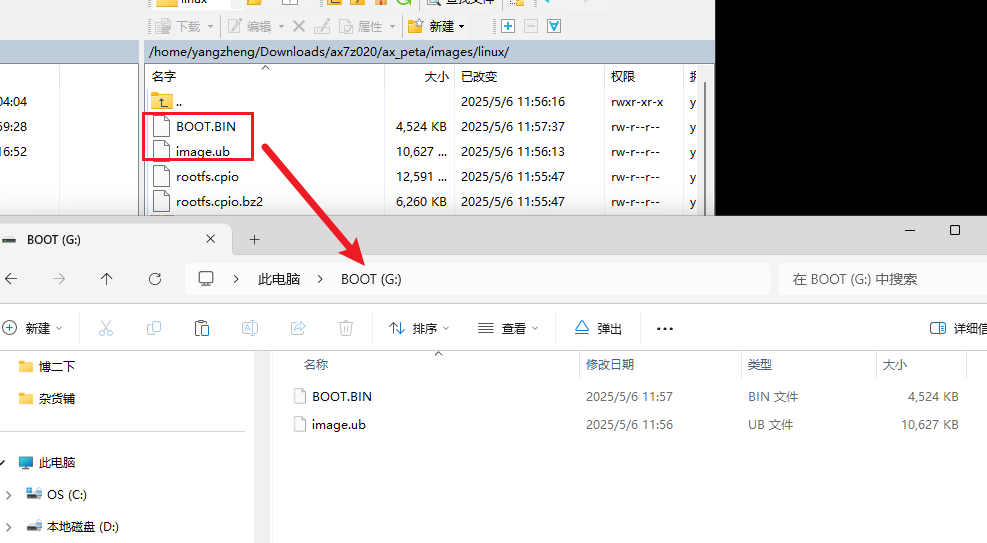

5、进入到images/linux生成image.ub文件

bash

# 进入文件夹

cd images/linux

# 生成imag.ub

petalinux-package --boot --u-boot --fpga --force

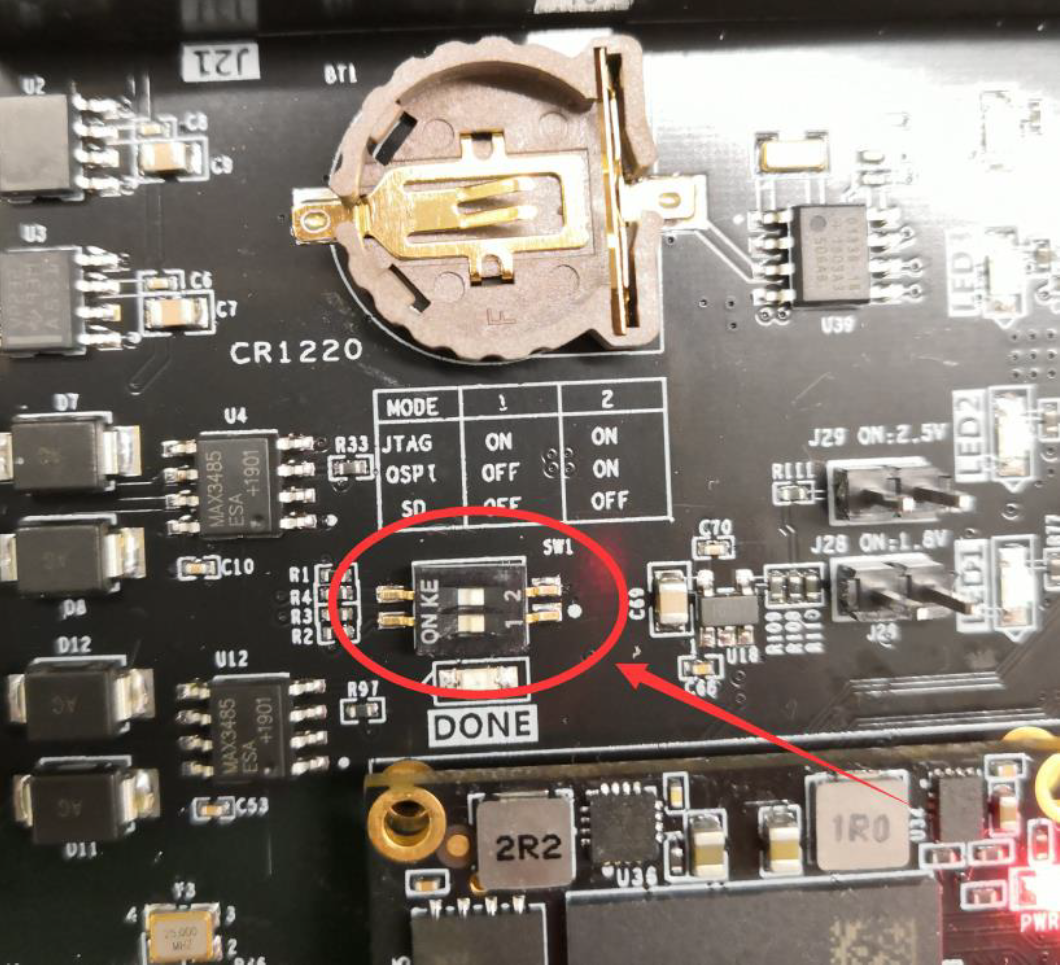

6、将7020设置为sd卡启动方式,正常买回来就是sd卡启动,挨着12就是sd卡启动了

3种启动方式MODE在图中白色表格有写。

7、格式化SD卡,将BOOT.bin与image.ub移动到SD卡中,上电启动。

7、登录的用户名为:root,密码为:root

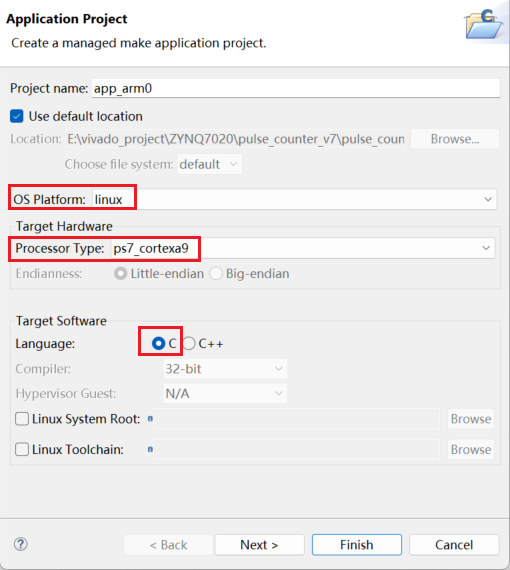

8、编写一个linux程序

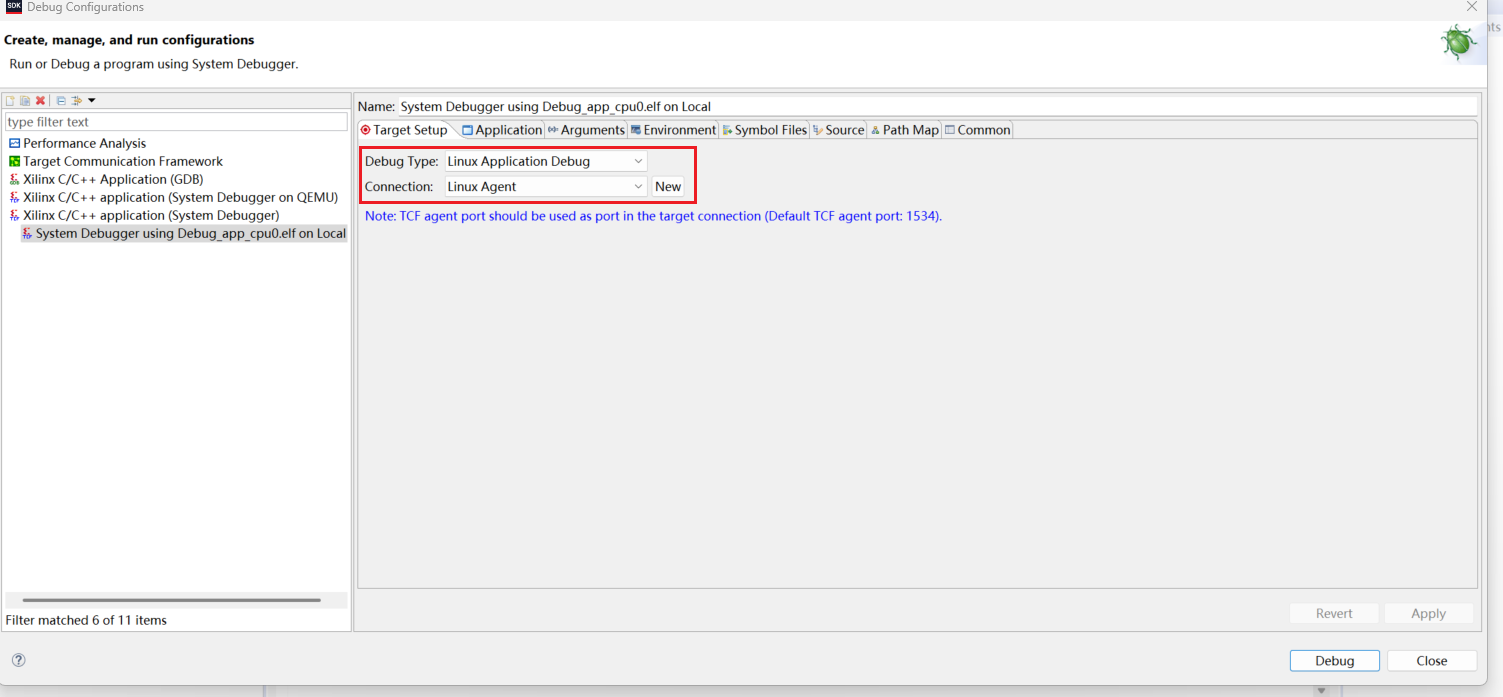

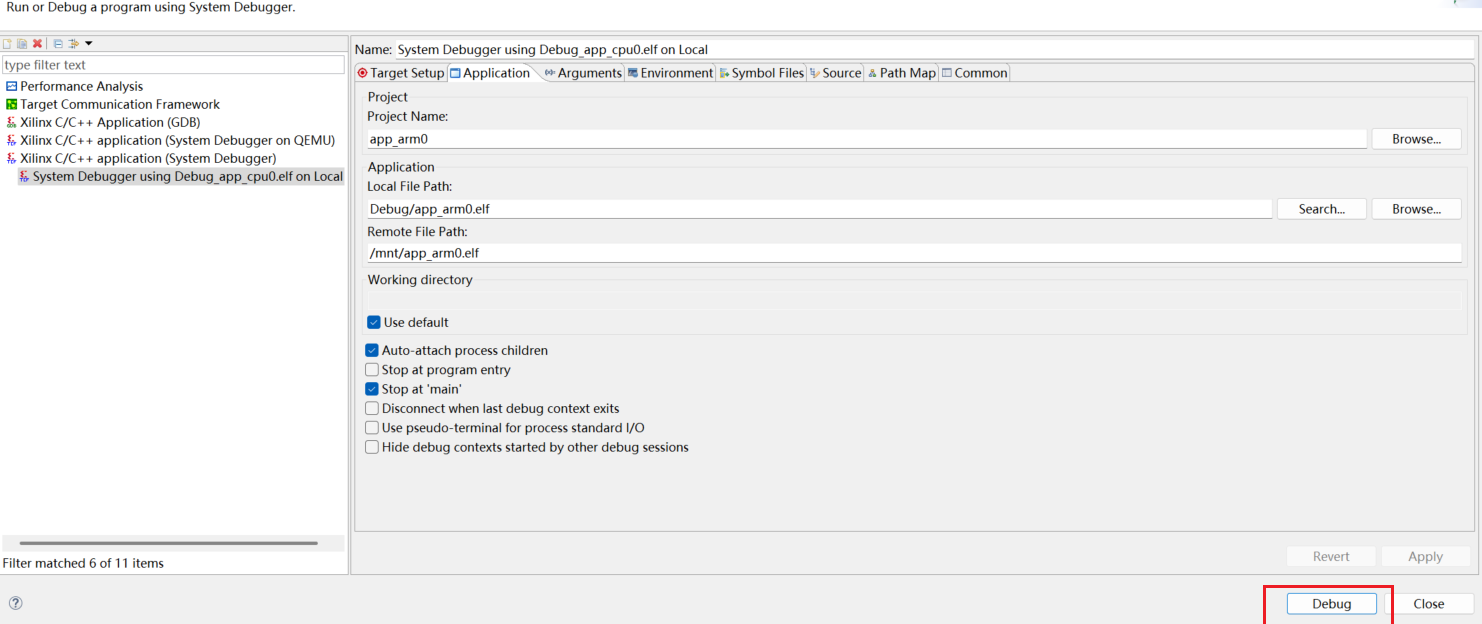

平台选linux,处理器选A9,语言选C,因为咱们没有装C++的标准库。

(2)通过命令配置zynq的ip

bash

# 查询网络接口

ls /sys/class/net

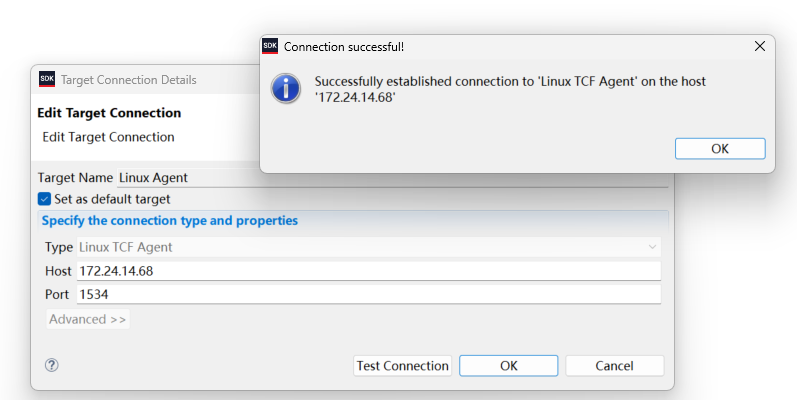

# 保证172.24.14.68与上位机是同一网段,上位机ping即可

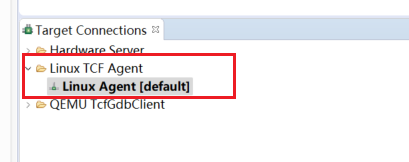

ifconfig eth0 172.24.14.68 netmask 255.255.255.0 up右下角设置Linux代理

(3)启动程序

出现下面结果就是运行成功了